文章链接:https://www.nature.com/articles/s41565-024-01705-2

文章链接:https://www.nature.com/articles/s41565-024-01705-2

近日,宾夕法尼亚州立大学Saptarshi Das教授团队探讨了基于双极性半导体WSe2单片三维集成互补二维场效应晶体管的前沿技术,研究成果发表在Nature Nanotechnology上。

两天前公众号分享了一篇基于N型半导体MoS2和P型半导体WSe2的大面积单片3D集成方案(2024,Small),两者的集成方案和有相似之处。对比之下,也可以发现这篇文章的优势在于单一半导体材料,且集成度和功能性更强。

摘要

半导体行业正在向“More Moore”时代过渡,通过采用三维集成方案来超越传统二维缩放的限制。尽管创新的封装解决方案使三维集成电路(IC)在商业上变得可行,但硅通孔和微凸点的使用增加了面积开销并引入了寄生电容,限制了整体性能。单片三维集成(M3D)被认为是三维IC的未来,但其在硅IC中的应用面临着上层热处理预算有限的问题,这可能会降低器件性能。为了克服这些限制,新兴材料如碳纳米管和二维半导体已经被集成到硅IC的后端。在这项研究中,我们报道了互补WSe2场效应晶体管的M3D集成,其中n型FET位于第1层,p型FET位于第2层。特别是,我们通过300纳米的通孔实现了密集且缩放的集成,其间距小于1微米,连接了第1层和第2层的300多个器件。此外,我们有效地实现了垂直集成的逻辑门,包括反相器、NAND门和NOR门。我们的演示突出了二维材料在推进互补金属氧化物半导体电路M3D集成中的作用。

研究背景和主要研究内容

六十年来,人们不断通过缩小晶体管尺寸来追求“More Moore”,而这得益于器件架构的创新,例如鳍式场效应晶体管 (FET) 技术的开发 、高κ电介质的集成、互连的改进以及极紫外光刻技术的进步。这些创新一直促进着集成电路 (IC) 元件密度的提高。有趣的是,尽管器件级的缩小令人惊叹,但它远远超过了封装级的进步。这凸显了三维 (3D) 集成的重要性——一种“正交缩放”方法,它为提高器件集成密度提供了一种有前景的策略,并有效地解决了传统器件尺寸缩放固有的限制 。与传统平面几何相比,3D 集成具有许多优势,包括占用空间更小、功耗更低、带宽更高、连接布线更短以及互连寄生损耗更低。此外,它还实现了各种元素(如存储器和图像传感器)的异构堆叠,这一概念被称为“超越摩尔”技术。

3D 集成的工业方法利用铜微凸块和硅通孔 (TSV) 来堆叠单独制造的芯片。然而,TSV 占用空间很大,会导致相当大的寄生电容和热/机械应力。单片 3D ( M3D ) 集成通过在单个芯片上顺序制造层间通孔来解决这些限制。这种方法可以提高垂直互连密度、缩短线长(实现更高的速度和更低的功率损耗)并实现晶体管级分区。M3D集成还允许在一个或多个层中加入非硅材料,以增强性能或丰富功能。最近,M3D 集成已经加入了低维材料,如碳纳米管和过渡金属二硫属化合物( TMDC ) 。然而,由于 n 型碳纳米管 FET 和 p 型二维 (2D) FET 的开发进展有限,因此 M3D 与来自相同 (非硅) 半导体材料的互补 FET 的集成仍未得到充分探索。尽管 n 型 MoS2与 p 型 MoTe2 (参考文献22 ) 和 n 型 MoS2

与 p 型 WSe2 (参考文献23 ) 的 3D 堆叠演示标志着互补 FET 的 M3D 集成向前迈出了一步,但由于器件和通孔尺寸都相对较大,其全部潜力仍未得到充分开发。

在本研究中,我们展示了基于 n 型和 p 型场效应晶体管的两层互补金属氧化物半导体 (CMOS) 芯片的 M3D 集成,这些场效应晶体管由通过金属有机化学气相沉积 (MOCVD) 技术合成的大面积 WSe2制成。我们还实现了晶体管级分区,在第一层上放置了 340 个 n 型场效应晶体管,在第二层上放置了 340 个 p 型场效应晶体管。这项研究的一个重要里程碑是展示了一种密集集成的层间通孔,其宽度为 300 nm,间距为 1 µm,可与最先进的封装解决方案相媲美 。此外,还成功实现了包括 27 个反相器、12 个 NAND 门和 12 个 NOR 门在内的 3D CMOS 电路。此外,M3D CMOS 堆栈的制造温度不超过 200°C,使其适合在混合 2D/Si 技术的后端生产线集成。

WSe2薄膜的合成及互补 2D FET 的实现

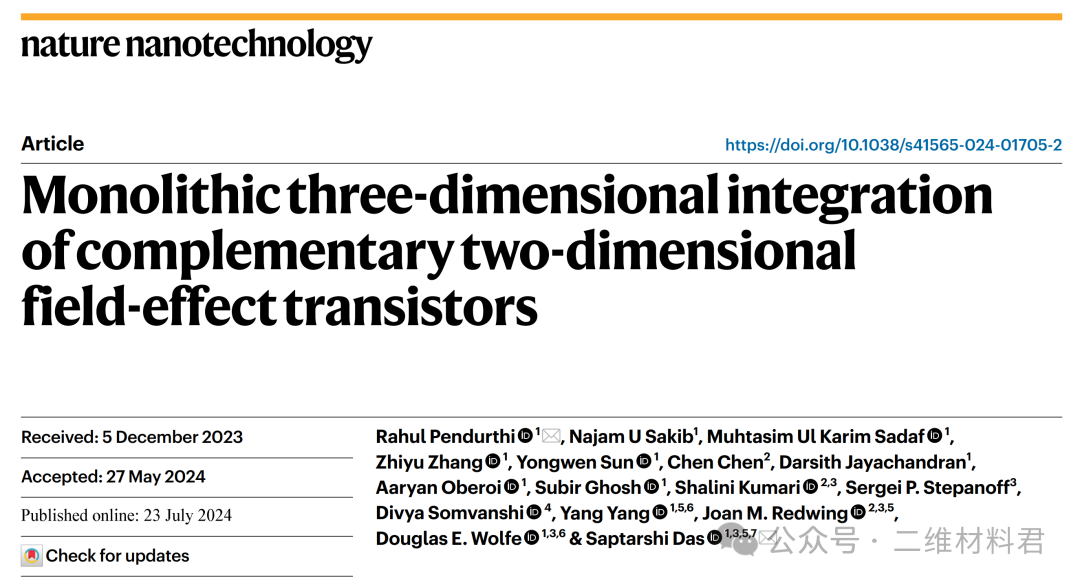

图1a显示了基于 WSe2 FET的 M3D 集成两层 CMOS IC 组成的阵列的光学图像。阵列中的每个单元(图1b)包含四个器件,其中两个 p-FET WSe2 FET 直接位于两个 n-FET WSe2 FET 上方。图1c显示了两级 CMOS 反相电路的倾斜假色扫描电子显微镜 (SEM) 图像。在此配置中,300 nm 通孔彼此相距 1 µm 以内,以形成一级 n-FET 和二级 p-FET 器件之间的串联连接,突出显示了这项工作中实现的密集通孔集成能力。图1d、e分别显示了 M3D 集成 NAND 门的示意图和相应的假色 SEM 图像。图1f-h显示了 M3D 堆栈的高角度环形暗场 (HAADF) 扫描透射电子显微镜 (STEM) 图像和能量色散 X 射线光谱 (EDS) 元素映射,拍摄于图1e中红色虚线指示的横截面。

图 1:CMOS WSe2 FET 的 M3D 集成。a 、基于 WSe2 FET的 M3D 集成双层 CMOS 电路的光学图像。b、在此配置中,每个单元包含四个器件。这里,两个 p-FET 器件直接位于两个 n-FET 器件的顶部。c 、双层单元的成角度的假彩色 SEM,对应于两级反相电路。具体而言,这项工作中实现的通孔宽度和间距分别为 300 nm 和 1 µm。d 、e、M3D 集成 CMOS NAND 电路的示意图 ( d ),以及相关的假彩色 SEM 图像 ( e )。互连和通孔已标记,突出显示了通过 M3D 集成获得的密集连接。f 、 HAADF-STEM 图像显示 3D NAND 电路的横截面,取自 ( e )中的红色虚线。在f中应用了垂直伸长以更好地显示特征。g

、h,一级 ( g ) 和二级 ( h ) WSe2器件的放大 HAADF-STEM 和 EDS 元素映射。( g ) 和 ( h )的比例尺为20 纳米。

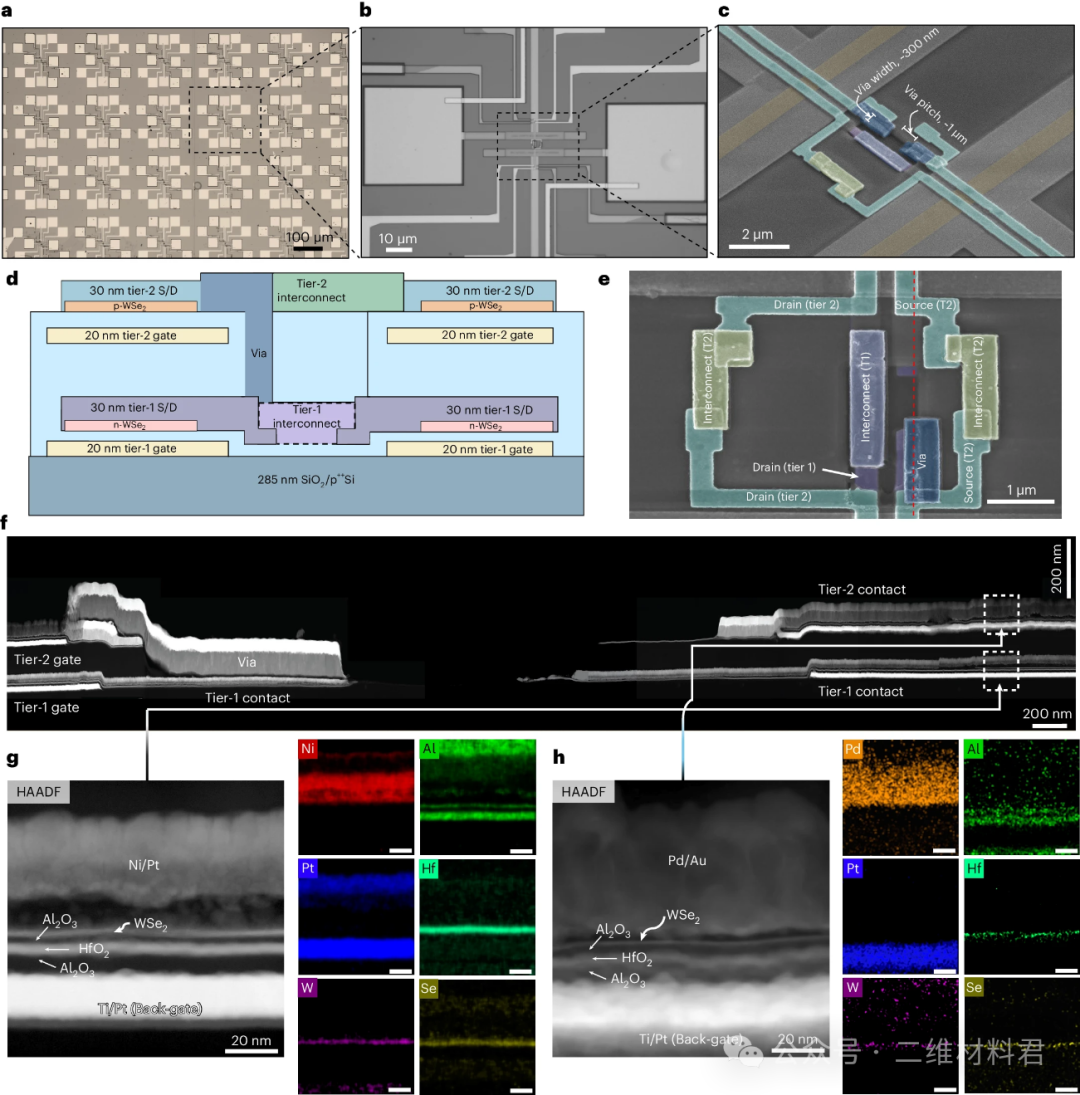

为了实现基于 2D FET 的 M3D 集成 CMOS 芯片,需要大面积合成目标 2D 沟道材料。本研究中使用的多层(三到四层)WSe2薄膜是使用 MOCVD 系统生长的。有关生长条件和合成参数的更多详细信息在方法中概述。图2a展示了两英寸宽的多层 WSe2生长的光学图像。通过原子力显微镜(图2b)证实了多层的形成,显示出融合的三/四层薄膜和一些多层岛。额外的 HAADF-STEM 成像(图2c )显示了 WSe2薄膜的晶体 2H 结构。从晶圆上的十个不同区域捕获的光致发光 (PL) 光谱(图2d)表明平均峰值位置约为 1.64 eV,进一步证实了多层生长。最后,图2e展示了从相同位置收集的拉曼光谱。

a 、使用 MOCVD 技术生长的两英寸多层 (ML) WSe2的光学图像。b、晶圆中心的ML-WSe2的原子力显微镜图像。在聚结的薄膜上可以观察到多层岛状结构。c 、从c轴拍摄的ML-WSe2的 HAADF-STEM 图像,显示了原生薄膜的原子结构。d 、 WSe2薄膜的 PL 光谱。发现峰值位置为 ~1.65 eV,与多层 WSe2相关。e 、WSe2薄膜的拉曼光谱,由249 cm –1处的特征平面内E2g峰和 258 cm –1处的非平面 2LA(M) 峰组成。拉曼光谱和 PL 光谱均在两英寸 WSe2晶片上的十个点处采集。

接下来,使用聚甲基丙烯酸甲酯 (PMMA) 辅助湿转移技术 (方法) 将 WSe

2薄膜从蓝宝石衬底转移到器件制造衬底,以评估电气性能。使用拉曼光谱确认转移后薄膜的均匀性,结果在补充第1节中介绍。使用 WSe2薄膜实现 CMOS 功能的关键步骤是选择层厚度、接触金属和层间电介质 (ILD) 材料。选择多层 (三到四层) WSe2薄膜是因为它在环境条件下稳定、性能高、易于大面积合成,最重要的是,能够实现双极导电,同时保持相对较大的开/关电流比 >10 4 。这些特性使 CMOS 功能成为可能,并实现低静态功耗,这与使用单极二维材料(如 MoS2 )的基于 n 沟道金属氧化物半导体的逻辑形成鲜明对比。扩展数据图1a、b显示了传输特性,即漏极电流 ( I DS ) 与施加的背栅电压 ( V BG ) 的关系图,FET 具有基于通过 MOCVD 生长的双层和多层(三到四层)WSe2薄膜的 Pd 触点。显然,与双层 WSe2 FET 相比,多层 WSe2 FET 显示出更高的 p 分支电流,多层 WSe2 的改善幅度约为 20 倍。这可以归因于多层 WSe2的带隙小于单层/双层WSe2以及金属费米能级的中间带隙钉扎,使其更容易实现双极传输。

除了层厚度之外,接触金属的选择对于实现 WSe2 FET 的 CMOS 功能也起着关键作用。扩展数据图2a显示了分别在 WSe2薄膜上使用 Pd 和 Ni 接触的 250 个器件的传输特性。Pd 接触主要产生 p 型特性,而 Ni 接触则观察到 p 分支电流减少了近 100 倍。Ni 接触还将 n 分支电流提高了近三倍。这一观察结果可以归因于 Pd 和 Ni 的费米能级与 WSe 2带隙的对齐方式不同——两种金属都能够进行双极传输;然而,Pd 更接近价带,而 Ni 更接近导带。

为了进一步提高 n-FET 的性能,我们利用通过原子层沉积 (ALD) 生长的亚化学计量 Al2O3进行表面电荷转移掺杂。扩展数据图3a、b显示了 Al2O3沉积前后具有 Ni 触点的WSe2 FET的传输特性,阈值电压明显负移,平均电压提高近 100 倍。证实了使用 ALD Al2

O3对 WSe 2进行 n 型掺杂。p 分支电流也抑制了近 6 个数量级,从而实现了近乎单极的 WSe2 n-FET。观察到的 n 型掺杂可归因于 WSe2/Al2O3界面处的固定电荷和陷阱态,它们增加了 WSe2沟道中的电子浓度。这类似于高电子迁移率晶体管中的调制掺杂。此外,如扩展数据图3c中的直方图所示,n 分支 (SS n ) 的亚阈值斜率没有下降,表明电子的掺杂源自不在 WSe2带隙内的掺杂态(参考文献30)。

还进行了拉曼和 PL 光谱分析,以了解 ILD 沉积的影响。扩展数据图4a显示了拉曼光谱,其中观察到红移约 1 cm –1埃2G1峰,这表明 WSe2中的电子浓度增加(参考文献32)。PL 发射光谱的红移以及主峰的增宽进一步证明了这一点(扩展数据图4b ) 。红移和峰值增宽与 WSe 2薄膜中电子浓度增加而形成的带负电的三子有关 。还采用了密度泛函理论 (DFT) 计算来研究 Al2O3电介质沉积对 WSe2的影响。

双层 3D CMOS 集成电路的制造

在优化 WSe2薄膜厚度、接触金属和电介质界面后,在 285 nm SiO2 /p ++ Si 衬底上完成了基于 WSe2的两层 M3D CMOS IC的制造。原则上,任何与光刻兼容的衬底都可用于实现 3D CMOS IC。这两层器件均由 2 nm Ti/18 nm Pt 背栅和 9 nm Al2O3 /3 nm HfO2 /3 nm Al2O3背栅电介质堆栈组成,等效氧化物厚度 (EOT) 约为 6 nm。所实现的栅极堆栈提供了类似闪存的功能,可用于实现内存计算应用。如前所述,为了分别启用第 1 层和第 2 层中的 n-FET 和 p-FET 器件,我们采用了不同的接触材料:

第 1 层 n-FET 器件采用 20 nm 的 Ni/10 nm 的 Pt,而第 2 层 p-FET 器件采用 20 nm 的 Pd/10 nm 的 Au。为了确保第 1 层 n-FET 器件和第 2 层 p-FET 器件之间的电隔离,使用厚度约为 82 nm 的 ALD 生长 Al2O3层作为 ILD,同时也用作第 1 层 n-FET 器件的 n 型掺杂层。最后,实施了后通孔方法来建立第 1 层和第 2 层器件之间所需的连接,从而方便我们演示电路。通孔采用 90 nm 的 Ni 和 30 nm 的 Au 构成,通孔宽度为 300 nm,确保跨层之间的稳健连接。通孔尺寸的这一成就凸显了 M3D 集成技术所带来的封装密度的提高。

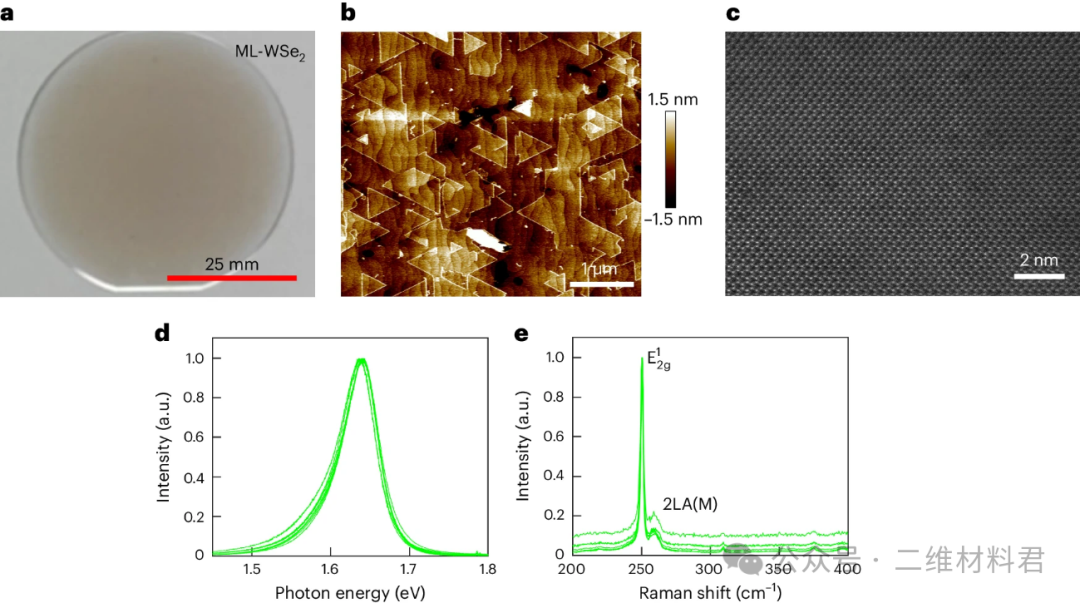

在完成第 2 层制造之后,对第 1 层器件的器件特性进行了重新评估。图3a,f分别显示了 340 个第 1 层和第 2 层器件的传输特性,其中第 1 层和第 2 层器件之间的 p 分支特性下降了近 4 个数量级,而 n 分支特性提高了 2 个数量级。除非另有说明,所有讨论的器件的沟道长度 ( L CH ) 和沟道宽度 ( W ) 分别为 300 nm 和 1 µm,并且所有参数都是在漏极偏压 ( V DS ) 为 1 V 的情况下提取的。图3b显示了使用等电流法在漏极电流 ( I DS ) 为100 nA µm –1时从第 1 层器件的 n 分支提取的阈值电压 ( V TH-n ) 的分布。对于 tier-1 器件的 n 分支,获得的平均V TH-n为 1.35 V,标准差为 0.97 V。还提取了I DS两个数量级变化的n 分支(SS n;图3c )的亚阈值斜率,其中对于 tier-1 器件,最小 SS n为 142 mV dec –1,平均 SS n为 282 mV dec –1,标准差为 73 mV dec –1。图3d显示了 n 分支导通电流 ( I n ) 的分布,该电流是在载流子浓度 ( n s ) 为 1.4 × 10 13 cm –2时提取的,这对应于 3.4 V 的过驱动电压 ( V OV )。实现的最大I n为 26.00 µA µm –1,其平均值和标准差分别为 10.80 和 5.84 µA µm

–1。最后,图3e显示了使用峰值跨导法获得的提取电子场效应迁移率 ( µ n ) 的分布。获得的最大电子迁移率为 6.90 cm 2 V –1 s –1,其平均值和标准差分别为 3.11 和 1.38 cm 2 V–1 s –1

图3g-j概述了提取的 2 级器件中 p 分支的器件参数。图3g显示了相同等电流(100 nA µm –1 )下的V TH-p分布,平均V TH-p值为 –0.84 V,标准差为 0.33 V。1 级和 2 级器件之间观察到的不同V TH-p范围对于实现具有离散和明确定义逻辑电平的 CMOS 电路至关重要。避免阈值电压重叠至关重要,因为它可以确保每个器件在其指定的逻辑电平下工作。针对I DS 的两个数量级变化提取了p 分支的亚阈值斜率(SS p;图3h ) ,其中最小 SS p为 244 mV dec –1,平均 SS p为 570 mV dec –1,标准差为 160 mV dec –1。虽然必须探索进一步的钝化策略来最大限度地降低 WSe 2中的缺陷密度,从而进一步改善亚阈值斜率,但已发现所获得的 SS n和 SS p值足以保证基于 WSe 2 FET 的 CMOS 反相器和逻辑门的正常运行,这将在后续章节中说明。图3i显示了 p 分支导通电流 ( I p ) 的分布,该电流是在载流子浓度 ( p s ) 为 1.64 × 10 13 cm

–2时提取的,此时V OV为 –4 V。获得的最大I p为 16.00 µAµm–1,平均值和标准差分别为 7.85和1.64 µA µm–1 。请注意,基于 WSe2的 n-FET 和 p-FET的导通电流相对相似,这对于 IC 的设计至关重要。在补充材料第 6节中,我们针对 WSe2 FET器件间差异与现有硅技术进行了基准讨论。虽然材料质量和界面的进一步改进可以提高性能,但我们结合接触和介电工程来实现近乎对称的 n-FET 和 p-FET 特性的方法值得注意。

此外,值得一提的是,第 1 层和第 2 层器件之间的器件间差异更多地受到 WSe2薄膜生长和转移过程的影响,而不是第 2 层中观察到的增强的拓扑复杂性。扩展数据图5a显示了 240 平面和具有 Pd 接触的第 2 层器件之间的转移特性,其中两组器件的通道材料都是在相似的生长条件下合成的,并通过相同的 PMMA 辅助湿转移技术进行转移。有趣的是,第 2 层器件表现出更高的我页米AX(扩展数据图5b)降低了器件间差异,V TH-p分布(扩展数据图5c)和较低的 SS p(扩展数据图5d )就是明证。这表明,在 WSe 2 FET的双层 M3D 集成中,形貌在器件间差异中起着次要作用。然而,我们相信,随着更多层级被整合到 M3D 芯片中,可以引入化学机械抛光技术,从而有效解决与形貌相关的挑战。

另一个有效的考虑是在任意层上演示 p-FET 的可行性,即使该器件用 ILD 封装时也是如此。扩展数据图6a、b显示了在 5 nm HfO2 ALD 沉积之前和之后带有 Pd 触点的40 WSe2 FET 。显然,并未观察到 n 分支特性的改善,尽管 p 分支电流确实降低了。值得一提的是,可以实施额外的 p 掺杂策略,例如用钒进行替代掺杂或用 WO x Se y 或 NO x 进行表面电荷转移掺杂,以进一步增强 p-FET 特性。扩展数据图 6c显示了在20秒的O 2等离子体之后带有HfO2 ILD的WSe2 FET的传输特性。观察到V TH的正移,同时 p 分支电流增加而 n 分支电流受到抑制。换句话说,通过精心设计接触和电介质界面,可以创建单极 WSe 2 p-FET 和 n-FET,使其成为构建 CMOS 电路的绝佳选择。

图 3:M3D 集成 CMOS WSe 2 FET。a、 340 个一级 WSe2 n-FET 的传输特性,其沟道长度(LCH )为 300 nm,宽度( W )为 1 µm。b - e 、在漏极电流(IDS )为 100 nA µm –1时提取的 n 分支阈值电压( V TH-n )( b )