来源:路科验证公众号 及 EETOP BLOG

如今的SoC设计中,IP中的寄存器等设计组件的数量和复杂性不断增长,关于CSRs(control and status registers)的问题在当今的SoC设计中相当普遍,无法正确地控制或接收这些组件的状态可能导致严重的问题。工程师们常使用基于仿真的方法来验证CSR功能,但是这种方法并不理想,因为它们不能完全穷尽所有可能。能有一个自动化验证指定寄存器的流程是IP开发人员和验证工程师的迫切需求。

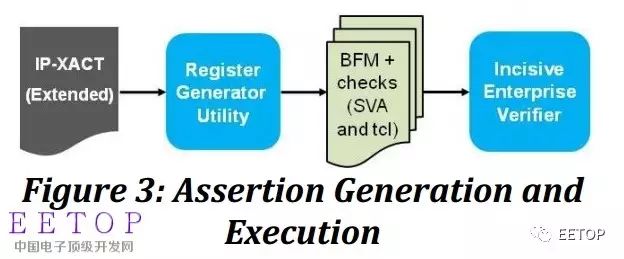

本文介绍了一个寄存器验证流程,以解决寄存器映射的验证要求。这种方法详尽地检查了基于IPXACT描述的SoC寄存器映射。此流程使用内部脚本将寄存器文档转换为IP-XACT格式,然后使用商业化形式验证工具生成断言,以完全验证寄存器的访问。

寄存器验证背景

关于寄存器验证,我们面临的突出问题是花费了太多时间设置和执行仿真,效率太低,同时,我们也不能保证所有的寄存器映射都完整的验证到了。我们渴求的是一个能够在SoC级别进行仿真测试的完整验证环境,并且对于不断更新的SPEC也无需进行太多复杂的设置,就能够验证所有的SoC和IP寄存器。

我们以前的寄存器映射的验证,主要是在C语言环境中针对所有SoC寄存器编写定向测试。但是我们发现基于C的定向测试来验证所需要测所有情况是很困难的,而且我们也无法解决与寄存器重叠或超范围寻址等相关的问题。当然要说明的是,我们没有使用UVM_REG,因为涉及环境设置和加速时间,UVM还没有被我们的团队完全采用。

更有效的寄存器映射验证流程

寄存器验证流程基于以下三个关键组件:

图1表示寄存器验证流程的各种元素及其彼此之间的交互。现在详细说明这些关键部件。

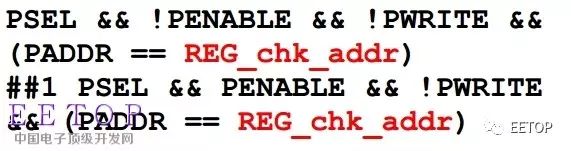

IP-XACT是一种IEEE标准(IEEE 1685-2009),被广泛用于寄存器和存储器映射管理。 IP-XACT为IP描述提供了XML架构,用于方便地捕获有关接口、信号、端口、参数、存储器映射、寄存器、文件详细信息等,也方便管理每个版本的设计更改。这样可以减少开发和验证时间和成本,更简单的共享数据。除了寄存器IP-XACT之外,我们还需要为设计的复位序列提供读取和写入序列的SVA(SystemVerilog Assertion)序列。当然这一流程是可扩展的,不单单适用于特定的接口协议。对于常见的协议,例如APB等,我们需要的读写序列在库中已经有。已提供的APB SVA写序列(WRITE_SEQ)如下:

提供的APB SVA读序列(READ_SEQ)如下:

REG_chk_addr和REG_chk_data都是预定义寄存器。REG_chk_addr表示出了被测试的目标寄存器地址。REG_chk_data表示出了接口上的写数据总线上驱动的所有数据模式。将这些序列组合以创建测试序列,以验证访问策略,如下面的关于读写访问策略检查。

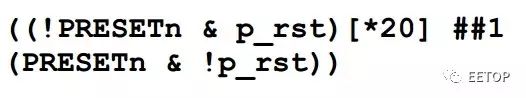

复位序列(RESET_SEQ)对每个设计都是特定的,对于本设计,SVA序列表示我们设计的复位序列。此设计需要将PRESETn驱动为20个时钟周期的低电平,将p_rst驱动为20个时钟周期的高电平。断言结束后一个周期后复位序列终止,最后一行即表示两个复位信号都无效。

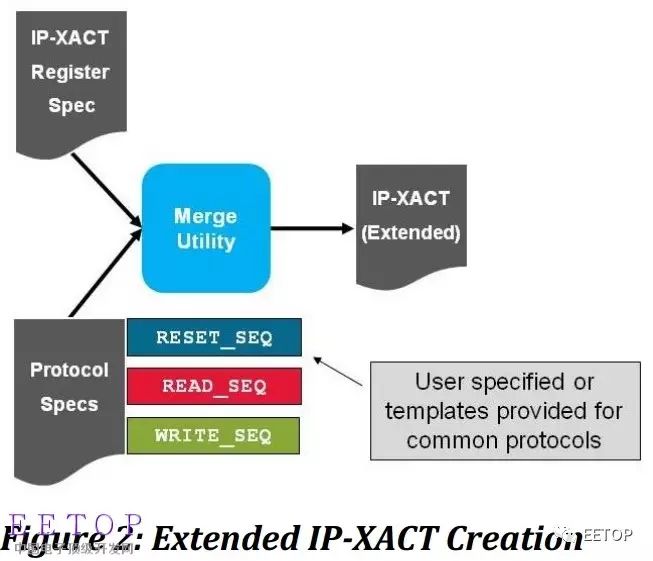

将这些序列与寄存器IP-XACT组合,创建扩展IP-XACT文件,如图2所示

下一步是生成断言,如图3所示。BFM驱动设计接口以及设计中的每个访问策略的检查。寄存器发生器读取IP-XACT规范,并生成一组使用Cadence Design Systems的Incisive Enterprise Verifier(IEV)编译执行的输出文件。所生成的文件包括SVA文件、用于验证配置寄存器策略的总线序列、用于执行每种类型的访问策略检查(reset,RW,RO等)的tcl文件、以及具有将所创建的SVA文件绑定到顶层设计模块信息的文本文件。

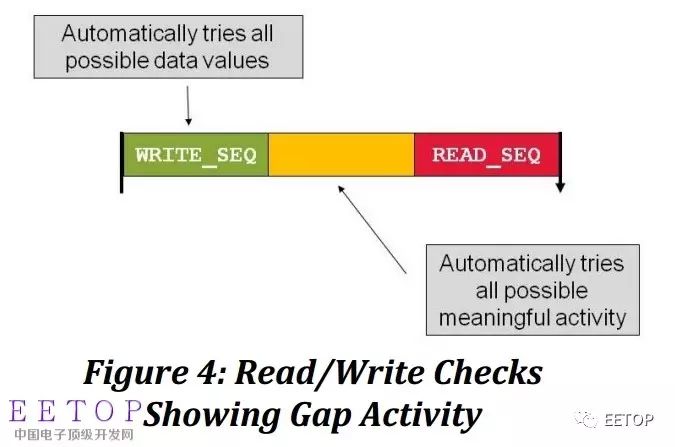

默认情况下,所有的序列都是一个接一个紧接着执行的。为了找到所有的错误,这里也引入了间隙活动的概念。间隙活动在读写策略检查时,会导致读取和写入序列之间的混乱。它控制额外的自由活动区域,除了写入它正在检查的地址之外,任何行为都可以完成。这里的检查支持前门访问和后门访问。前门检查通过接口协议进行,而后门检查通过直接访问寄存器完成。图4示出了间隙活动的概念,在该示例中用于说明读/写检查。对此读/写示例,在间隙活动期间,不发出写入目标。虽然形式化技术默认可以探寻到所有可能的接口/设计行为序列,但是我们的方法采用增量方法来控制IP寄存器访问接口上的这种行为。这样,你可以控制“混乱”的注入,借此来弄清楚设计对这种混乱的敏感性。

断言的检查列表如下:

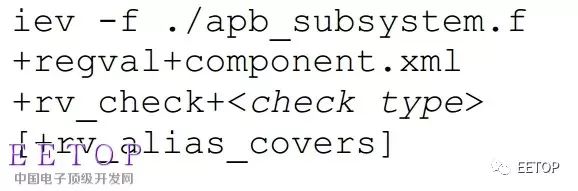

以下的示例用以说明如何使用IEV执行生成的检查。我们为IEV指定了IP-XACT组件描述的XML文件,用于执行如下检查:

其中:

component.xml文件被处理过后,就会产生以下由IEV生成的输出文件:

效果

我们在我们的SoC中的多个不同的IP块上执行寄存器映射验证。对于具有200-300个寄存器的IP模块,执行时间大约为2-3小时。我们在RTL冻结之前执行测试,结果反馈给设计和文档管理团队以进行所需的更新。对于可以使用IP-XACT描述的寄存器IP块的复杂性方面也并没有受限制。事实上,复杂性的极限是由断言的状态的数量决定的。为了提高我们复杂性的极限,同时由于我们的检查测试都是独立的断言,我们可以利用多个处理器来并行执行。工具本身就是支持这种行为的,而且执行起来也很方便。实际上,我们已经看到,对于由多个前面描述的IP块组成的子系统,该方法扩展后也可以进行验证。这种方法已经帮助我们清除了许多设计与规范不匹配和寄存器访问策略(RW与RO)错误。

结论

本文的寄存器映射验证流程能够实现我们的目标,使用IP-XACT使寄存器指定更方便,从而实现快速设置;通过为我们的接口协议提供预先存在的读写协议库;并通过自动创建断言来检查寄存器访问策略,从而加速寄存器映射验证,并提高验证的完整性。总的来说,这还是一个很不错的验证策略。

rvf_reg_check.svp

rvf_ext_bind.txt

特定检查的tcl文件

+ regval选项指定要处理的组件的xml文件。这是在IEV中运行寄存器验证流程所需的必需选项。

+ rv_check选项指定要执行的检查。 可以是rw,ro,rst,w1c或w1s。这是一个强制选项。

+ rv_alias_covers选项创建读写检查覆盖

Reset Checks

Read-Write Checks

Read-Only Checks

Write One Set Checks

Write One Clear Checks

长按二维码,加群主为好友,拉你入群

为了更好地便于大家交流学习,EETOP组建了 IC验证群,欢迎行业内朋友加入,加群方法: 先加 jack_eetop 为好友,发送如下信息:加群+IC验证+单位(或院校)。

加群前请务必在朋友圈分享至少一篇EETOP的微信文章

点击阅读原文查看更多

点击阅读原文查看更多