我们有幸请到了UCLA的PhD KO大神来为我们介绍一些sense amplifier的insight,本系列可以作为电路大师课系列

电路大师课系列-模拟集成电路设计第四讲:基本π网络(上)

的课外读物 :)

读出放大器简介

存储器是用于保存信息的记忆设备,如随机存储器(

RAM

)、磁盘(

disk

)、闪存(

Flash

)等存储器均在计算机系统中得到广泛应用。读出延迟,功耗,面积

/

位,和价格

/

位都属于存储器的重要指标(显然,你不希望自己的手机因为存储器而续航低,价格贵,速度慢)。读出放大器是存储器电路的一个重要组成部分,它属于读出电路的一部分(显然,所有存储器都要支持读出操作)。读出放大器的使用恰恰可以大大降低读出延迟和读出功耗,同时与其他降低延迟的功耗的方法相比面积代价较小。

SRAM

位线结构;

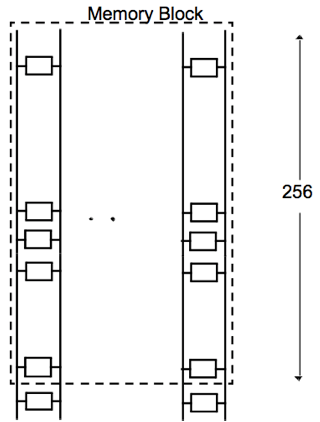

我们以一个典型的静态随机存储器(

SRAM

)为例,来说明读出放大器的重要性和性能指标要求。如图是

SRAM

的位线(差分:

BL/BLB

)的列结构,当某一行被选中后(相当于选中了希望读出的数据),该行存储单元则会根据存储的数据将位线对的某一条位线下拉,该信号将被后续读出电路读出。如果把该行的存储单元当成数字电路中的一个门(

gate

),则可以算出该门的扇出在

100

的数量级,远远偏离电路延迟(

latency

)的最优解数十倍。由于该门显然处于关键路径(

criticalpath

)上,可以想象,如果依靠存储单元得到轨对轨输出,不光对存储器的读出延迟的影响是灾难性的,而且功耗也极大(

E(peroperation)=VQ=C

BL

V

DD

2

)。有两个思路可以改善这个问题:

1.

仍然使用大信号读出(

large-signal sensing

),通过减小扇出,即减少单对位线上的存储单元数量如使用多级(

hierarchical BL

)结构;

2.

使用小信号读出(

small-signal sensing

),即使用读出放大器将位线的信号放大,意味着不需要轨对轨的位线信号即可读出存储单元的数据。我们这里介绍第二个思路

。因存储器阵列的相似结构,读出放大器不仅在

SRAM

中使用,

在其他种类的存储器如动态随机存储器(

DRAM

),闪存(

Flash Memory

)中也得到广泛使用。从上面的简介我们可以得到推出读出放大器应该具有的特性:

1.

高速;

2.

面积小(

SRAM

可以有

1000

个以上的读出放大器);

3.

低功耗。然而,我们知道

FET

的参数如阈值电压在制造完成前可以看成随机变量,无法控制。而在数量庞大的读出放大器的客观条件下,我们无法对单个读出放大器的偏移电压(

offset voltage

)做校准(

calibration

),这一点与锁存型放大器在数据转换器和高速有线通信中的应用非常不同,因此我们必须使用结构简单的低偏移读出放大器。

历史上多种放大器均被当做读出放大器使用。对于模拟集成电路学习者最容易理解的读出放大器则是静态差分放大器。然而,这类放大器几乎可以作为反面教材,具有静态功耗大,无法将小信号放大至轨对轨等缺点。将电流而非电压作为输入信号的

SRAM

读出放大器在

2000

年左右曾被研究,因其具有可以忽略输入电容而几乎没有延迟的将存储单元的驱动电流作为信号放大的优点。然而,电流读出放大器电路往往需要多级放大结构,太过复杂而导致面积太大的问题。经过长年的自然选择,一类读出放大器脱颖而出,它就是锁存型读出放大器。锁存型读出放大器具有几乎所有的优点:高速,面积小

/

结构简单,功耗低(无静态功耗),轨对轨输出。这里介绍两种经常被使用的锁存型读出放大器。

当然,需要指出的是,本文介绍的电路结构不仅仅只应用于读出放大器,锁存型读出放大器的电路结构如

StrongArm

锁存器的电路结构也在存储器以外的领域作为比较器(

comparator

)、限幅器(

limiter

)、锁存器(

latch

)被使用,这是由于它们和读出放大器的功能相似性决定的。这些领域包括但不限于数模转换电路、串并

/

并串行转换器。

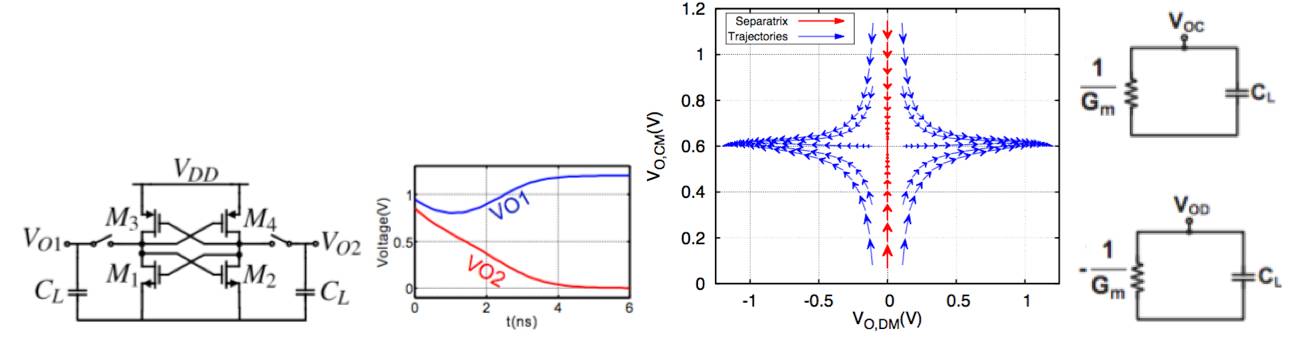

基于交叉耦合反相器(

Cross-CoupledInverter

)的读出放大器

交互耦合方向器电路图;电压的时间演化和相空间图;共模

/

差模等效电路;

对任何正反馈放大器的讨论都应该从简单且易于理解的交互耦合方向器开始。功耗:因为正反馈,放大器的输入信号将被放大至轨对轨。由于这个特性,在放大完成后,该电路的功耗降为零,这是锁存型放大器普遍的特点。速度:对该电路有了定性的了解后,我们接着理解该正反馈电路的动力学过程。如果选取共模电压和差模电压作为独立变量,我们可以通过基于基尔霍夫方程组的动力学方程组或基于仿真得到如图所示的动力学相空间图。从图中我们可以明显看出共模电压和差模电压是一对正交的变量,意味着两者独立变化而不受互相的影响。事实上我们可以得到其等效电路(如图)。共模电压对应的极点是稳定极点,而差模电压对应的极点是不稳定极点,这两个极点的位置由负载和反相器跨导决定。由于该电路的线性性直到差模电压很大时才失效,因此极点的位置和输入信号的大小决定了该放大器的速度。偏移电压:由于该放大器只有四个

FET

,根据

pelgrom

定律,在设计面积一定的情况下我们因此可以得到非常小的等效输入偏移电压。由于正反馈放大器的特点,我们不能使用对静态放大器的分析方法分析该电路的偏移电压公式,必须对该电路进行动力学分析,找出各个失配下的亚稳态(

metastable point

,数学上称为“

Saddle fixed point/

鞍点不动点”)和对应的分界线(

separatrix

,图中红色直线,是失配的函数,数学上称为“

stable manifold/

稳定流型”)。

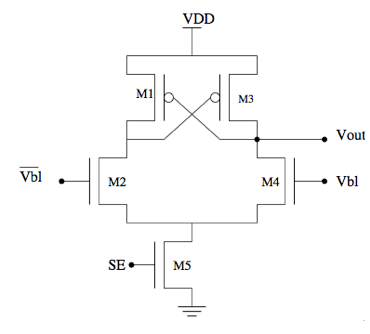

实际中基于交互耦合反相器的读出放大器在其为核心的基础上加上若干

FET

控制开关。该读出放大器的一个重要特点是输入节点和输出节点相同。如在

SRAM

中,输入共模电压是

VDD

,使用最广泛的读出放大器则加上两个

FET

用于隔离位线电容和一个用于开启和关闭读出放大器的

FET

,而无需在

PFET

端也加一个开关。有趣的是,利用正反馈特性,交互耦合反相同时也是

SRAM 6T

存储单元的核心结构。在

DRAM

中,由于输入共模电压一般为

VDD/2

,因此需要两个

FET

控制开启关闭,并且由于

DRAM

需要重新写入被读出的存储单元,因此不能隔离位线(大电容),这也是

DRAM

读出一般比

SRAM

慢的一个重要原因。

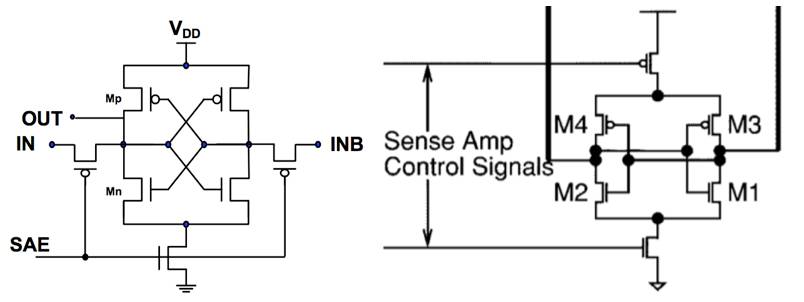

SRAM/DRAM

常用的读出放大器;

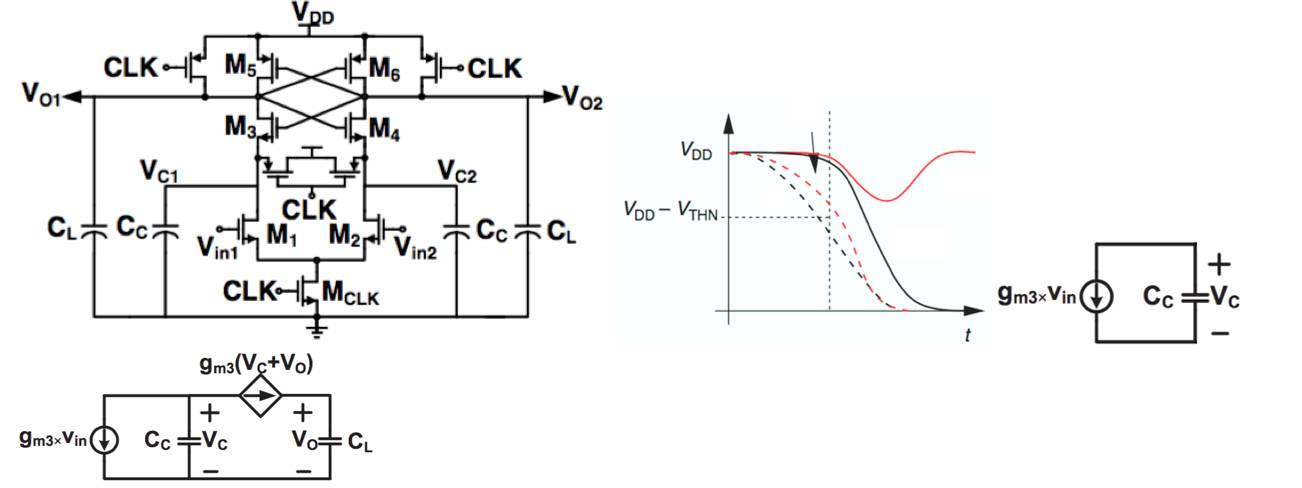

StrongArm

锁存器

StrongArm

电路图;信号随时间演化(虚线:

V

C1

/V

C2

;实线:

V

O1

/V

O2

);差模小信号等效电路:采样;转移;

StrongArm

锁存器最初由

Abidi

教授的学生

Kobayashi

教授于

1993

年提出,得名于本电路在

StrongArm

微处理器中的使用。如图所示,核心

FET

是

M1-M6

。这个电路提供了一个方便的方法,将输入电压耦合至交互耦合放大器,从而隔离了输入和输出端口:输入电压信号通过输入对管转变成电流信号,该电流信号在输出端口产生一个初始电压使交互耦合放大器再生放大至轨对轨信号,因而该电路在

SRAM

设计者中也被称为电流锁存读出放大器。这个电路的动力学过程有三个阶段:采样,转移,再生。每个阶段伴随着一定的信号放大。初始时节点

C

和输出节点

O

均为

VDD

。采样阶段时,所有交互耦合放大器的

FET

(

M3-M6

)均处于关断,输入信号在电容

C

C

上积分并在节点

C

形成一个信号,同时伴随着节点

C

的共模电压下降。转移阶段时,

M3

和

M4

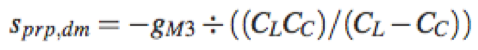

开启并处于饱和区,差模小信号等效电路如图,该电路只有一个稳定极点:

同时注意到节点

C

和

O

的总电荷守恒,因此在此阶段输入信号积分的所有电荷将被转移至输出节点并放大(稳定时

V

C

为负),形成再生阶段的初始电压。再生阶段的动力学行为则与交互耦合反向器非常相似。在了解了

StrongArm

锁存器的原理以后,我们可以得到一个很显然的结论:即为了保证再生阶段的初始信号足够大(以抵抗

FET

失配),必须保证输入对管始终处于饱和区(输入共模电压小于

VDD-VTN

),否则电荷将从输入对管的等效电阻泄露从而信号放大倍数大大降低。

SRAM

中使用的

StrongArm

锁存器则存在这个问题,在固定面积的条件下,该读出放大器的输入偏移电压约为之前介绍的读出放大器的两倍,这也是

StrongArm

锁存器在

SRAM

应用中的主要缺点。然而,高速的

StrongArm

锁存器则要求输入共模电压要大,从而将采样和转移阶段的延迟降低,而基于交互耦合反相器的读出放大器速度则与输入共模电压无关

。

这里需要指出,由于在存储器应用中无法校准偏移电压,因此噪声是不重要的。在数据转换器的应用中,则还要分析噪声的贡献

。

留一个问题:

从读出放大器的性能指标的角度,为什么该电路未作为

RAM

读出放大器被广泛使用?(留言回答正确有福利:))

《矽说》创办的宗旨就是与大家分享有用的信息,倾听大家的声音,并争取帮工程师发声,为中国的芯片行业工程师社区建设尽自己的一份力量。

我们建立了矽说交流群,希望能给大家提供一个互相交流的平台,多多结识志同道合的人。也欢迎大家给我们提意见,吐槽!

欢迎扫描下方二维码

填写您的信息,我们会邀请您入群!