受制造工艺等的限制,硅基芯片的发展已经渐渐达到了极限,而碳纳米管芯片身量虽小,节能增效能力却更强;韧性极高,可以承受弯曲、拉伸等应力,电信号传输过程的延迟很短;碳管晶体管还能有效避免漏电导致的发热问题,因此被认为是未来硅的理想替代者。

硅材料是半导体工业的重要原料,多年来,由于信息技术的发展,电子产品的性能随着需求的增加日益提高,而硅基芯片技术发展到现在,也已经快要抵达材料本身所能承受的极限了。

那么,在芯片领域,是否有哪种材料能成为硅的完美替代者?目前,碳纳米管芯片被寄予厚望,而且,中国在这方面是走在世界前列的。

(一)硅基芯片虽好,7nm已经是物理极限

计算机技术的发展很大程度上推动了这几十年的世界科技进步,如今人们的生活已经离不开互联网与计算机。计算机的核心是一块小小的芯片,而组成芯片的主要基质材料就是硅。

硅材料能够成为整个现代电

子学革命的支撑点,主要因为以下两大特性:

首先,硅是一种优秀的半导体材料,在特定条件下施加电压时,它会变为导体,这正好满足了芯片的工作需求;其次,硅的来源非常广泛,从石英岩和砂(主要成分二氧化硅)中就能够以较低的成本提取出纯硅。

不过,硅基芯片虽好,其使用性能也渐渐达到了理论的极限。英特尔创始人之一的戈登·摩尔曾提出过著名的摩尔定律:当价格不变时,集成电路上可容纳的晶体管数量大约每隔18个月便会翻一番,性能也将提升一倍。

集成电路早期的发展的确如他所说,各大芯片制造公司也基本上按照这个规律在提高单个芯片上硅晶体管的数量,但时至今日,硅基芯片的发展已经开始受到制造工艺物理极限的限制。

要提高芯片上晶体管的数量,主要靠的是芯片工艺的改进。想必大家一定听到过这样的说法,某某核心处理器(CPU)采用了XXnm制造工艺,常见的工艺还有90nm、65nm、40nm、28nm、22nm、14nm之分,芯片制造工艺的大小也就成了考量芯片制造水准的指标。

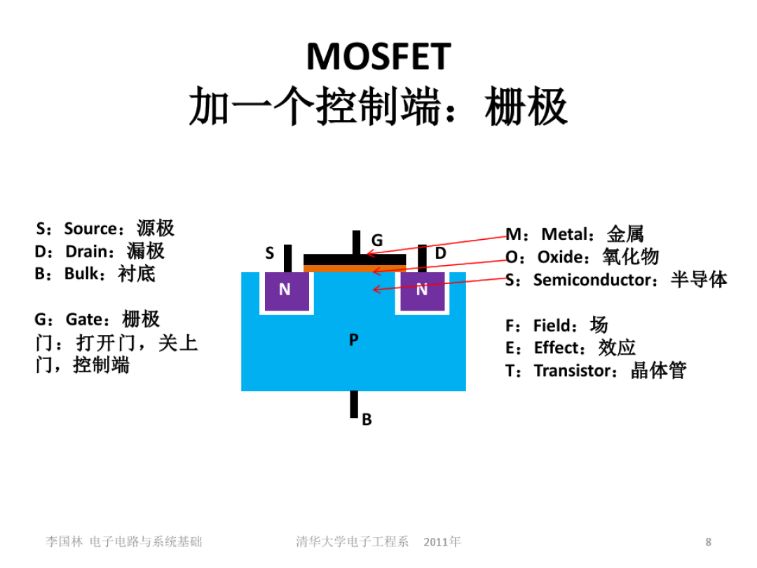

图注:模拟电路与数字电路的金属氧化物半导体场效晶体管,CPU内的晶体硅衬底上就集成了以亿为单位的该类型晶体管,电流从源极流入漏极,栅极则起到控制电流通断的作用(逻辑上的0与1)

所谓的XXnm工艺指的就是晶体管栅极的宽度,也就是栅长。

在相同硅芯片尺寸的前提下,栅长越短,就意味着上面集成了更多的晶体管,芯片性能也就越强;集成度不变的前提下,栅长越短,芯片的面积和功耗也会相应地下降。因此,芯片生产厂商会想方设法地减小晶体管栅极宽度,以保持其芯片性能的领先地位。

不过,栅长不可能无限地短下去,因为短的栅长会使内部电子移动距离缩短,从而晶体管内部电子可能会自发通过晶体管通道的硅底板从负极运动到正极,也就产生了漏电。而且随着芯片中晶体管数量增加,氧化物绝缘层会变得更薄(几个原子层厚),使得泄漏的电子更多,从而增加芯片额外的功耗。

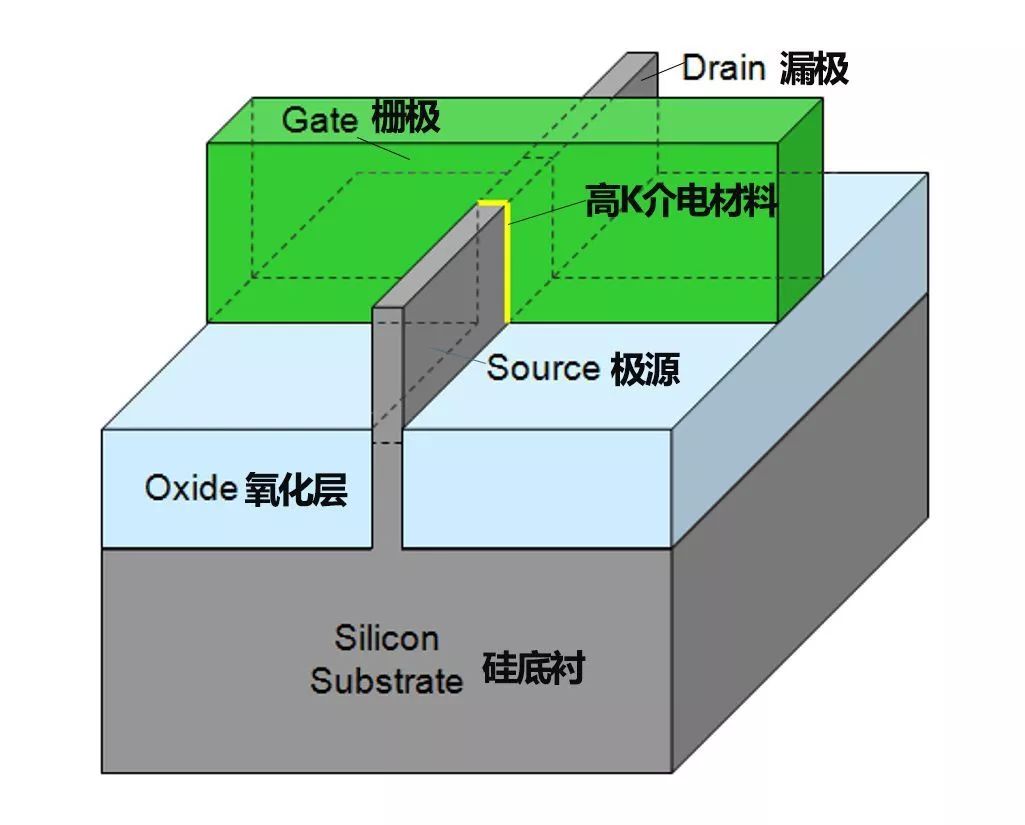

如何解决漏电问题,也正是各大芯片厂商在研究更小纳米工艺时首先要考虑的问题。有的厂商采用的鳍式场效电晶体管技术(FinFET),就是在原有设计的基础上通过增加绝缘层的表面积来增加电容值,降低漏电流以达到防止发生电子跃迁的目的。

此外,各大公司也各有自己的高招:英特尔在其制造工艺中融合了高介电薄膜和金属门集成电路以解决漏电问题、IBM开发出SOI技术——在源极和漏极埋下一层强电介质膜来解决漏电问题。

图注:FinFET示意图,原图来源于网络,了不起的中国制造栏目进行汉化处理

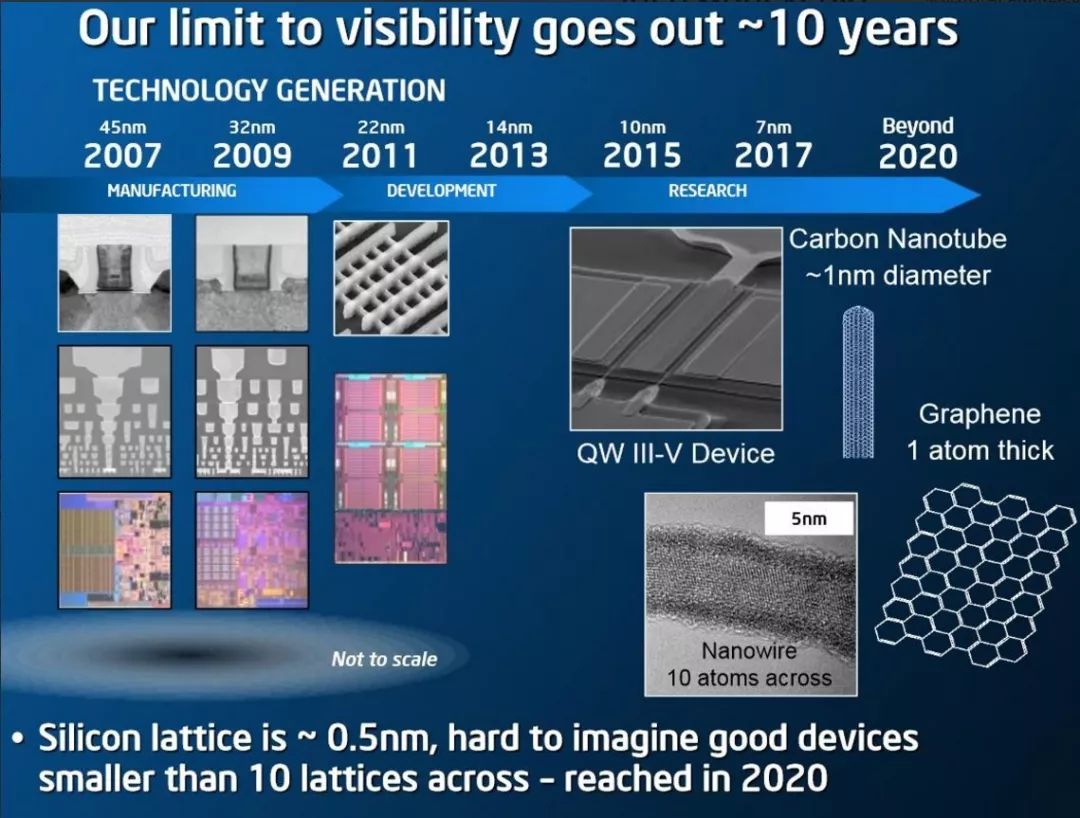

这些做法只在栅长大于7nm时才能有效解决漏电问题,而在现有的芯片材料前提下,晶体管栅长如果低于7nm,晶体管中的电子就很容易产生隧穿效应,这也就是7nm硅材料芯片的物理极限的由来。

针对这一问题,寻找新的材料来替代硅制作7nm以下的晶体管,一直是芯片制造行业的巨大挑战,而碳纳米管复合材料被认为是其中一种较好的选择。

(二)考虑到漏电和发热问题,碳纳米管比硅芯片能效高

图注:英特尔对半导体工艺的进展预期

碳纳米管被寄予替代硅的厚望与其本身的特性息息相关。

首先,碳纳米管芯片身量虽小,节能增效能力却更强。碳纳米管是由单层碳原子卷成管状的碳材料,导电性能极好,而且,碳元素在地球上的储量十分丰富。

碳纳米管的直径可以根据工艺的不同制成几纳米到几十纳米长;管壁厚度更小,根据壁层碳原子数量不同,碳纳米管可以分为单壁碳纳米管和多壁碳纳米管;在同样集成度的情况下,碳纳米管芯片比硅元器件体积更小。

同时,碳纳米管的韧性极高,可以承受弯曲、拉伸等应力,电信号传输过程的延迟很短,所以,从材料物理属性上看,碳纳米管具有替代硅芯片的潜力。

其次,碳材料具有多种同素异形体,除了碳纳米管以外,还有人们熟知的金刚石、石墨、富勒烯、活性炭等等。其导电性质强烈地依赖于结构,可以由绝缘体转变为半导体、由半导体变为导体。而且,它的导电方式和原理与传统的晶体管不一样,有更强的传导能力。

图注:碳的同素异形体

另外,现有的晶体管在导电过程中无可避免地会产生漏电流,漏电会导致发热,而碳纳米管可以避免这一问题,故而能效相对较高。从理论上讲,碳纳米管芯片的能量利用率有望超过现有芯片的能效比(60%至70%)。

发热问题的解决也给芯片的散热降低了压力。硅晶体管的功耗很大,在小小的芯片空间内,发热极其严重,为了不使芯片过热无法工作,还需要分配部分的功耗用于芯片的散热,这使得硅晶体管功耗增大。

而碳纳米管芯片本身产热就少,加上碳纳米管本身的热导率很高,有效地减少了用于散热的能耗,所以碳纳米管的能效会远远高于以硅为材料的晶体管。

(三)中国已经掌握碳管晶体管技术,领先硅基技术20年

从理论上讲,采用碳纳米管的芯片可以比硅基芯片在速度和功耗上有5—10倍优势,这对于后摩尔时代的集成电路而言有无可比拟的优势。不过如何把碳纳米管做成场效应晶体管,而且还要保证它的优势,仍是很大的挑战。

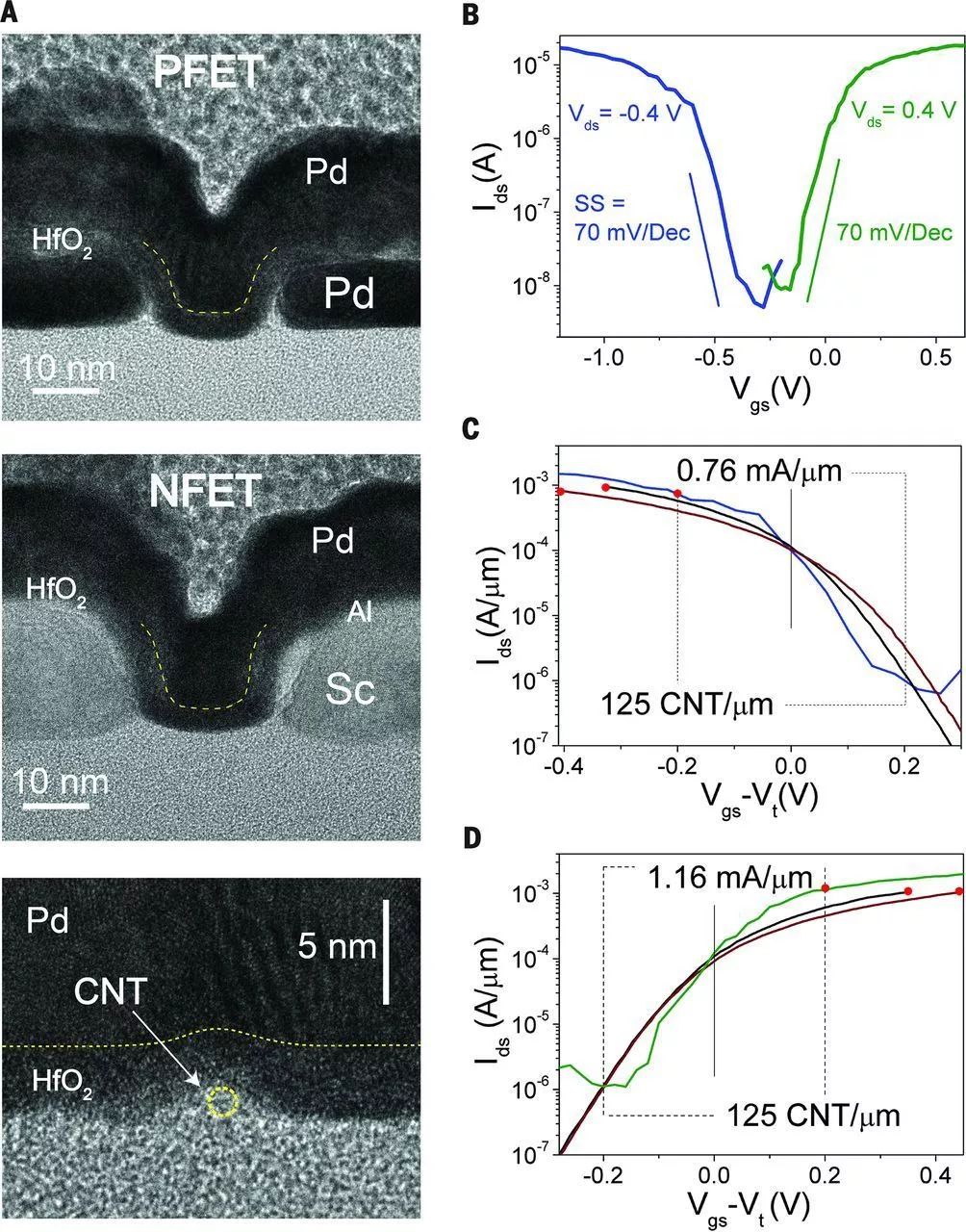

世界范围内,最早实现碳纳米管器件制备的是IBM,其在2014年成功制备出碳纳米管20nm栅长器件,不过,该器件性能比预期差很多。近年来,也有国外的各类实验室号称制备出1nm栅长的碳纳米管器件,但更多的只是噱头,实际使用性能很差。

而中国在碳纳米管器件的研究方面紧跟国际前沿。北京大学的彭练矛—张志勇研究团队在该领域已经进行了十多年的精心研究,在高性能碳纳米管(CMOS互补金属氧化物半导体)晶体管的无掺杂制备、晶体管的极性控制方面有很多技术积累。

其中该团队制备的栅长为10纳米的碳纳米管顶栅CMOS场效应晶体管(对应于5纳米技术节点)已经成功攻克器件结构和制备工艺等相关难题。不仅如此,其制备出的碳纳米管器件的性能也远远超过国际上已报道的碳纳米管器件。

图注:10纳米栅长碳纳米管CMOS器件。A:n型、p型和栅堆叠型器件截面图;B:碳管器件的转移曲线;C—D:与硅基CMOS器件(Intel,14nm,22nm)输出特性的对比

而且,在早期技术积累的前提下,该团队还进一步探索5nm栅长(对应3纳米技术节点)的碳纳米管晶体管,这一研究成果在去年1月登上了美国《科学》杂志。

对于常规结构制备的碳管晶体管,其栅长在5纳米以下时就会较为明显地受到短沟道效应和隧穿漏电流影响,以往融合高介电栅介质薄膜的做法很难有效地解决漏电问题,使得器件也不能有效地关断。