文章链接:https://pubs.acs.org/doi/10.1021/acsami.3c15535

东京大学材料工程系Kosuke Nagashio课题组利用同质结实现了横向结构的TFET。

摘要

二维(2D)材料在低功耗电子器件,特别是物联网时代的隧穿场效应晶体管(TFET)中展现出巨大的潜力。这种潜力源于其无悬挂键的范德华异质界面。然而,高性能器件的实现受到需要精确控制多层堆叠2D材料的限制。在本研究中,我们研究了一种厚度调制的n/p+-同质结,该结由Nb掺杂的p+-MoS₂晶体制备而成,在这种同质结中,由于不需要外部界面控制,界面陷阱问题可以忽略。值得注意的是,我们的观察表明,即使在室温(RT)下,也存在负微分电阻现象。这标志着在室温下,通过单栅在III型带对齐条件下成功实现了TFET的操作,表明主要电流机制是由于理想界面引起的带间隧穿。

研究背景和主要内容

在物联网(IoT)时代,减少电路和系统的功耗以实现自供电设备是半导体研究人员面临的首要挑战。然而,当前功耗缩减的困境直接源于金属氧化物半导体场效应晶体管(MOSFET)在亚阈值区间的亚阈值摆幅(SS)无法缩减至室温(RT)下低于60 mV/dec的水平,这定义了传输特性中的亚阈值区间的陡度SS的限制来自于源区热电子载流子在高能尾部的波尔兹曼分布。为了解决这一限制,基于碳纳米管(CNT),硅,硅/锗, III-V,和氧化物/IV半导体的隧穿场效应晶体管(TFETs)已被广泛研究,因为它们可以通过带间隧穿(BTBT)有效抑制高能载流子。尽管对传统半导体异质结TFETs进行了大量研究,但由于在p/n异质界面产生载流子的复杂问题,异质界面的活性缺陷水平难以降低,从而恶化了SS性能。

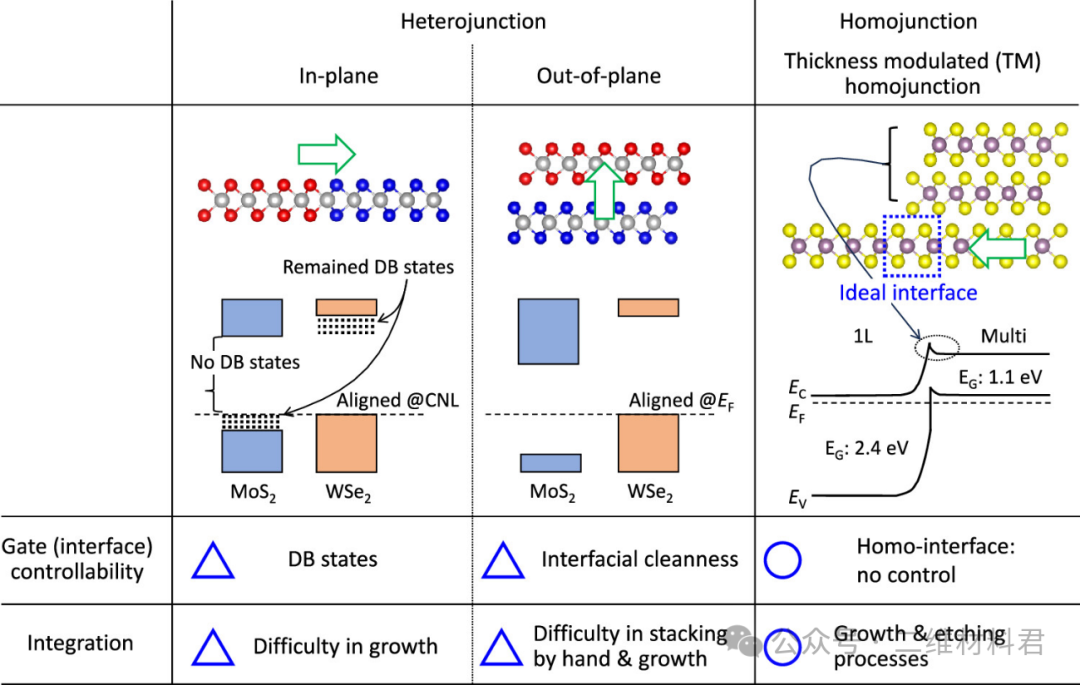

在此,二维(2D)材料为隧穿场效应晶体管(TFETs)提供了理想的平台,因为无悬挂键的范德华(vdW)异质界面最大限度地减少了载流子的产生,并且vdW界面的短隧道距离增加了开态电流。图1全面总结了典型的面内和面外vdW异质结构的特性。在栅极可控性方面,密度泛函理论计算表明,面外异质结构优于面内异质结构,因为即使在面内异质结构中形成了完美结合的异质界面后,悬挂键(DB)状态仍然存在。实验上,最近报道了通过化学气相沉积法生长的面内n-MoS2/p+-MoS2异质结构的负微分电阻(NDR)趋势,表明DB状态的影响可能并不显著,因为NDR趋势明显表明在II型和III型能带对齐之间的平滑栅极可控性。另一方面,面外vdW异质结构的优势在于任何2D材料都可以通过弱vdW力任意堆叠而无需考虑晶格失配。对于通过机械剥离组装的有限2D vdW系统,如WSe2/MoS2,WSe2/SnSe2,MoS2/p+-MoS2,和MoTe2,已经证明了亚60 mV/dec的SS值,但排除了通过离子栅极执行的TFET。然而,vdW异质结构所需的多层堆叠的串行组装并不适合进一步将TFET性能提升到传输模拟和随后的应用所预测的水平。

最近,提出了另一种二维结构,即厚度调制(TM)同质结,如图1所示。由于带隙能量(EG)在很大程度上取决于层数,因此自动实现了适用于TFET的能隙各向异性,即源的较小EG以减少隧道屏障宽度和通道的较大EG以最小化关态电流。这里的关键点不在于实际构建范德华异质界面,而在于利用作为异质界面的物理特性。由于界面只是一个同质结,因此无需任何界面控制便可忽略界面陷阱问题。因此,在TM同质结黑磷TFET中,获得了最佳的2D-TFET性能,其平均SS值约为26 mV/dec跨越5个电流数量级,且在SS = 60 mV/dec时的高开态电流约为1 μA/μm。然而,问题在于单个器件中使用多个栅极独立控制源和通道的极性,这因不可避免的寄生电容而阻碍了实际应用。

迄今为止,TM同质结的垂直和并行电输运特性已被研究。尽管是同质结,但应注意在多层侧形成的边缘,如图1所示,因为TM同质结的能带对齐在很大程度上受到其边缘态的影响。已知边缘在约20 nm的有限宽度内自然掺杂p型,以保持边缘的电荷中和。考虑到边缘的贡献,基于光电流线扫描实验,提出了单层/多层MoS2的TM异质结在边缘向上弯曲的I型能带对齐。所有这些研究都是对通过机械剥离固有MoS2晶体而制成的器件进行的,且没有任何掺杂。在此,讨论了通过化学气相传输(CVT)生长的Nb掺杂p+ -MoS2晶体,其空穴浓度为2 × 10¹⁹ cm⁻³,使用摩尔比为Mo:S= 1:2:0.005的源粉制备,名义上掺杂0.5%的Nb。有趣的是,在这种晶体上的FET特性表现出随着层数减少从未调制的p+行为向n型行为的过渡,如图S1的补充信息所示。尽管Nb浓度在整个厚度上是均匀的,但在机械剥离过程中在MoS2表面附近产生了S空位。当层数减少时,S空位产生的电子浓度变得比Nb掺杂的空穴浓度更大,导致在传输曲线上表现出n型行为。如果从Nb掺杂的p+-MoS2晶体形成单层/多层同质结,则将自动形成n/p TM同质结,如图1所示。TM同质结的单栅TFET操作是可以预期的。

在本研究中,我们研究了由Nb掺杂p+-MoS2晶体制备的n/p+ TM同质结。在这种具有理想界面的器件结构中,TFET操作在III型能带对齐下通过单栅实现。此外,通过揭示电流流动路径和n/p+ TM同质结内的n/p+界面位置,讨论了降低SS的指导原则。

图 1. 异质结(平面内和平面外)和同质结的 2D-TFET 比较。图中给出了它们各自的结构、能带图和器件特性。

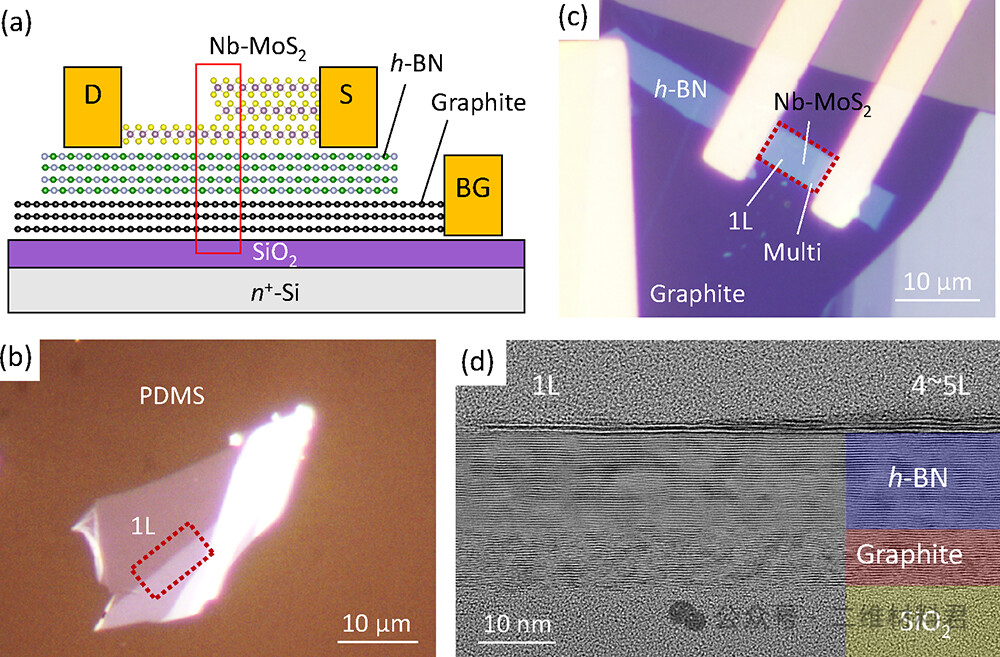

图 2. (a) 具有h -BN/石墨背栅的 TM 同质结 Nb 掺杂 MoS2 TFET示意图和 (c) 光学显微照片。(b) PDMS 上具有 TM 同质结的Nb 掺杂 MoS2晶体的光学显微照片。(d) 来自 (a) 中实心矩形的 TM 同质结 Nb-MoS2 TFET 器件的横截面 TEM 图像。

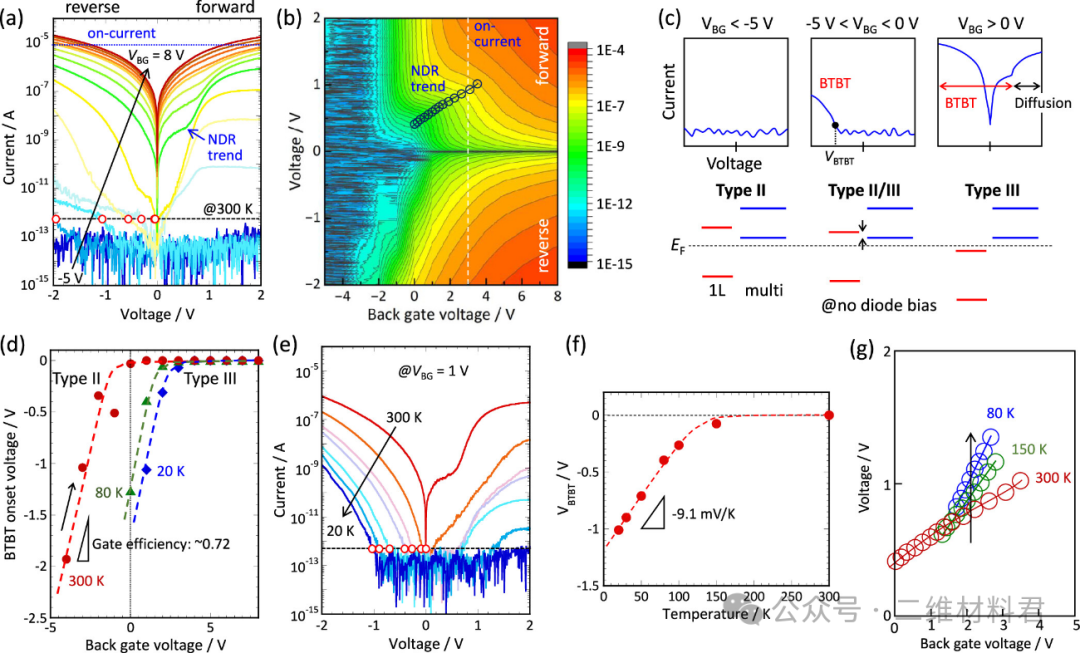

图 3. 不同V BG和 300 K下TM 同质结 Nb 掺杂 MoS2 TFET的 (a) 二极管特性和 (b) 其轮廓图。(c) 三个不同V BG范围内的二极管特性与相应的能带图示意图。(d)从 (a) 中提取的V BTBT作为不同温度下V BG的函数。虚线供参考。(e) V BG = 1 V 和不同温度下的二极管特性。(f)从 (e) 中提取的V BTBT作为温度的函数。虚线供参考。(g) 不同温度下从 BTBT 电流到扩散电流的转变点的轨迹。

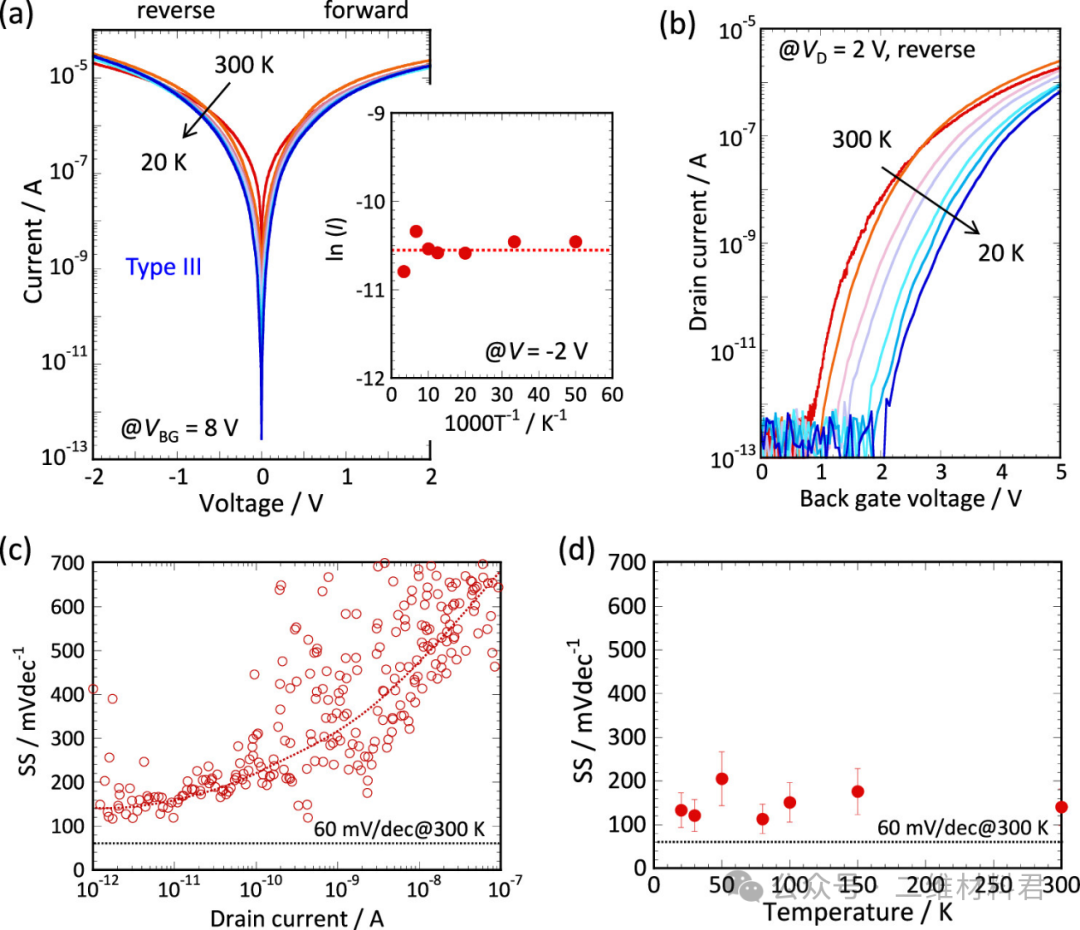

图 4. (a) V BG = 8 V(20、30、50、80、100、150 和 300 K)时二极管特性的温度依赖性。插图显示了反向偏置 −2 V 时的电流与温度的关系。(b) V D = 2 V(反向偏置)时传输特性的温度依赖性(20、30、50、80、100、150 和 300 K)。(c) 300 K 时 SS 与I D的关系。虚线用于引导视线。(d) SS 与温度的关系。

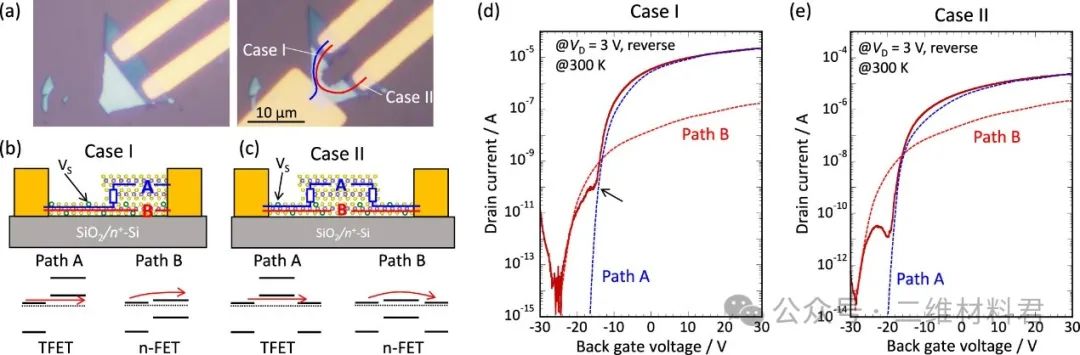

图 5. (a) 构建器件的光学图像。可以清晰地观察到几层和厚多层 MoS2之间的清晰界面。(b) 具有 n/p +的案例 I 器件结构,其中显示了电流流动路径 A 和 B。(c) 具有 n/p