近五十年来,集成电路上的晶体管密度果真如威名赫赫的“摩尔定律”所预言的一样:每两年就会翻一番。

这一现象的出现也就意味着:那些芯片生产商们,如英特尔、AMD或是高通,每两年就要绞尽脑汁、想方设法地往相同尺寸的芯片里塞进比之前多一倍的晶体管,以便我们年复一年的用上性能更强,处理速度更快的电脑芯片。

这些生产商们为了在芯片中容纳更多的晶体管,就将芯片内部的晶体管阵列设计得如同城市网络般复杂纷繁。因此,毫无悬念的是,晶体管尺寸被设计得越来越小,他们之间的距离也靠得越来越近。

举例而言,英特尔在 2014 年推出的Broadwell处理器已经将组件之间的距离缩小到了 14 nm。这个距离嘛,大概是 1 张普通A4纸厚度的 1 万分之一。

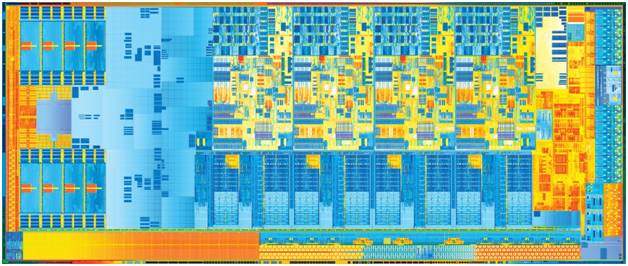

CPU内部结构示意图与电脑芯片内部扫描电子显微镜图像

如此精密的设计与排布,使得芯片制造商们面临着一个令他们束手无策的难题:如何才能在不破坏芯片的前提下,去观察芯片的内部结构?毕竟,只有看到芯片的内部结构,制造商们才能确保这批已经完工的芯片结构与他们所期待的如出一辙。

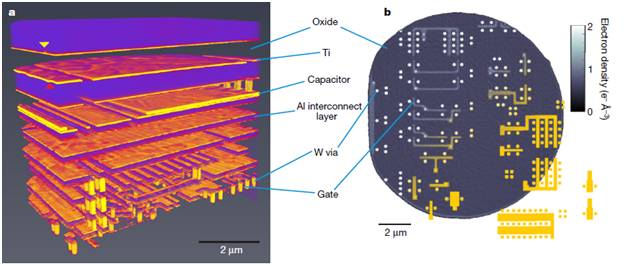

来自瑞士的保罗谢勒研究院(Paul Sherrer Institute,PSI)的研究员们为这个难题找到了一个可行性的解决方案。在这篇发表于《自然》杂志上的文章中,他们使用了一项名为“叠层衍射X射线计算机断层扫描成像”的技术,成功的得到了一枚英特尔芯片的内部 3 维构造。

“叠层衍射成像”是一种不依赖透镜,通过恢复衍射图像中相位的成像手段。简而言之,研究人员们向一块不停旋转的芯片照射一束X射线,接着通过电脑程序分析而得到不同角度芯片的衍射图案,从而在电脑中重建芯片内部精密的三维结构。

在这次研究里,PSI的研究人员们先后对两枚芯片进行了测试。其中一枚是由PSI自行开发研制的,采用了110纳米工艺制作的专用集成电路芯片(ASIC);另一枚则是来自英特尔的奔腾G3230处理器,这枚处理器采用了22纳米的工艺,与最现代的14纳米工艺仅有一步之遥。

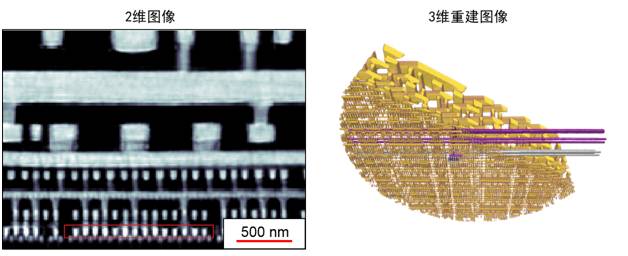

PSI自制的专用集成电路芯片的3维结构与对应的2维图像

利用这项技术,研究人员们实现了高达14.6纳米的分辨率,成功的复原了这两块芯片的内部结构。令人倍感欣喜的是,他们可以清晰地看见芯片内部的晶体管和内部电路。

毫无疑问,PSI研究人员开发的这项手段,是芯片检测技术的一项重大飞越。

但在此之前,芯片内部的检测大多依赖于扫描电子显微镜,或透射电子显微镜来看一探究竟。这两种常规手段需要像剥洋葱一般,工作人员需耐心地、一层一层地除去芯片的上层电路,才能够最终揭示芯片内部晶体管的形貌。这一手段费时费力不说,更令人不满的是,即使再小心翼翼,仍不可避免的会破坏芯片内部的三维结构。

如前文所言,随着芯片的集成度越来越高,芯片内部晶体管的层数也日渐增多,实际内部电路的厚度有时可达约十微米之多。在这种情况下,依赖于电子显微镜、进行逐个分析晶体管的过程就显得难以为继。对于已经封装的电脑芯片而言,这两种手段更是无能为力。

一名来自普渡大学的一名电子爱好者,为了一探电脑芯片内部的究竟,像砸核桃一样,把芯片砸出一个大洞。(如下图)

被砸坏的芯片

相比于前两者,研究人员所开发的“叠层衍射成像技术”则道高一丈。这项技术集X射线所具有的两大特点于一身:高穿透率和高分辨率。

不仅如此,在芯片检测这项应用中,这项技术还拥有常规电子显微镜所难以企及的两个优势:其一,避免了对芯片内结构的破坏;其二,避免了因切割不精细而导致图像的扭曲变形。

如此一来,人们便可以利用这项技术来获取“三维结构芯片”更加完整且准确的信息。

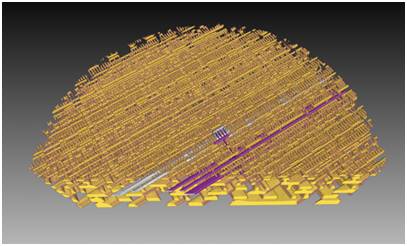

另一张英特尔处理器的三维结构示意图

但就目前形势来看,这项技术距离实际应用还欠些东风。在本次研究中所使用的“X射线光源”可不是某个业余爱好者可以在自家后院就能鼓捣出来的“光”。

研究人员们为了得到最好的成像效果,使用了隶属于PSI的瑞士同步辐射光源的“高相干辐射X-射线”。即使在全球,类似的同步辐射光源设施也屈指可数。

另一方面,这项研究同样也耗费了不少时间,研究人员不仅要花24小时才能完成叠层衍射实验,而且还需要另一个24小时去处理得到的数据。

瑞士光源的鸟瞰图

不过,本次研究的负责人,同时也是该论文的第一作者莫尔克·霍勒(Mirko Holler)胸有成竹的在文章中表示:通过使用更多的计算机、改进实验装置以及X射线源,会将这一实验所需的时间缩短至现在的千分之一。

除此之外,更具挑战性的的一点在于:闻名的“摩尔定律”驱使着芯片制造商们连年推出尺寸更小的晶体管。在这种情况下,人们观察芯片所用的“放大镜”也需要拥有自己的“摩尔定律”,才不至于在这场竞赛中落下太远。

就现在的情形来看,芯片制造商们已经占了上风。在本次研究中,莫尔克·霍勒所实现的最高分辨率约为 14.6 纳米,尽管这一数字十分了不起,可目前由英特尔开发的最新一代的处理器芯片,却已经迈进了10纳米制程的门槛。

无论怎么说,这次莫尔克等人的研究将在“芯片无损检测”领域上留下浓墨重彩的一笔。随着这项技术的进一步发展,或许在不远的将来,芯片内部结构的检视不再是“一锤子买卖”。

相反的,当人们将芯片放入某个类似的装置之后,即可一览芯片的内部构造。从这个意义上说,芯片的设计似乎变得“透明”了。

论文的作者Mirko Holler(右)与 Manuel Guizar-Sicairos(左)

与此同时,对于芯片制造商来说,这一技术的问世无疑将会对这个行业产生深远的影响。通过检视芯片内部是否存在制造缺陷这一做法,制造们可以借此实行更加严格的质量控制和品质管理方针。

除此之外,人们还能利用这项技术来确认集成电路设计,了解其内部功能,优化其生产流程,并找出可能的失效机制。

从消费者的角度看,这一技术同样惹人关注。最近,硬件安全也日益成为了一个颇受重视的话题。特别是对于国防和军工行业而言,如果能将这项技术能够加以运用,他们便可以确认,芯片内部是否存在可能窃取机密的恶意硬件,即所谓的“硬件木马”。毕竟,一块被砸坏了的芯片可是没有半点用处的。

时至今日,芯片无损检测的发展尚未成熟,但是瑞士保罗谢勒研究院的科学家们为真正的“透明芯片”的未来照亮了全新的路径。

参考资料:

1. M.Holler, et al. Nature, High-resolutionnon-destructive three dimensional imaging of integrated circuits, 543(2017):402-407

2. https://www.psi.ch/media/3-d-x-ray-imaging-makes-the-finest-details-of-a-computer-chip-visible

3. Deep into CPU, https://sites.google.com/site/imhengwu/work

4.http://blogs.discovermagazine.com/d-brief/2017/03/15/microchip-imaging-picture-look/#.WM_qrm8rIdU

5. http://spectrum.ieee.org/nanoclast/semiconductors/processors/xray-ic-imaging