广告

目录

1.

大联大品佳集团力推新唐科技MCU应用于DALI 2.0照明控制方案

2.

Semtech和MultiPhy宣布在OFC 2018上展示带有EML光学器件的100G单波长芯片组

3.Silicon Labs推出业内首款低功耗PCI Express Gen 4缓冲器

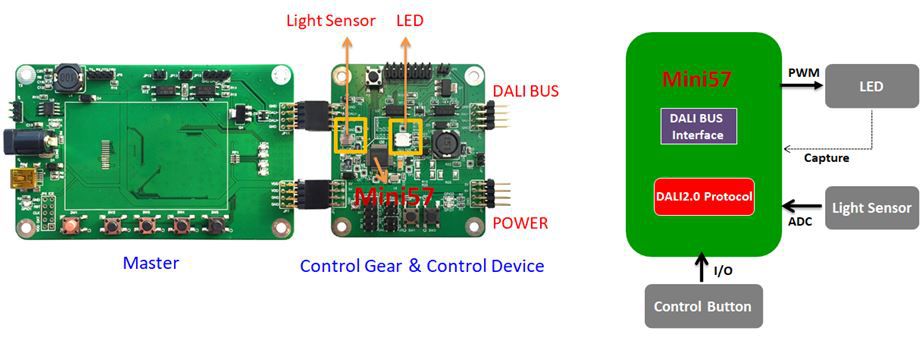

大联大品佳集团力推新唐科技MCU应用于DALI 2.0照明控制方案

2018年3月15日,

致力于亚太地区市场的领先半导体元器件分销商---

大联大控股

宣布,其旗下品佳力推新唐科技MCU应用于DALI 2.0照明控制方案。

大联大品佳代理的新唐科技DALI 2.0灯光控制解决方案,搭载基于ARM® Cortex®-M0内核的NuMicro®Mini57系列微控制器,最高运行频率高达50MHz,内嵌32KB Flash内存及4KB SRAM,在DALI 2.0的应用中可支援多种的协定。例如,标准207的LED装置、标准202的紧急灯等。该方案亦整合了DALI BUS界面,可连接DALI系统与其它DALI产品互动,为DALI设备的开发者,带来了极大的便利性。

该方案主要实现DALI 2.0所需的多主机控制,此外,所需的软硬件完全开源,是一个对于开发者极为友善的平台,借由NuMicro® Mini57系列的高运算能力,快速转化资料以进行装置控制,开发者亦可以实现复合型装置应用。

功效特色

符合DALI2.0协议;

支持DALI2.0多主机互动模式;

具有总线冲突检测及修复功能;

电路简单,成本低;

宽电压输入支援8到24伏;

16位PWM输出控制;

PWM可触发ADC;

硬件捕捉(Capture)功能;

芯片工作温度105度。

相关IC

控制装置:Mini57EDE;

控制设备:N76E003;

适用于DALI Master的NUC240SE3AE。

广告

Semtech

和

MultiPhy

宣布推出

100G

单波长芯片组

2018年3月 – 高性能模拟和混合信号半导体及先进算法领先供应商Semtech Corporation和基于DSP的高带宽通信领域全球市场领导者MultiPhy Ltd共同宣布:他们将利用业界领先的、支持单波长100G以太网和通用公共无线接口(CPRI)光学模块的PHY/PMD芯片组,对100G单波长技术(Single Lambda Technology)进行最新的、开创性的展示。

两家公司将通过在OFC 2018上运行超过2公里的光链路来展示新型芯片组。单波长100G技术有望大幅降低太比特网络(Terabit networking)的成本,并且是建设下一代超大规模数据中心和新兴的5G无线网络的关键组成部分。

该展示由多条2公里链路组成,这些链路使用了Semtech的FiberEdge™芯片组和MultiPhy的FlexPhy器件来驱动EML光学器件。方案中包括Semtech具有高输出摆幅和线性度的FiberEdge GN1860 EML驱动器,Semtech的GN3289线性光接收次模块(ROSA)和GN1089高性能低噪声线性跨阻放大器(TIA),以及MultiPhy 的FlexPhy,这些器件旨在提供一种全面解决方案以实现100G单波长互连。

“Semtech的FiberEdge芯片组再次为100G 单波长技术设定了标准,此次公开展示完全可操作的、带有低成本EML光学器件的2公里链路标志着我们向100G单波长市场迈出了重要一步。” Semtech执行副总裁兼信号完整性产品事业部总经理Gary Beauchamp表示。

MultiPhy的FlexPhy平台是一款低功耗、高性能的DSP,它利用一流的信号处理技术来实现下一代数据中心和无线网络。该器件的任务模式是将4x25Gbps NRZ CAUI4主机总线转换后对接线路侧的单个100G PAM4 IO对。该器件采用小型BGA封装,带有在QSFP28模块中使用而专门优化的高速IO布局。

“100G单波长技术将主宰下一代数据中心网络。交付包括DSP / PMD在内的完整解决方案可为我们的客户提供更快速的集成和更短的上市时间,并且加速这种新技术的采用。”MultiPhy首席执行官Avi Shabtai表示。“基于PAM4的DSP可以在光数据中心连接市场中实现一种范例式的转变,即利用单波长处理能力来简化光学系统并优化成本和功耗。”

Silicon Labs推出

业内首款低功耗

PCI Express Gen 4

缓冲器

2018年3月15日-Silicon Labs(亦称“芯科科技”)日前推出了一系列低功耗PCI Express® (PCIe®) Gen 1/2/3/4时钟缓冲器,设计旨在为1.5V和1.8V应用提供超低抖动时钟分发。Silicon Labs的新型Si532xx PCIe时钟缓冲器具有40fs RMS(典型值)的附加抖动性能,可为严格的PCIe Gen 3和Gen 4抖动规范提供超过90%的余量,从而简化时钟分发和降低产品开发风险。

越来越多的数据中心硬件设计正在使用低功耗1.5V或1.8V电源,以最大限度地降低整体功耗,这些数据中心硬件设计包括网络接口卡(NIC)、PCIe总线扩展器和高性能计算(HPC)加速器。Si532xx缓冲器由单个1.5V-1.8V电源供电,具有多达12路时钟输出,非常适合在低功耗设计中提供低抖动PCIe时钟分发。Si532xx时钟器件支持PCIe通用时钟、分离参考无展频(SRNS)和分离参考独立展频(SRIS)架构,能够满足各种应用需求。

Si532xx时钟是基于非PLL的扇出缓冲器,支持展频时钟信号的分发而不影响信号完整性。随着PCIe端点数量在服务器和存储应用中的不断增长,要求系统设计人员提供更多的PCIe参考时钟的缓冲时钟副本。新型Si532xx系列产品的超低抖动性能使得设计人员能够级联多个缓冲器,同时仍能达到0.5ps RMS的最大允许系统PCIe抖动预算。

Si532xx器件输出驱动器利用Silicon Labs的推挽式HCSL技术,该技术不像使用恒流输出驱动器技术的传统PCIe缓冲器那样需要外部终端电阻。内部电源滤波可防止电源噪声降低时钟抖动性能,从而消除了竞争解决方案所需的离散式低压差稳压器。Si532xx系列产品支持85欧姆和100欧姆阻抗选项。

Silicon Labs时钟产品高级营销总监James Wilson表示:“我们利用Silicon Labs在高性能时钟设计方面的专业技术来降低PCIe时钟分发应用中的抖动和功耗。我们新推出的Si532xx系列产品显示Silicon Labs致力于帮助整合并简化数据中心、工业、通信和消费类设计中的高速时钟树设计。”

价格与供货情况

Si532xx PCIe时钟缓冲器已经量产,并可提供样片,其中包括多种输出选项。Si53212、Si53208和Si53204时钟器件提供12路、8路和4路PCIe时钟输出。样片可在两周内发货,批量订购可在四周内发货。在一万片采购量时,4路输出时钟器件的单价为1.40美元起,12路输出时钟器件的单价为2.17美元起。Silicon Labs的新型Si53204-EVB开发套件零售价为175美元,可提供快速、简单的PCIe缓冲器评估。