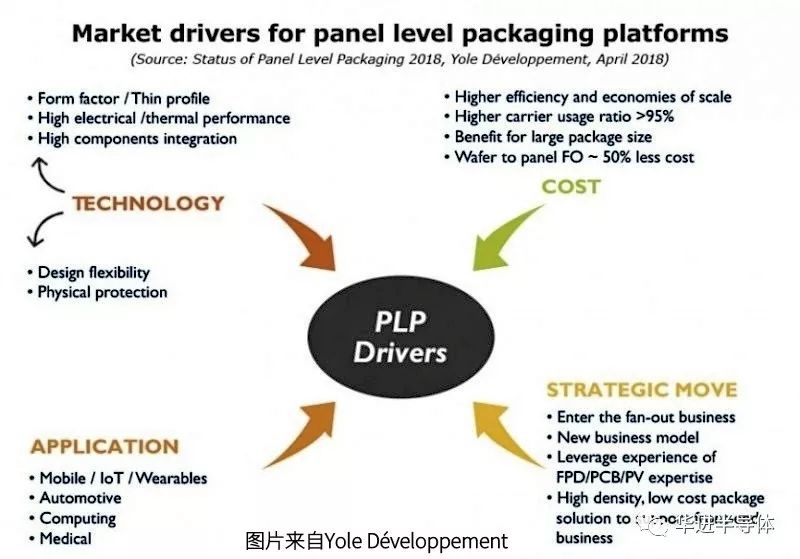

市场青睐低成本高性能产品,封装解决方案不断面临挑战与创新。扇出型封装技术始于2006年,经过十年沉淀,于2016年迎来了爆发式增长。目前,扇出型封装主要集中在晶圆级;然而,晶圆有限的利用率及其高昂的成本阻碍其大批量制造。从晶圆级到面板级的高性能、低成本的封装需求,驱动着半导体行业开发创新的解决方案。将晶圆级封装转变为大尺寸板级封装成为降低整体成本的新途径,在技术成熟的条件下,成本可降低50%,产品良率超过90%。事实上,板级工艺的基础设施已经引起了半导体行业的极大兴趣,其具有成本优势及规模经济效益,是一个有前景的市场。各种因素正在推动板级扇出封装(FOPLP)的发展,并鼓励全产业链(包括设备和材料)投资板级扇出基础设施,已经成为各大OSAT路线图上的重要战略布局。目前主要玩家包括如ASE、SEMeCO、NEPES、Intel、SAMSUNG。

扇出型封装市场目前主要集中在基带、电源管理及射频收发器等单芯片封装应用以及手机应用处理器芯片、动态存储器芯片、车载雷达和无人驾驶等高密度多芯片堆叠封装应用领域。扇出型封装技术正朝着诸如多芯片、薄型封装和3D SiP这些下一代封装方向出发,不仅应用于电子封装,还可用于传感器、功率IC和LED封装等领域。通过大板扇出封装技术可以获得小尺寸、更高的集成度和功能性,其应用领域包括无人机、汽车侧面避碰系统、自动停车装置等。

经过多年的工艺及技术开发和验证,FOPLP终于开始进入规模量产。根据Yole Développement,整体的扇出封装市场预计会从2015年的2.44亿美元增长到2022年的23亿美元,FOPLP市场营收预计将在2023年达到约2.80亿美元。Powertech Technologies(PTI)、NEPES以及SEMCO预计将在2018年底进入FOPLP量产。NEPES主要瞄准的是(L/S>10um)汽车、传感器和物联网相关的应用, PTI和SEMCO的长期目标是L/S <8/8或更小线宽线距的中高端应用。其余各大OSAT,如ASE、Amkor、JCET/STATS CHIPPAC等,也在评估技术方案,每个玩家都在基于自己的战略路线和设备设施进行板级扇出封装技术的研发和布局。

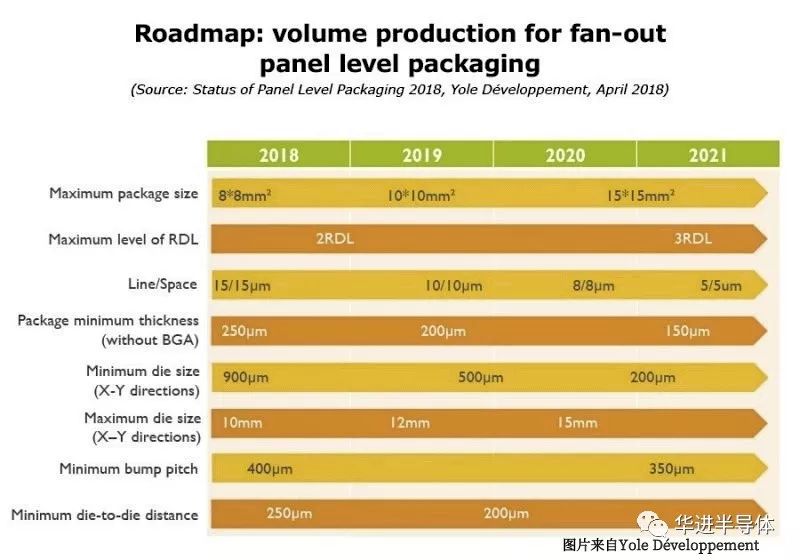

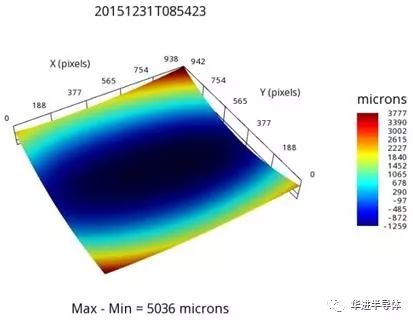

机遇与挑战并存,FOPLP的开发及产业化仍存在不少挑战。业界标准缺失,由于应用领域和客户不同,采用的制程及面板尺寸也不尽相同,终端用户很难根据统一的标准去选择,设备厂商也无法设计出满足不同尺寸要求的设备,产线配套设施投入昂贵。此外,还有一系列技术难关需要攻克,如翘曲控制、贴片精度、在大面板上制造小于10/10um的RDL线路等。FOPLP实现产业化必须统一标准,如板级尺寸和装配工艺的标准化。据Yole Développement的市场调研报告,目前大多玩家支持一个相对简单的设计:L/S>10/10 um,封装尺寸<10 x10 mm

2

,最多2层RDL。随着技术和经验的成熟,最终将采用高密度设计:L/S <10/10 um,多层RDL,封装尺寸>15×15 mm

2

和多芯片SIP集成。

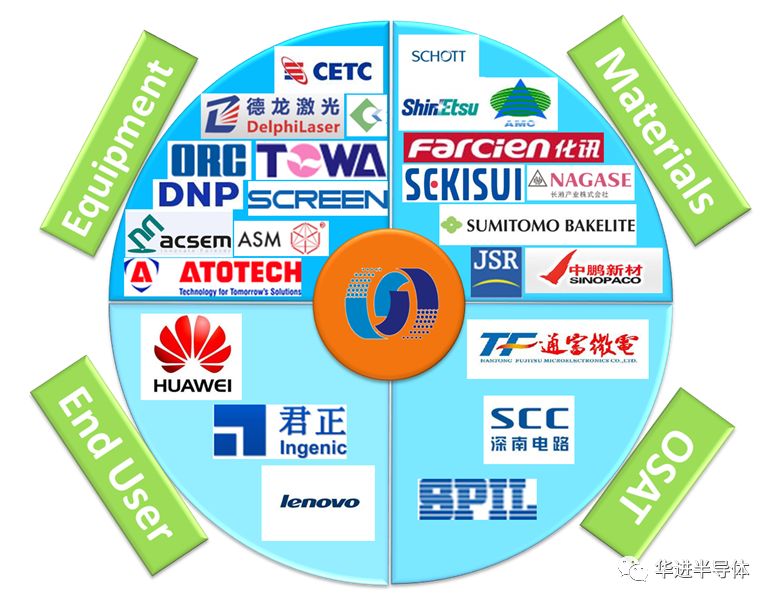

2015年,华进联合国内外25家企业成立了大板扇出联合体,主攻320mm×320mm板级扇出工艺技术的开发,形成了包括终端用户、设计、封装代工和材料装备于一体的完整产业链。我们的联合体成员包括华为、通富微电、深南电路、矽品精密、JSR、SCREEN、德龙激光、联致科技、ASM、SCHOTT、ATOTEC、ORC、SEKISUI、住友、上海微电子、技美科技等。联合体运作期间,完成了单颗芯片和单层RDL设计工作,并完成了热、机械和翘曲等的模拟和仿真工作;整合了板级扇出的产业链,开发了Die First(埋入式)和Die Last(基于基板)两种工艺路线,完成样品流片及可靠性验证;形成了大板扇出的核心知识产权,申请了5项大板扇出核心专利;评估和验证了FOPLP联合体成员单位的相关设备及材料,如SCREEN的SLIT coating涂布机和激光直写曝光机、ORC的PPS光刻机、ASM的贴片机、TOWA的塑封机、AOTOTECH的电镀机、KINGYOUP的种子层PVD溅射机、SUMITOMO的粉末塑封材料、NAGASE 的液态塑封料、JSR的光刻胶/PI/临时键合材料等。项目成果荣获“第十二届(2017年)中国半导体创新产品和技术项目”。

华进第一期大板扇出联合体成员

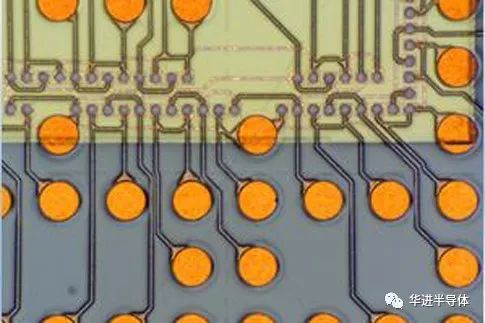

华进第一期大板扇出样品

随着一期联合体接近尾声,应广大成员的强烈需求,华进已开始筹备二期联合体。根据国内外多家设备/材料供应商的反馈,并结合华进参与的由SEMI草拟的第一版FOPLP板级尺寸的标准,二期板级尺寸定为600mm x 600mm,主攻多颗芯片和多层布线的板级扇出型封装的技术开发,培养一个专业的FO研发团队,提供从设计仿真、工艺加工到可靠性分析和测试的FOPLP整体解决方案,最终目标建立一条工艺示范线。具体工艺参数如下

:

|

华进二期SiP FOPLP联合体工艺参数

|

|

面板尺寸

|

600mm×600mm

|

|

最小L/S

|