文章链接:https://www.nature.com/articles/s41928-024-01289-8

亮点:

1.设计框架的提出:开发了一种基于量子传输模拟的设计框架,结合非理想接触和材料电容计算,确保设计的准确性。

2.材料选择与优化:发现三层钨二硫化物在能效和延迟方面相较硅晶体管表现最优,提升能量-延迟积55%。

3.2D纳米片晶体管:展示了一种新型二维纳米片场效应晶体管,集成密度和驱动电流相比传统3D晶体管提升了近十倍。

4.适用多种应用场景:提供低功耗和高性能应用下的优化设计,满足多样化需求。

5.支持CMOS进一步缩放:展示了二维半导体助力CMOS扩展至几纳米级别的潜力,为未来芯片设计提供了新方向。

摘要

原子级超薄的二维(2D)半导体,特别是过渡金属二硫化物,被认为是后硅互补金属氧化物半导体(CMOS)场效应晶体管的潜在沟道材料。然而,其在CMOS技术中的应用需要实现三维(3D)晶体管集成。在本研究中,我们提出了一种设计基于2D半导体的缩放3D晶体管的框架。此方法基于非平衡格林函数量子传输模拟,结合非理想肖特基接触和综合电容计算,并通过密度泛函理论模拟提供材料输入。针对不同3D晶体管(包括2D和硅基)及沟道厚度进行了比较性能分析,适用于低待机功耗和高性能应用。结果表明,三层钨二硫化物是最有前景的材料,其能量-延迟积相比硅基晶体管提升超过55%,有望将CMOS扩展缩小到几纳米。此外,研究还展示了2D半导体可以被独特地设计为2D纳米片场效应晶体管,与具有类似占地面积的2D和硅基3D场效应晶体管相比,其集成密度和驱动电流分别提升了近十倍。

研究背景和主要内容

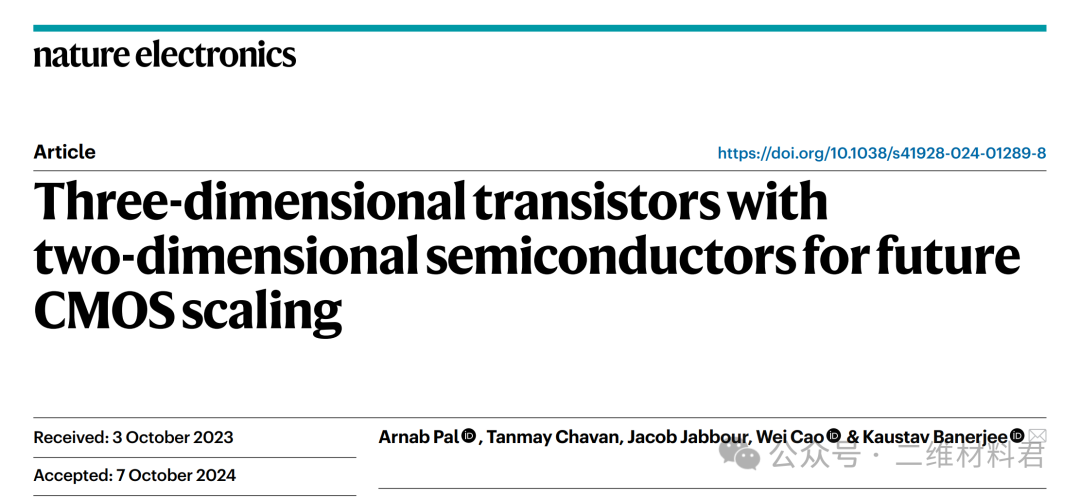

使用传统半导体材料来扩展互补金属氧化物半导体 (CMOS) 技术节点以提高系统集成密度、性能和能源效率,但对于沟道长度 ( LCH ) 小于 15 纳米的技术而言,这种扩展正在放缓。这是由于开关电流比的下降和相关的加工挑战造成的,这使性能改进与开发成本的比率降至最低 。二维( 2D) 范德华层状材料具有优异的静电性能,这是保持沟道长度 (LCH) 小于 10 纳米(沟道厚度小于 3 纳米)的扩展优势所必需的,并且通过减少与陷阱的相互作用、减少表面粗糙度散射和厚度变化来抑制载流子产生和复合,从而实现稳健的器件性能(图1a )。与硅相比,单层(1L)2D 过渡金属二硫属化物 (TMD) 具有更大的带隙,并且在传输方向上具有更大的载流子有效质量(1L MoS2沿传输x方向的电子有效质量为 0.57m0 ,而 Si 的电子有效质量为 0.19 m0 ,其中m0

为电子静止质量)也最大限度地减少了直接源漏隧穿泄漏 (SDTL) ,从而抑制了关断电流 ( IOFF ) 。此外,它们更大的态密度 (DOS) 和与硅相当的迁移率 -可以改善器件设计和性能- 导致良好的导通电流 ( ION )

图 1:基于 2D 材料的 NXFET 器件架构。a、这些超薄分层二维材料的原子排列示意图,表现出原始界面(左),从而最大限度地减少了表面粗糙度散射和通道-电介质界面处悬空键的存在,以及优异的静电性能(右),从而允许通过施加栅极偏压实现卓越的静电通道调制。b 、 2D TMD 与传统块体材料的迁移率比较,由于相关的表面粗糙度散射,后者的迁移率在亚 5 纳米沟道厚度下迅速下降。数据是从文献中报道的各种实验结果中收集的,相关参考文献在补充说明1中提到。c – e,示意图显示了 NSFET(c)、NFFET(侧视图 (SV))(d)和横截面视图 (CSV)(e),其中源极和漏极采用多层 2D TMD 实现,以及三个沟道堆栈(即n = 3),采用 1L 到具有 GAA 控制的多层 2D TMD 实现。f , n = 2时 NSFET(左上)和 NFFET(左下)的侧视图,以及 NSFET(右上)和 NFFET(右下)的截面图。LS、 LD 、 LCH和UL分别指源极、漏极、沟道和 UL 长度,WNS、tCH、tmetal、tox和tFS分别指纳米片宽度和沟道、金属、栅极氧化物和隔离鳍厚度。W eff是有效栅极宽度 (GW)。g 、沿对称方向从 DFT(左)计算出的1L WS

2的能带结构( x轴标签表示k空间中的相关对称点),以棕色/黑色显示 CB/VB,以深蓝色显示费米能级EF。CB中两个最低谷用绿色虚线圆圈突出显示,从中提取了用于建立 NEGF 形式主义的相关参数(右)。m *表示载流子的有效质量,沿平行于(x)和横向于(y)传输方向的方向计算。α是非抛物线因子,Δ E是两个谷能量最小值之间的能带偏移,BW 是带宽。

精心设计的多层 2D TMD 的迁移率与硅的体迁移率相似(图1b;补充说明1提供了相关参考文献),但当沟道厚度缩小到 3nm 以下时,2D TMD 的载流子迁移率几乎没有下降。相比之下,由于带隙变化和表面粗糙度散射,硅的迁移率 会大幅下降。此外,由于沟道-氧化物界面的表面变化引起的表面粗糙度散射仍然会导致超大规模(沟道长度低于 10nm)晶体管的传输效率低下,而这种晶体管中的传输预计实际上是弹道的。这进一步降低了实际硅晶体管的迁移率和性能。在 2D 晶体管中,表面粗糙度散射可以忽略不计。此外,随着栅极电介质、工艺、器件和应变工程的改进 ,少层2D TMD的迁移率可以进一步提高。

尽管使用薄 2D TMD 通道材料具有潜在优势,但也需要在器件架构方面进行开发。三维 (3D) 环栅 (GAA) 结构晶体管的改进静电特性尤其可用于提高器件性能和可扩展性。这些 GAA 晶体管包括纳米片结构场效应晶体管 (NSFET)和纳米叉结构场效应晶体管 (NFFET)(图 1c-f)。在 NSFET 中,栅极环绕整个沟道,以优化静电控制和器件性能。在NFFET中,为了提高集成密度,牺牲了部分栅极静电特性和性能。在 NFFET 中,这种权衡是通过将一种横向栅极氧化物替换为隔离氧化物来实现的,隔离氧化物用于电隔离两个相邻放置的互补 (p/n) NFFET。 2D TMD 的高度各向异性结构特性可产生较大的沟道宽度与沟道厚度比,这种特性也可以独特地用于设计本文介绍的 2D 纳米板 FET(NPFET),这是一种更广泛的 GAA 金属氧化物半导体 FET,可在更小的占用空间下实现更高的能效和性能。然而,探索这种 3D 器件架构需要进行全面的设计空间分析,包括理想的器件结构和通道材料的选择。

在本文中,我们报告了一种基于 3D 非平衡格林函数 (NEGF) 量子传输形式的模拟方法,其材料输入来自第一性原理密度泛函理论 (DFT) 计算,以帮助指导使用 2D TMD 进行缩放 3D 晶体管的设计。我们将这些器件称为 2D NXFET,其中 N 代表纳米,X 表示沟道形式(例如片、叉或板)。我们的方法考虑了量化效应、边缘电场和具有接触电阻RC的非理想肖特基接触。它可以准确评估 NXFET 中的电流和电容(跨横向和垂直栅极,包括寄生效应)的性能指标,并考虑精确的层数相关的 2D TMD 材料物理。

我们对基于单层/多层 2D-TMD 的 NXFET 进行了性能/可扩展性评估,并进行了设计优化,以最大程度地提高性能和能效。我们还针对 NXFET 的硅实现进行了性能预测。这些突出了 2D NXFET 架构在低待机功耗 (LSTP) 和高性能 (HP) 应用的节能计算方面的优势,以及在 5 纳米沟道长度之后仍能维持摩尔定律的优势。这些优势被证明可以转化为卓越的电路性能,为 2L 二硫化钨 (WS2 ) 沟道提供超过 51% 的能量延迟积 (EDP) 改进,并且即使在存在肖特基接触的情况下,也可以使用 3L WS2获得进一步的改进。

NXFET 架构仿真

NXFET 架构参考了 GAA 3D 设计,其凸起的源极漏极区域连接到多个垂直堆叠的沟道,所有沟道均由全包围栅极控制。栅极电极通过电介质间隔物与源极和漏极横向隔开,这有助于提高工艺公差,但会增加访问电阻和寄生电容。源极和漏极区域经过掺杂,而沟道保持未掺杂,电导仅由栅极调制。栅极氧化物和金属厚度(t

metal)的变化以及沟道数量用于估计最佳器件性能(包括接触电阻考虑因素)。Si 器件中的通道厚度假设为 4nm 或 6nm ,而 2D TMD 实现取决于 TMD 层数,对单层、双层和三层厚度(分别为 0.66/1.29/1.93nm)进行了模拟,这是 4 年来首次研究,尽管是针对双栅极架构。用于标准化导通电流的关断电流遵循国际器件与系统路线图 (IRDS) 预测,对于 LSTP(在 IRDS 中也称为高密度)和 HP 应用分别为100 pA µm–1和 10 nA µm–1 。虽然在主要模拟中使用SiO2作为电介质,但稍后也会考虑高κ HfO2。原子层沉积生长方面的最新进展使得纳米片沟道上的栅极电介质全面覆盖成为可能。

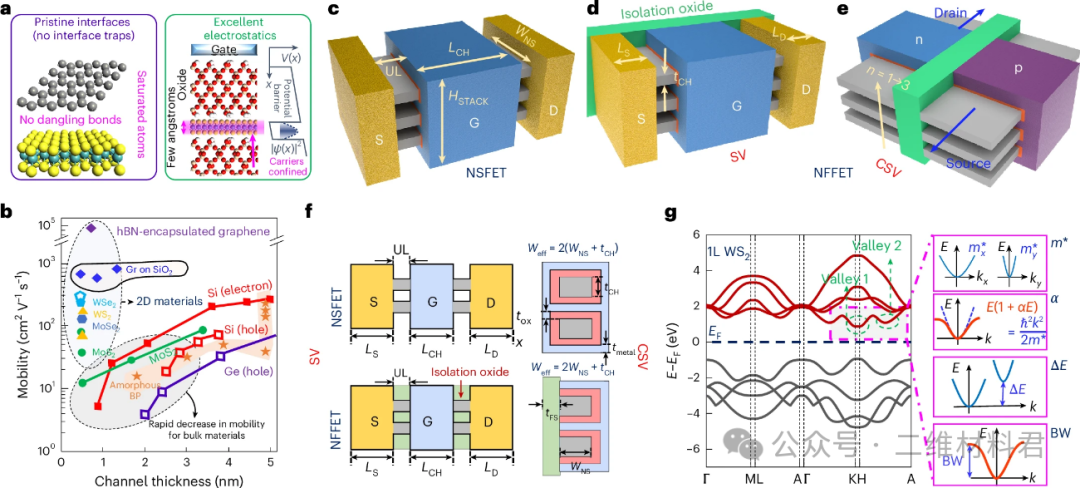

使用 Synopsys QTX 中的 NEGF 形式模拟了器件的性能,包括电流和电容特性(通过使用 Synopsys Sentaurus Device 计算小信号导纳矩阵来提取电容)。 使用 Perdew-Burke-Ernzerhof 广义梯度近似交换相关函数,从 Quantum ATK中的DFT 中的能带结构模拟中提取了有效质量和带隙等参数(图1g显示了 1L WS2的能带结构;补充说明2和补充表1显示了 NEGF 参数)。 NEGF 模拟用于模拟弹道传输,在源极、沟道和漏极之间构建了基于多谷有效质量的系统哈密顿量(图2a、b显示了整个器件的能带结构;补充说明3和补充图1讨论了图2a、b中的静电势下降)。补充说明4和补充图2讨论了 NEGF 网格中的离散化步骤。实际迁移率值表明,即使在沟道长度低于 10 nm 且迁移率为 100 cm2V–1s–1时,传输仍主要保持弹道状态(~75%) (图2c)。还提取了考虑寄生场和边缘场的电容。最后,使用 HSPICE 模拟评估了 EDP 和延迟等电路级指标,并使用根据 NEGF 传输特性校准的 2D FET 紧凑模型。性能指标是从 15 级环形振荡器 (RO) 网络中提取的。最后,有关模拟框架的所有其他相关细节都可以在方法中找到。

图 2:最佳 2D NXFET 沟道材料。a、电流谱或电流谱密度图,计算了 3L WS2 NSFET(n = 1)的LCH = 10 nm,显示最大电流谱密度为 6 × 10–5 AeV–1,峰值电流密度刚好超过源极-沟道能垒。电流还流过 CB 最小值顶部附近的能垒,突出了带内隧穿。E

FS和EFD分别是源极和漏极费米能级。b 、器件的局部 DOS(材料空间特定点的电子态密度)图显示凸起的源极和漏极处的 DOS 较大。c、对于采用 1L MoS2 ( L CH = 7 nm)实现的双栅极 2D FET,对于 弹道传输和扩散传输(迁移率( μ )为 10、50、100 和200 cm2 V–1s–1 ),比较以W(W = WNS )为标准的漏极电流(I DS),结果显示,对于 100 cm2 V–1s–1(0.6 mA μm–1 )的实际迁移率,弹道传输(0.8 mA µm–1 )和扩散传输之间的导通电流略有不同。d – f ,对于固定关断电流 100 pA µm–1 ,比较 1L(d)、2L(e)和 3L(f)2D TMD NSFET 的传输特性。由于DOS较高,导通电流随层数增加而增加。d – f中的模拟假设单个(n = 1)NSFET 通道,其中L CH = 10 nm 、W NS = 5 nm、UL = 1 nm(无间隔电介质)、NSD = 1014 cm–2、SiO

2电介质的氧化物厚度(tox )(沿横向和垂直方向)为 0.5 nm、LS = 5 nm、LD = 5 nm、RC = 0 Ω μm 且VDS = 0.4 V。

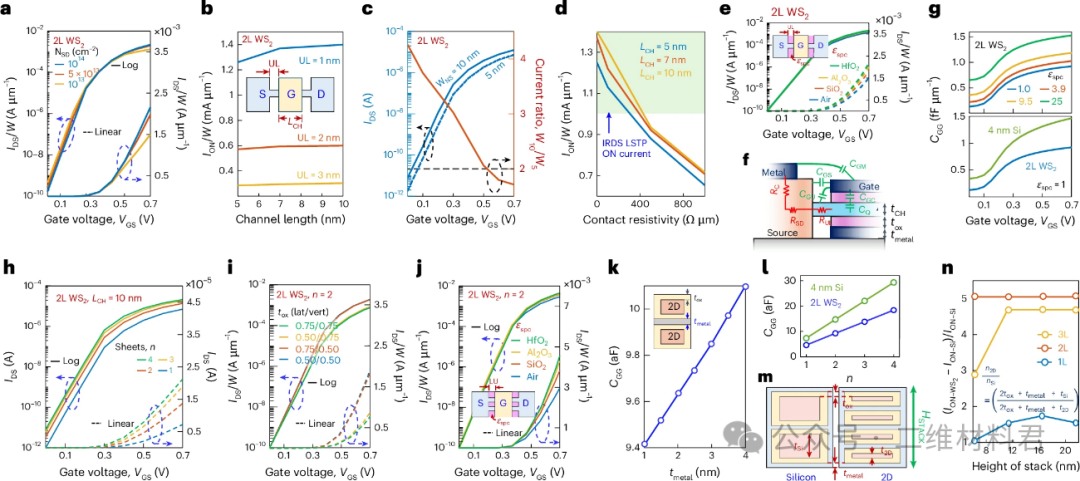

利用开发的模拟框架,针对 LSTP 和 HP 应用模拟了使用具有不同层数和通道厚度的 2D TMD 实现的 2D NXFET 的各种器件配置的电流-电压和电容特性。除非另有说明,所有模拟均假设V DS固定为 0.4 V,工作电压 ( V DD ) 为 0.7 V。因此, 一旦 OFF 电流固定为V GS = 0 V 和V DS = 0.4 V 时的 LSTP/HP 值,则 ON 电流将在VGS = 0.7 V 和VDS = 0.4 V 时提取。单个器件中 OFF 电流的选择是通过栅极金属功函数 调整器件阈值电压 ( VT ) 来确定的,n 型 NXFET 中较大 (较小) 的VT转化为较小 (较大) 的 OFF 电流,因此静态功率耗散较小 (较大)。但是,较大的VT也会降低器件的过驱动电压(对于固定的亚阈值摆幅 (SS)),该过驱动电压由VDD – VT决定,从而限制了导通电流,而较小的V T则通过提高过驱动电压来增大导通电流。因此,LSTP 器件的性能更多地受亚阈值(亚V T)传输特性的限制,而主要受器件静电的影响,而需要较大导通电流的 HP 器件的性能则受较大注入速度、DOS、迁移率(用于扩散传输)和较小串联电阻(跨晶体管栅极-源极-漏极欠重叠长度 (UL))的限制。请注意,使用V DS = 0.4 V 可提供代表性的V

DS来测量晶体管的线性电流(I DLIN,在V DS = 0.05 V 时测量)和饱和电流(I DSAT,在V DS = V DD时测量),这两者都是器件特性最相关的两个指标。最后,我们注意到,每当将 2D NXFET 的漏极电流与 Si NXFET 进行比较时,电流都会被标准化为每个堆栈的栅极宽度 (GW) (GW = 2( W NS + t CH );图1提供了相应晶体管的参数定义),实际上是单堆栈沟道上栅极电介质覆盖的总周长。这种标准化对于准确估计性能(即导通电流与器件电容之间的关系)至关重要,特别是因为与 1L、2L 或 3L 2D TMD(0.66/1.29/1.93 nm)相比,沟道更厚(4/6 nm)的 Si NXFET 可以承载更多电流,但器件电容更高。因此,对整个 GW 上的导通电流进行标准化可确保在等效器件电容下进行比较,从而提供一致的性能指标。但是,当比较 2D NXFET 的各种设计和晶体管配置的电流时,已根据晶体管通道占用空间(W)对其进行了标准化,即纳米片宽度(W NS;W = W NS),以准确评估集成密度。此后,以 GW 和纳米片宽度为标准的电流分别称为IDS /GW 和IDS /W。

2D 材料选择

图2中绘制了 用于 LSTP 应用(关断电流为 100 pA µm–1 )的1L、2L 和 3L 基于 2D-TMD 的单堆栈(n = 1)NXFET(X = 薄片)的归一化导通电流,用于评估所选材料,以提供最高导通电流(在恒定关断电流下)。电流归一化是通过将漏极电流除以晶体管占用面积(W)来实现的。显然,1L WS2(图2d)、2L WS2(图2e)和 3L WS2

(图2f)在 1L、2L 和 3L 同类材料中提供最大的导通电流,从而成为首选材料。这是因为,尽管WS2的中等有效质量(1L 中约0.33 m0)有助于提高I ON值,这是由于载流子注入速度(与有效质量成反比)和 DOS 的改善,但其大带隙(1L 中约 1.8 eV)以及中等传输有效质量最大限度地减少了源漏直接隧穿(缩小晶体管中I OFF的主要机制),从而导致开-关电流比超过七十个数量级。虽然 1L WS2 NSFET 的开电流为约 0.4 mA µm–1,但 2L 和 3L 样品的开电流可能高得多,分别约为 1.5 和 2 mA µm–1(图2),因此 3L WS2是HP 和 LSTP 应用的实用选择。在确定最佳材料选择后,与 Si 实现进行了性能预测,如下一节所述。

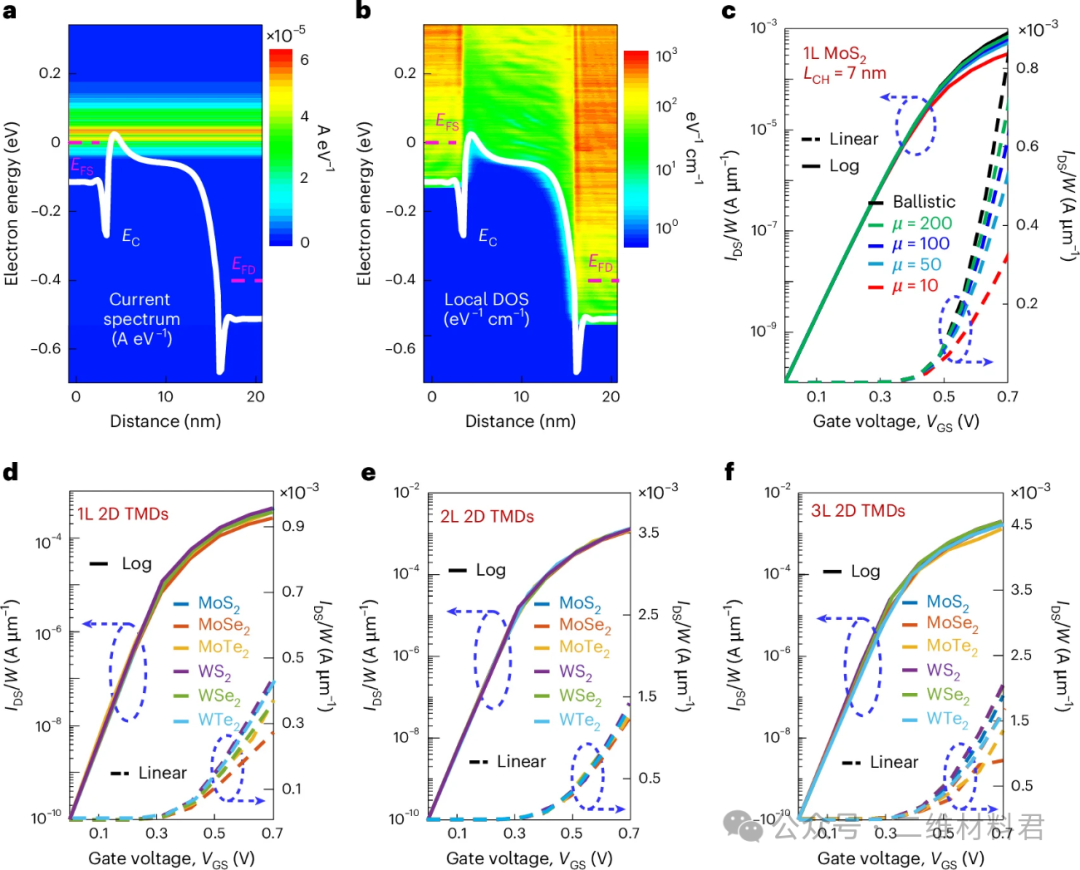

图 3:沟道长度缩放以及模拟和数字性能的比较。a、b、对于 LSTP(a)和 HP(b)应用,1L、2L 和 3L WS2 NSFET 与 tCH 为 4 nm 和 6 nm 的 Si NSFET 之间的 ION (归一化到有效器件 GW) 比较,显示2D WS2 (特别是2L 和 3L WS2 )相对于 Si 具有优异的性能,对于 LSTP 和 HP, L CH分别低于 9 nm 和 7 nm。ION随着LCH 的缩小而降低(对于固定的IOFF),因为较小的沟道长度会降低开关比(由于较差的静电和增加的源漏直接隧穿)。c 、 d 、2L WS2 相对于 Si(对于 tCH = 4 nm 和 6 nm)的 SS(c)和 DIBL(d

)计算显示,由于出色的静电介导 栅极控制,2D NSFET 具有优异的性能。尽管对于 WS2 来说, SS 几乎恒定在 ~60 mV dec–1的理想值,但是 Si 的较差静电性能会在L CH < 9 nm 时大幅降低 SS。同样,无论L CH如何,2L WS2中的 DIBL在 ~50 mV V –1时 也非常出色(因为静电性能良好)。e , f , 在 VGS = 0.4 V(饱和开始)下,比较 1L、2L 和 3L WS2 NSFET(n = 1 )与 Si NSFET(tCH = 4 nm)的跨导( gm) (e)和跃迁频率(f T ) (f),结果显示,由于跨导大幅下降和电容增大,10 nm 以下沟道长度的 Si 性能严重下降。CGS表示栅极-源极电容,等于总栅极电容的一半。除非另有说明,所有模拟均假设n = 1、W NS = 5 nm、UL = 1 nm、N SD = 1014 cm –2(2D)和 10 21 cm –3(Si),EOT(SiO2沿横向(垂直于t CH)和垂直方向(垂直于WNS)的介电常数(ε)为 0.5 nm,LS = 5 nm,LD = 5 nm,RC = 0 Ω μm 且V DS

= 0.4 V。

开态电流评估和沟道长度缩放

图3a、b比较了1L、2L 和 3L WS2 NSFET 的归一化(相对于 GW)I ON ( I OFF = 100 pA µm–1 ) 与n = 1 且沟道长度从 5 到 12 nm 不等的 Si 对应物。尽管由于横向电场的增强,I ON会随着沟道长度的减小而增大,但是在较短沟道长度下静电性能的降低会伴随有I OFF和 SS 的严重下降,从而导致在I OFF固定的情况下I ON下降。在这方面,2D WS2相对于 Si的优越静电性能以及更大的带隙和有效质量(沿传输方向)可使 SDTL 最小化,尤其是在低LCH时,从而降低I OFF并相应地增加I ON。虽然在LCH = 9 nm以下的 LSTP(图3a)应用中,2L 和 3L WS2的性能均优于 Si(t CH = 4 nm),但3L WS2 在所有沟道长度下都具有最大的I ON,这使其成为实现 2D NXFET 的理想选择。6 nm 沟道厚度的 Si 表现出最差的静电,导致I OFF较大,因此I ON最小。虽然 Si NSFET在

I OFF要求不太严格(10 nA µm –1 )的 HP 应用(图3b )中表现更好,但当沟道长度小于 7 nm 时,其性能会下降,而 3L WS2仍然更胜一筹。因此,3L WS2是LSTP 和 HP 应用的首选材料。尽管图3a、b是在V DS = 0.4 V 下模拟的,但使用更高的V DS = V DD = 0.7 V 会在较长的沟道长度下(由于 DOS 较大)为 Si NSFET 提供更高的电流(相对于 2D NSFET),并且由于短沟道效应的增加,在较短的沟道长度下性能会下降。更多详细信息请参阅补充说明5和补充图3。值得注意的是,尽管我们的模拟没有考虑界面态对 Si 和 2D NXFET 性能的影响,但考虑这些状态可能会导致 Si NXFET 的性能比 2D NXFET 的性能下降更多。这是因为像 Si 这样的 3D 块体半导体在沟道宽度和厚度方向上都有边缘状态,而 2D NXFET 的边缘状态只存在于横向方向(即边缘方向)(2D 材料的顶部和底部表面完全终止,因此没有悬空键)。事实上,据报道34 2D TMD 沟道(宽度高达 25 nm)中的边缘状态的影响提高了器件性能,而不是降低了器件性能,因为它通过增加局部电场增加了有效电荷载流子数量,而不会因边缘相关散射而导致性能下降。因此,考虑这些边缘状态甚至可能会增加 2D NXFET 和 Si NXFET 之间的性能差异。此外,2D 材料的较薄体使这些边缘状态与整个器件宽度的比例最小化,从而减轻了这些边缘状态的影响。例如,在沟道宽度和厚度分别为 10 nm 和 1.9 nm 的 3L 2D-NSFET 中,在 23.8 nm 的总器件宽度中,只有约 3.8 nm 具有边缘状态,而 Si NSFET(体厚度为 4 nm)的整个器件宽度为 28 nm,边缘状态都存在。最后,表面钝化技术已成功用于 Si 晶体管35,以提高迁移率,最大限度地减少表面散射和滞后现象,将来经过适当修改后,也可以适用于钝化 2D 材料的边缘状态,以进一步提高性能。

与 Si NSFET 相比,NSFET 中的 WS2 具有更优异的性能,这还带来了出色的 SS(图3c)和最小的漏极诱导势垒降低 (DIBL)(图3d),这些指标与数字电路设计有关。尽管 2L WS2 的 SS 和 DIBL不受沟道长度缩放的影响,但即使是对 4 nm tCH的 Si NSFET 进行乐观的弹道模拟,也显示出 SS(>100 mV dec –1)和 DIBL(~250 mV V –1 )的严重退化。由于相关的表面粗糙度和陷阱态散射,预计实际的 Si 性能会更差。在跨导( gm )(图3e)和过渡频率(fT )(图3f)的模拟性能指标中,也观察到了Si的类似下降,其中Si中gm的下降将fT

限制在10GHz(在峰值fT偏置点),在LCH = 5nm处,与2DWS2 相比,下降了30倍。虽然gm是晶体管增益的度量,但过渡频率决定了晶体管电流增益降至1的频率。因此,较大的fT意味着晶体管在较大的工作频率下提供较高的电流增益。因此,缩放的2D NXFET对于模拟和数字电路实现都非常有前景。

单栈优化

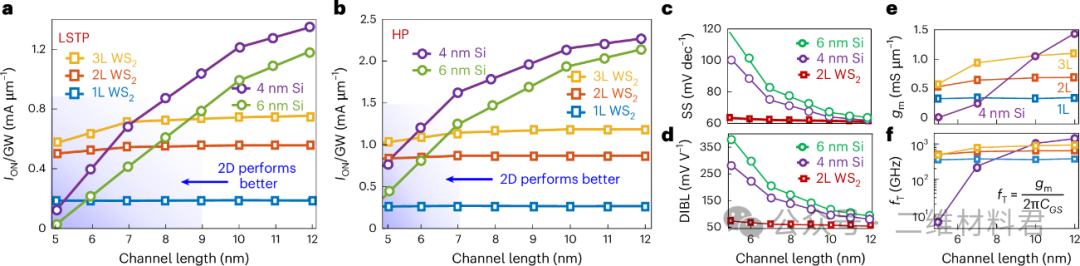

单堆栈 ( n = 1) 器件优化(图4)可提高所设计的 NXFET(X 表示片、叉或板)的整体性能。较大的源漏掺杂浓度 ( NSD ) 会下推源漏能带(相对于 n 型掺杂的固定费米能级 ( E F )),而沟道中的能带则由栅极偏置保持恒定。因此,这会增加从源极到沟道的电流注入屏障(在固定栅极金属功函数下),从而降低IOFF(图4a)。此外,源漏界面上的访问电阻得到改善,从而改善了ION。因此,虽然较大的源漏掺杂浓度会改善开关电流比,但大于 1014 cm–2 的掺杂浓度接近 2D TMD 中的固溶度极限,从而使NSD = 5 × 1013 cm–2成为目标掺杂浓度,超过此浓度掺杂效益也开始饱和。还必须注意,如果掺杂浓度进一步降低,即降低至 1013 cm–2 ,导通电流的下降幅度会很大 (~25%) 。最后,值得注意的是,虽然已经发现这种选择性掺杂浓度可以在 2D 材料中实现,但对源漏区使用电导率更高的材料也是实现更高性能和更低串联电阻的潜在解决方案,即使在低掺杂浓度下也是如此。类似地,尽管通过最小化下重叠部分的串联电阻 ( RUL ),降低 UL 可以改善ION (图4b ),但过低的 UL 不仅会增加器件对短沟道效应的敏感性(也会增加寄生栅极-源极-漏极电容),因为从漏极到源极的横向电场更强,而且还会使器件容易受到工艺变化的影响,其中凸起的源极-漏极区域可能与栅极金属区域重叠。因此,2nm 的 UL 是首选。由于 Si NXFET 的 OFF 电流较大,因此 ON 电流随 UL 的变化更为显著。补充说明6(补充图

4)中给出了等效分析。然而,纳米片宽度 ( W NS ) 不仅决定了载流截面,还影响静电 (图4c ),其中较小的WNS改善了静电性能(通过改善横向栅极的静电通道控制)。这会导致I OFF降低而I ON增大(以 GW 为标准),从而改善开-关比。尽管W NS对I ON的影响在 2D NSFET 中影响相当有限,但它对 Si NSFET 性能的影响更大,因为 Si NSFET 的主体更厚,会降低静电性能(补充说明7和补充图5)。这导致 2D NSFET在更现实的纳米片宽度W NS = 20 nm 下更全面地优于 Si NSFET( t CH = 4 nm),因为通道长度减小到 10 nm 以下。然而,除了决定晶体管性能的沟道电阻之外,NXFET 中与凸起的源漏结构的低效接触也会影响器件性能,特别是在较短的沟道长度时。此时沟道电阻相对于接触电阻最小,从而使后者成为器件性能的限制因素。在这方面,对具有不同R C值和不同沟道长度的 NSFET 的I ON进行模拟(图4d),结果表明,R C < ~400 Ω μm 是实现I ON大于 1 mA µm –1的IRDS 性能指标的必要条件。在这方面,在确定最佳金属半导体材料和接触配置以及实现最小 RC方面取得的最新进展很有希望。具体而言,与半金属Sb (用于 n 型接触)的2D TMD 的混合接触似乎是最优的。通过精心设计隔离层, I ON仍可得到改善(图4e),高κ

隔离层可通过边缘栅极场线提供对R UL的更高有效调制(图4f),但代价是电容增加(图4g,顶部)。事实上,虽然将介电隔离层从空气(ε spc = 1)替换为二氧化铪(ε spc = 25)可改善I ON增加约 40%,则会导致器件电容增加约 66%,从而降低器件的整体性能。此外,由于 2D TMD 的体厚度和介电常数相对于 Si 有所减小(WS2 /Si 的相对平面外介电常数为 5/12),2D NSFET 的整体器件电容比 Si NSFET(图4g,底部)小约 60%,从而进一步提高了性能增益。最后,电介质的物理厚度(对于恒定的等效氧化物厚度 (EOT))也在调节器件的性能方面发挥作用,特别是对于较薄的沟道厚度,因为它调节跨电介质的边缘源漏电场线的数量,从而调节沟道静电。具有相似 EOT 0.5 nm 的 HfO2电介质的结果在补充说明8(补充图6 )中给出。

图 4:单堆和多堆纳米片结构的优化。a 、 n = 1、2L WS2的晶体管封装归一化漏极电流比较(其中WNS = 5 nm、LCH = 10 nm、UL = 1 nm 和 EOT = 0.5 nm),结果表明ION随着N SD 的提高而增大,从而提高了性能。b 、对于 2L WS2,在IOFF = 100 pA µm –1固定的情况下,随着L CH的变化,ION/W随 UL 长度(1 nm、2 nm 和 3 nm)的增加而减小。c 、W

NS = 5/10 nm的2L WS2的漏极电流 表明,随着沟道变宽,ON-OFF 比会降低,如 WNS = 10 nm(W 10)与 5 nm(W 5 )的电流比( V GS = 0 V 附近的OFF 电流和V GS = V DD附近的ON 电流)所示。还显示了对应于比率 2(具有理想静电的通道的导通电流比)的黑色虚线。d 、对于L CH = 5 nm、7 nm 和 10 nm , I ON / W衰减随R C的变化表明, RC < 400 Ω μm 对于满足 IRDS LSTP I ON要求(>1 mA µm –1 ) 至关重要。e 、对于n = 1、2L WS2(其中WNS = 5 nm 和LCH = 10 nm), ION /W随间隔层介电常数(ε spc )的增加而增加。f 、寄生元件,包括R C 、源极-漏极扩展(R SD

)和 UL 电阻,与寄生电容CQ、CGS、CGM、CGC和CGU(即分别为量子、栅极源、栅极金属、栅极通道和栅极 UL 电容)一起示出。g、宽度归一化净电容(CGG )比较表明,较高的εspc增加了器件电容(顶部),但与 Si tCH = 4 nm相比,2L WS2 的电容始终较低。h ,转移特性表明,将2L WS2中的薄片数量(n )从 1 增加到 4会增加漏极电流。i ,与较厚的横向栅极氧化物t ox ( lat )相比,较厚的垂直栅极氧化物t ox (vert ) 会显著降低整体静电性能,使 SS 和I ON均恶化。j ,高κ间隔物增强了栅极边缘电场线,降低了R UL并提高了纳米片(n = 2)的I ON ,但代价是增加了C GG。k ,减小的金属厚度会 通过降低整体器件高度来降低n = 2 纳米片中的C GG 。l ,由于主体更薄且介电常数更低, 2L WS2中的C GG低于 4 nm t CH Si,从而提高了性能。m ,与 Si 同类产品(n Si堆叠层)相比,原子级厚度的 2D NSFET 能够在相似的垂直(H STACK )和横向占用空间内实现更多堆叠纳米片( n 2D ) ,从而产生更大的I ON。n ,随着t CH = 4 nm, n Si从 1 增加到 4 ,绘制了 2D 纳米片相对于 Si 的 ION改善比率,这对应 于H STACK的增加。可实现的n2D/nSi比率如插图所示。模拟假设n = 1 NSFET,具有 2L WS2沟道,L CH = 10 nm(对于n为 5 nm ),W NS = 5 nm,UL = 1 nm(无间隔电介质),