广告

目录

1.Socionext推出神经网络加速器,加速AI时代

2.中移物联China Mobile Inside首款“4G+eSIM"芯片于广州发布

3

.

大联大品佳集团力推Nuvoton电子智能锁解决方案

4.

Semtech的LoRa技术被集成到群登科技(AcSiP)面向物联网应用的模块之中

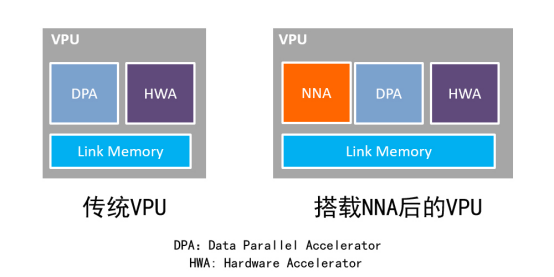

Socionext推出神经网络加速器,加速AI时代

先进视觉影像SoC应用技术领导厂商Socionext Inc.(以下“索喜科技”或“公司”)宣布推出神经网络加速器 (Neural Network Accelerator engine,缩写NNA),用于优化人工智能处理中的边缘计算设备。它具备高速且低功耗的特性,是专用于深度学习中推理处理的加速器。相较以往的处理器,NNA在图像识别等处理时性能提升约100倍。公司预计于2018年第三季度开始,配合FPGA软件开发工具提供产品销售。此外,搭载有NNA的SoC产品开发也正在规划当中。

随着消费电子、汽车电子、工业控制等越来越多的应用引入人工智能(AI),人工智能面临着前所未有的快速发展,深度学习、神经网络等技术迎来了发展高潮。神经网络越大,需要的计算量就越大,传统的VPU虽然也能完成人工智能运算,但因为高功耗和高延迟已经略显疲惫。在VPU上加载人工智能计算能力则可以规避这些问题,而且具有更高的可靠性。

Socionext目前提供图像处理SoC“SC1810”,这款芯片内置有技术标准化组织Khronos Group制定的API规范-OpenVX,内置有视觉处理器(VPU,Vision Processor Unit)。此次新推出的NNA加速器能VPU性能,可在汽车、数字标牌等多种应用中通过深度学习及传统的影像识别执行多种电脑视觉处理,以便在较低功耗下提供更高的性能。

NNA采用量化技术整合了公司的专有构架,减少了深度学习所需的参数和激活值。通过量化技术能以较少的资源执行大量计算任务,大幅减少数据量,并显著降低系统存储器带宽。此外,新开发的片上存储器电路设计提高了深度学习所需的计算资源效率,能在非常小的封装中实现最佳性能。搭载有NNA的VPU结合了最新的技术,能在图像识别处理时比传统VPU快100倍。

Socionext预计于2018年第三季度开始提供NNA FPGA软件开发包。改软件开发包可支持TensorFlow学习环境,并提供用于量化技术的专用库和从学习模型到推论处理用的数据转换工具。通过利用NNA优化后的学习环境,用户无需模型压缩或学习调谐(learning tuning)知识也能有效建立起他们自己的模型。今后Socionext还将计划通过支持各种深度学习框架来支持应用广泛的开发环境,让用户能简单建立深度学习的应用程序。

与此同时,Socionext也计划将载有NNA的SoC芯片投入市场。目标应用包括车载系统中的影像拍摄,以及基于行人、自行车等高精度物体识别的辅助驾驶以及自动泊车。另一个重要的应用便是显示系统,例如电视、数字标牌,NNA可在超分辨率处理时增强图像识别,提高4K/8K屏幕高清晰度成像。Socionext将不断创新并开发出高效、高性能产品,以适应各种边缘计算环境中广泛的AI应用。

中移物联China Mobile Inside首款“4G+eSIM"芯片于广州发布

中移物联于2018年5月25日正式推出智能物联China Mobile Inside计划,同时发布国内首款芯片提供“芯片+eSIM+连接服务”,并于广州移动召开发布会暨产业合作签约仪式。

基于China Mobile Inside 嵌入式芯片(即内置eSIM的核心芯片或套片),可以在工业制造技术、生产周期、行业能力整合、终端补贴等多方面发挥更多优势。

China Mobile Inside计划推出的首款C417M系列芯片,是中国移动自主品牌,与紫光展锐合作研发,主要特性是集成中国移动eSIM功能,支持空中写卡,在最大程度降低终端体积的同时,可避免部署场景环境恶略或震动等造成SIM卡接触不良、无法通信的情况,进一步提升芯片的稳定性。该系列芯片集成中国移动SDK,可无缝接入中国移动物联网开放平台OneNET,帮助企业实现上层应用快速和低成本研发。此外,芯片自带的FOTA功能使得产品在投放后可持续进行功能增强和问题修复。此次发布的芯片包括C417M-S和C417M-D两款,均支持中国移动以及全球运营商的主流LTE频段,支持蓝牙、Wi-Fi、FM和GNSS多模卫星定位等功能,满足蓝牙通话、音乐播放和定位导航等多种实用场景需求。从芯片级对eSIM封装,其可靠性更高,对于恶劣环境的耐受能力更好。终端厂家采购的通信芯片中直接嵌入eSIM功能,简化了生产流程。同时终端厂家也无需分别对接芯片厂商和运营商,有效降低沟通成本,且可以更高效的保障通信信息安全,将在车联网、智能穿戴、工业设备监控等领域发挥重要的作用。

中移物联通过China Mobile Inside嵌入式芯片,联合广州移动,为产业链合作伙伴提供芯片及终端补贴计划,有效地降低开发成本和行业准入门槛,同时降低产业链的生产及运营成本,让利于物联网产业链,推进智能物联产业加速发展。

在内容和渠道运营方面,中移物联及广州移动将基于China Mobile Inside计划大力推动产业合作,为产业链合作伙伴及最终客户提供更多增值服务,包括在线实名认证能力、主号代付能力、终端管理能力、本地信息增值服务(保险、交通、教育等)。结合本地移动用户资源,发挥渠道能力,进一步推动产业合作和深度运营。

面向个人用户市场,广州移动推出“1+N”物联营销模式,推进"个人用户+物联网卡"的深度运营。结合China Mobile Inside定制芯片 ,探索"业务+终端"的产业模式。通过"1+N"营销模式为个人客户提供主号代付、在线办理、在线实名、在线支付、在线配送等端到端服务。降低客户的交易成本。同时,还将为参与China Mobile Inside计划的终端提供专项补贴,让利于消费者,让更多消费者感受物联网带来的便利生活。首期将推出针对私家车主的车主畅享包业务和针对智能穿戴类的亲子畅享包。其中车主畅享包用户每天只需支付1元,即可享受动态导航、语音交互、视听娱乐、报险救援等智能化服务。亲子畅享包用户每天只需支付1元,即可享受语音通话、精准定位、天气预报、运动计步等智能化服务。

在此次发布会上,中移物联集成电路创新中心与国产通信芯片龙头紫光展锐进行了合作签约,中移物联智能硬件中心和安畅星、研强、联想懂的、中通视际、驾控科技、东华星联等合作伙伴进行了合作签约。

Synopsys数字和模拟定制设计平台通过TSMC5nm工艺技术认证

全球第一大芯片自动化设计解决方案提供商及全球第一大芯片接口IP供应商、信息安全和软件质量的全球领导者Synopsys近日宣布, Synopsys设计平台获得TSMC最新版且最先进的5nm工艺技术认证,可用于客户先期设计。通过与TSMC的早期密切协作,IC Compiler ? II 的布局及布线解决方案采用下一代布局和合法化技术,最大限度地提高可布线性和总体设计利用率。借助重要的设计技术协同优化工作,通过使用PrimeTime?Signoff和StarRC?提取技术实现ECO闭合,IC Compiler II 实现了对高度紧凑的单元库的支持。对于TSMC 5nm极紫外光刻(EUV)技术来说,通过部署非缺省规则处理和布线层优化的通用技术,最大限度地提高了寄生优化的新机会,从而创建出高度收敛的RTL-to-GDSII实现方案。

PrimeTime时序分析和Signoff认证解决方案中的先进技术,已扩展到整个数字实现平台,以实现面向TSMC 5nm工艺节点的快速增长市场的差异化设计。PrimeTime中的参数化片上偏差 (POCV) 分析得到了加强,可精确获取由于工艺缩放和低电压运行而导致的非线性变化,而这些手段过去常用于实现上述目标应用的能源效率。

TSMC 5nm认证还包括IC Validator物理验证Signoff,支持DRC、LVS和金属填充。TSMC发布设计规则的同时也发布运行集。TSMC和 Synopsys 之间的深度技术合作可实现先进的工艺特性,如新的多网格填充优化和LVS双层次抽取。

为了加速可靠的模拟定制和数模混合信号设计, HSPICE?仿真器以及 CustomSim?和 FineSim? FastSPICE 仿真器也都进行了优化,可支持TSMC 5nm FinFET工艺。该解决方案结合CustomSim先进的IR/EM 可靠性分析能力,加快了AMS验证,以支持可靠的AMS设计。

TSMC设计基础架构营销事业部资深处长Suk Lee表示: “我们与Synopsys在5nm工艺的合作可以为客户在设计过程中带来更高性能和更低功耗。为帮助客户在5nm工艺技术的支持下实现目标PPA,TSMC和Synopsys一直在广泛的设计风格上展开合作,以推动并让设计性能实现最大化。”

Synopsys设计事业群营销和业务开发副总裁Michael Jackson表示:“考虑到5nm工艺技术在规则和进步方面的复杂性,我们必须进一步提早开始与TSMC的合作周期。此外,我们还必须提早开始与早期5nm技术采用者的接触。新工艺节点正在以前所未有的速度引入,我们与TSMC的合作确保了企业设计人员能够在新节点上满怀信心地设计,同时最大限度地提高他们的投资回报。”

TSMC可提供Synopsys Design Platform技术文件、库和寄生参数,以便在5nm技术工艺中进行先期设计。获得TSMC5nm FinFET工艺认证的 Synopsys Design Platform的主要产品和特点包括:

· IC Compiler II 布局和布线: 全自动、全着色布线及抽取支持,下一代布局和合法化技术以减少单元占板面积缩小,实现高设计利用率的高级合法化和引脚访问建模,以及实现通孔柱技术的流量部署,最大限度提高性能和器件产量;