来源:半导体行业观察翻译自semiengineering,作者MARK LAPEDUS

,谢谢。

数年前,许多人都预测,引线键合技术这种传统的互联封装技术会消亡,并且会推动了对更先进的封装技术的需求。事实证明,这些预测错了。

当下,半导体制造业确实使用着几种先进的封装类型,但是引线键合技术已经经历了多年的重新改造,并且仍然是封装的主力。例如,全球最大的封测代工厂(outsourced semiconductor assembly and test,OSAT)——台湾日月光半导体制造公司(ASE),现在具有一个近16.000台焊线机的安装基地,能够生产多种封装类型,引线键合就是其中的主力。

20世纪50年代发展起来的引线键合机(焊线机),类似于高科技缝纫机,能够利用极细的线将一块芯片缝到另一芯片或衬底上。引线键合技术主要用于低成本的传统封装,中档封装,内存芯片堆叠等。

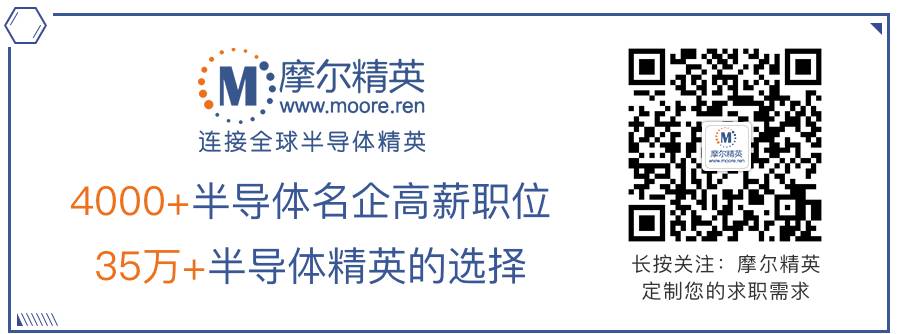

图 1:超小间距的引线键合。来源:库力索法(Kulicke & Soffa.)

当下,在激增的传统应用如汽车,以及新的细分市场如3D NAND领域,引线键合市场正在升温。同时,引线键合也被用在高级封装中,正如TechSearch International(TSI)的总裁Jan Vardaman所说,“现在大约有75%到80%的封装类型仍然是引线键合的。虽然增速是个位数,但是确实仍有增加的部分。例如,闪存、某些新型传感器都会用到键合线,一些封装实际上有内置的键合线和倒装芯片。”

然而,引线键合技术有它自己的局限性。它不可能掌控IC封装世界,因为该技术有一些众所周知的I / O问题。对于许多高性能芯片来说,引线键合技术确实走到尽头,客户将需要更先进的封装类型。

事实上,一些基于引线键合的传统应用正在往更新的封装类新迁移。引线键合技术不会停滞,而工具也在继续升级。台湾ASE设备工程副总裁Scott Chen声称,“键合线将继续发展,尤其是铜线键合。”

总之,预测引线键合技术的消亡确实太言过其实了。“在某些硅节点,不能简单地采用高级的封装,如倒装芯片和晶圆级,” 星科金朋负责产品和技术市场的副主任Edward Fontanilla如是说,“考虑到成本和可靠性,键合线具有相当的优势。”

虽然芯片客户已经习惯了引线键合的能力和局限性,但是,许多人正在寻求有竞争力的技术。为了帮助业界了解引线键合的发展方向,半导体工程公司已经看到了技术和一些关键市场,特别是智能手机领域。

什么是引线键合?

分析师称,引线键合是一个成熟的市场,预计从2014年到2019年将仅增长2.4%,尽管如此,引线键合封装市场仍然大有可赚,据悉,该市场每年约产出130亿美元至150亿美元。

模拟和汽车这两个最大的引线键合驱动因素,每年都以3.9%的速度增长。分析师补充说,计算领域的应用将下降6.6%,但传感器却增长了15.2%。

引线键合是封装中的主要互连技术之一。 其他的技术还包括倒装芯片,晶圆级封装(WLP)和硅通孔(TSV)。

封装是一种根据终端类型定制化的行业。在高端设计中,行业继续采用TSVs技术加强2.5D/3D芯片的设计;在中档到低端应用中,客户采用WLP技术,如扇入(fan-in)和扇出(fan-out)。WLP是在晶圆上进行的IC封装。

在倒装芯片中,在芯片的顶部形成大量微小的凸起或铜柱。该装置翻转并安装在单独的模具或板上。模具或板由铜垫组成。凸起或铜柱落在铜垫上,形成电气连接。

图 2:倒装芯片BGA封装。来源:UTAC

引线键合是一种最古老、最低成本的互联方案,它利用来自ASM Pacific,K&S等的引线接合器进行焊接。焊线机被用于制造各种封装类型——BGA、PDIP、QFN、SOIC、TSSOP等。

基本上,有两种主要类型的焊线机——球键合和楔键合。“超过90%的市场使用球键合,”ASE的陈说。“楔焊用于离散产品和重型电线的电源设备。”

在一个简单的引线键合流程中,首先芯片附接在框架或基质上。然后,使用引线键合机将导线从系统中的线轴送入细管中。热量使得导线的末端形成一个小球。使用力,焊接机将焊球焊接在焊接面。该系统环绕着导线,然后将其缝合。最后,模塑材料覆盖电线。

图 3: TI的铜线键合工艺流程。

直到2010,行业内以引线键合为基础的封装主要使用的还是金线键合,但当金价飙升时,键合产品由金线向铜线转移。由于铜比黄金便宜,芯片制造商的封装成本得以降低。

虽然铜比金硬,但这又反过来需要更强的粘结力,这可能导致焊接盘的损坏。而且,铜在一定温度下会氧化。

今天,虽然有约70%的基于引线键合的封装使用铜线,但是剩余部分仍使用金线或者银线键合。“另外,银的成本高于铜,但低于黄金,”陈说。“大部分银线用于内存封装。”

金线键合在许多应用中仍然被使用。“有些应用比较保守。需要花更长的时间来认证,比如汽车,”他说,“他们需要更多的时间来证明该设备可以转换成铜线。对于某些设备,他们更是根本不想做任何改变。”

无论如何,引线键合是有限的。“它支持低引脚数器件引线键合,可以支持高达700至800个I / Os,但实际的引线超过1000线,”陈说。

十年前,用于引线键合的焊接盘间距限制在80至100μm。 随着时间的推移,引线接合器已经改善,使得焊接盘间距降为40至37μm。

Amkor公司负责微电子机械系统(MEMS) 、传感器和引线键合BGA产品的高级副总裁Adrian Arcedera表示:“焊线机器的不断改进,允许我们做的不仅是在焊接盘间距缩小时处理更小的导线直径,而且还可以使我们获得更好的循环控制。”

然而,焊线机需要在更精细的间距中执行更复杂的任务,这带来了吞吐量的挑战。“因为(引线键合机)以及有所改善,功能也提高了,”Arcedera说, “但是我们还在不断挑战机器。我们正在使这些机器在循环中进行一些弯曲或扭结。现在,我们又在放慢机器的速度。”

总而言之,客户有选择权。他们可以坚持使用引线键合,也可以考虑倒装芯片,可以选择WLP或TSV技术,或者对这些技术做一切可能的组合。还有一些人可能从引线键合转到其他技术。“有些客户正在从引线键合产品迁移到高级封装。有些需要更严格的可靠性,”星科金朋(STATS ChipPAC)的Fontanilla如是说,“我们也有层压板的引线键合,(有些可能)转换为高级封装,比如倒装芯片和晶圆级封装,这是对引线键合的威胁。”

探究iPhone7 内部

引线键合用于多种应用,其中,汽车是通常想到的典例。 “在汽车行业,我们使用标准设备和工艺流程的标准封装,”Fontanilla说,“汽车和商业市场之间的唯一区别就在于质量和过程控制方面。汽车在质量、流程和可靠性方面要求更为严格。”

汽车客户也不太愿意做出改变。给定的插座多年来可能都使用相同的芯片和封装类型。不过,事实上也并非总是如此,Fontanilla称“有些用户正在考虑高可靠性产品,如自动驾驶辅助系统(ADAS)。 他们可以使用晶圆级产品,而不是引线键合。”

然而,智能手机的故事却不尽相同。下一波智能手机将需要新的芯片,并将其安装在更小更薄的封装中。

图 4:iPhone 7的结构框图。来源:TechInsights

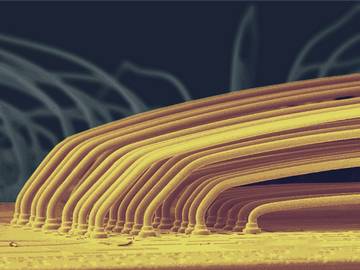

举例来说,智能手机已经为应用处理器提供了PoP技术。PoP技术将两个独立的封装堆叠在一起,并使用倒装芯片进行连接。

在PoP产品内,内存封装在顶部,而应用处理器则封装到底部。一个内存封装可以由一个或多个die组成。 基本上,存储die使用引线键合连接到衬底上。

许多智能手机OEM都在坚持使用PoP,因为该技术成熟又廉价。但是PoP在0.8mm左右的厚度下就无法发挥作用了。

为了找到PoP技术的替代品,行业正在开发一种被称为高密度扇出(fan-out)的高级封装技术,在fan-out技术中心,互联被扇出,从而使能更多I/O端口。

苹果的iPhone 7是高密度fan-out最显着的例子。台积电(TSMC)正在为苹果的A10应用处理器代工。 基于16nm finFET工艺,苹果的A10处理器就是使用台积电的fan-out产品技术,被称为集成扇出(Integrated Fan-Out,InFO)。根据TechInsights的说法,利用InFO技术A 10能够使用厚度从0.33mm到0.23mm的封装。

InFO类似于一种PoP封装技术,内存封装位于顶部,应用处理器封装位于底部。 在一些fan-out配置中,存储器die通过引线键合堆叠并连接到衬底上。 通常,银线用于连接存储器die堆叠。由于银线相对较软,从而降低焊接盘损坏的风险。

图 5:PoP vs WLP fan-out。 来源: TechSearch

在iPhone 7中,同时有四个LPDDR4 SDRAM die。 根据TechInsights的说法,die不是堆叠的,而是遍布整个封装,将整体的封装高度保持在最低限度。

星科金朋的Fontanilla说:“一些fan-out WLP使用引线键合,有些则不然。有时候,它们在封装内组合使用引线键合和倒装芯片技术。”

实际上,PoP和fan-out可以使用几种互连技术的组合,有时被称为“混合封装”。另外,系统级封装(SIP)的产品也可以利用混合封装。ASE的陈解释说说:“这样封装内部就会很复杂,它将结合引线键合、倒装芯片和晶圆级封装技术。”

一般而言,混合封装增加了制造方程的成本和复杂性。 另一方面,混合封装是确实有价值。比如,由于性能原因,在智能手机中应用处理器使用fan-out是有意义的。

但是智能手机还包括其他设备,比如MEMS、微控制器和射频芯片。它们还包括无源组件。由于成本原因,这些芯片大多数都不需要高级封装,引线键合就已经满足要求了,且成本较低。

图6 :混合封装。来源:Kulicke & Soffa.

堆叠NAND

对于应用处理器而言,DRAM堆栈仅限于四层die。为了节省成本,该行业就迁移到3D DRAM技术,如高带宽内存(HBM)。但是,HBM对于一款智能手机来说,过于昂贵了,至少现在看来是这样。

NAND的故事有所不同。根据TechInsight所说,通常情况下,智能手机采用独立的NAND芯片进行数据存储。一个标准的iPhone 7具有128GB的闪存。使用传统的平面型NAND,该手机可叠加16个128 Gbit的die。

Micron Technology中负责DRAM产品工程的总监Tony Veches表示,一般来说,人们对NAND堆叠的评价是:“使用引线键合技术的NAND堆栈通常限制在16个高位。 使用这种技术,对堆叠的die数目没有机械限制。但是,我们确实遇到了基于信号完整性和功率传递的限制。这将根据die和应用的具体情况而有所不同。

该技术还要面临其他挑战。 例如,NAND堆栈必须满足一定的配置要求。但是当我们堆叠更多die时,堆栈高度又会增加。

为了保持规格的规范性,封装厂商可能需要减少每个die的厚度,这种具有挑战性的工艺过程被称为晶圆薄化。使用称为晶片变薄的具有挑战性的过程来减小每个管芯的厚度。 Fontanilla说:“例如,在一个10层die的堆栈中,只需要50μm厚度的晶圆。 而在一个10层die的堆栈中,晶圆厚度仅为30μm。”

苹果可能已经解决了这个问题。 根据TechInsights的说法,一些高端iPhone 7机型正在使用3D NAND,从而能够实现256Gbdie的更薄的八层die堆叠。

3D NAND堆栈可能会与极板键合。 与平面结构的2D NAND不同,3D NAND由多层组成,密度有所增加。

更多的芯片和传感器

与此同时,一部智能手机还集成了许多其他芯片,诸如音频IC,FPGA,LCD控制器,MCU,MEMS等。

其中的许多芯片要求低于0.5mm的封装高度。Amkor的Arcedera称:所有这些组件都需要安装在LCD显示屏的下面,因此它们需要更薄。”

为此,有几种封装类型可供选择——极薄、细间距的BGA(XFBGA),QFN;以及WLP。

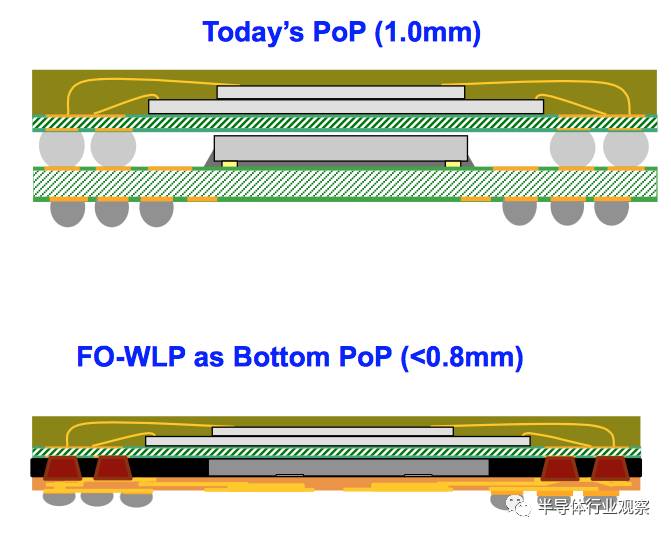

无引线方形扁平封装(QFN)是一种老式但受欢迎的封装类型,因为它可以获得薄型尺寸且价格低廉。 在QFN中,将铜框架或引线框放置在die上,在引线框的四面各有一个焊盘。利用引线键合器,引线将die连接并缝合到焊盘上。

图 7: QDN示意图。来源:Wikipedia

同样基于引线键合的XFBGA是另一个竞争者。不同于QFN,XFBGA封装使用层压基板而不是引线框架。然后,利用一种被称为扇入式(fan-in)的WLP技术,将I / O放置在焊球上,实现了微小的封装。

QFN面临的问题是路由能力受限。直到最近,XFBGA的尺寸限制在大约0.45mm的高度。 Amkor公司的层压产品总监Choonho Choi在白皮书中表示:“倒装芯片CSP(设计)可以克服这些技术问题,并提供另一个有效的解决方案。但是它需要在die上进行冲击过程(冲模),这是导致成本增加的主要原因,特别是如果压模设计不允许用户实现廉价的冲模和填充不足的方法。”

为了解决这个问题,Amkor开发出了一种低功耗的XFBGA技术,设计了最大高度0.40mm的XFBGA装配工艺流程。 Amkor将该技术称为ChipArray球栅阵列(CABGA)。

图 8: XFBA技术图解。来源:Amkor

Amkor和其他封测代工(OSAT)厂商还提供了具有竞争力的QFN和WLP产品。Arcedera说:“我们正在努力为客户提供选择,传统上,这种厚度是晶片级CSP所在的区域,(CABGA)允许传统的开发引线键合器件的客户与晶圆级解决方案竞争。”

这为IC设计人员带来了一些优势。Arcedera解释道:“他们的设计库已经建成了用于引线键合的产品。 因此,他们可以重新使用这些设计库来更快地生产一个芯片,并将其推出市场,而不是将其完全地重新设计为倒装芯片应用,我们正在为设计人员提供一种能力,使得他们能够更长时间继续使用自己的引线键合产品。”

此外,今天的智能手机集成了多种传感器。事实上,苹果的iPhone 7集成了以下类型的传感器:指纹识别、加速度、陀螺仪、距离传感器、指南针和气压。

传感器是引线键合、倒装芯片和WLP的主要驱动器。星科金朋的Fontanilla说:“不同的传感器具有不同的工艺要求.”

封测代工厂在几个传感器领域的营业额都有增长,特别是ID识别应用的指纹传感器。据Yole Développement称,智能手机指纹传感器市场总量从2013年的2300万台,增长到2016年的6.89亿台,同比增长了210%。但是,随着智能手机增速放缓, 2016年到2022年指纹传感器市场预计将增长19%。

传感器需要更小更薄的外形尺寸。Fontanilla说:“对于指纹传感器来说,挑战主要来自模具间的间隙。有些客户要求更高的清关率,有些则需要更薄的间隙。更薄的清关是具有挑战性的部分,我们需要做一些额外的步骤才能确保清除。”

有一段时间,星科金朋已经加强了对传感器的封装能力。ASE、Amkor和其他厂商也在追逐市场。显然,汽车、移动设备、传感器及其他市场将继续推动引线键合技术,从而保证该技术在未来几年依然存活。

原文链接:http://semiengineering.com/wirebond-technology-rolls-on/

今天是《半导体行业观察》为您分享的第1275期内容,欢迎关注。