正文

(该文包含了比较多的代码,建议点击阅读原文前往论坛查看原帖)

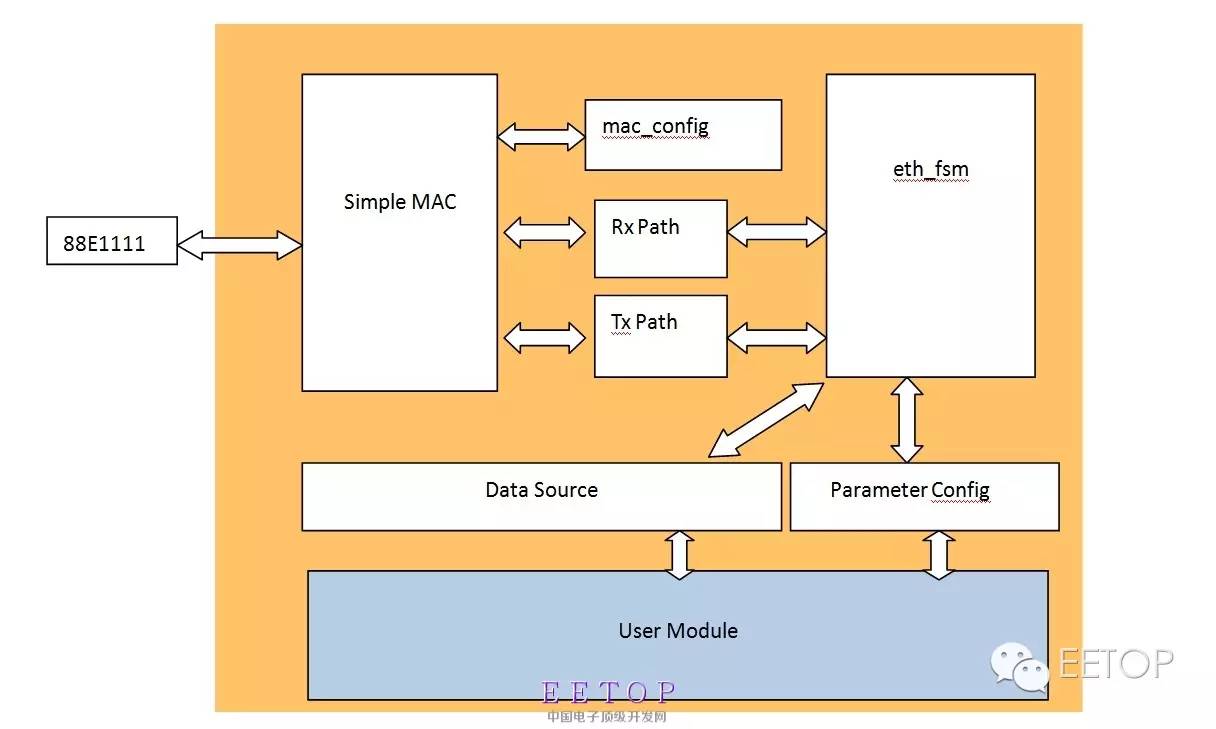

目前TCP协议大多由cpu跑代码实现, 这次用FPGA的纯逻辑实现 , System Verilog编写,下面给大家粗略讲一下我的实现方法,下面是工程的示意图.

这个工程由几部分组成, 外部使用了88e1111千兆以太网phy。FPGA内部有几个大的模块,

顶层模块:

//////////////////////////////////////////////////////////////////////

//// ////

//// tcpip_hw ////

//// ////

//// Description ////

//// top module ////

//// ////

//// Author(s): ////

//// - bin qiu, [email protected] or [email protected] ////

//// ////

//// Copyright (C) 2015 ////

//////////////////////////////////////////////////////////////////////

`include "tcpip_hw_defines.sv"

module tcpip_hw(

input clk,

input rst_n,

output mdc,

inout mdio,

output phy_rst_n,

output is_link_up,

input [7:0] rx_data,

output logic [7:0] tx_data,

input rx_clk,

input rx_data_valid,

output logic gtx_clk,

input tx_clk,

output logic tx_en,

//user interface

input [7:0] wr_data,

input wr_clk,

input wr_en,

output wr_full,

output [7:0] rd_data,

input rd_clk,

input rd_en,

output rd_empty

);

。。。。

(由于微信字数限制,此处省去200多行代码,可以点击阅读原文查看)

1. 与外部phy芯片通信的模块,simple_mac模块。

主要功能是通过mdio配置phy, 给发送帧打包(加入preamble,padding和crc32),和接收帧解包。 下面是顶层代码:

//////////////////////////////////////////////////////////////////////

//// ////

//// simple_mac_top ////

//// ////

//// Description ////

//// top module of simple mac ////

//// ////

//// Author(s): ////

//// - bin qiu, [email protected] or [email protected] ////

//// ////

//// Copyright (C) 2015 ////

//////////////////////////////////////////////////////////////////////

module simple_mac_top(

input clk,

input rst_n,

output mdc,

input mdio_in,

output mdio_out,

output mdio_oe,

output phy_rst_n,

input [7:0] rx_data,

output logic [7:0] tx_data,

input eth_mode,

input rx_clk,

input tx_clk,

input clk125out,

output tx_en,

input rx_data_valid,

input [7:0] reg_addr,

input reg_wr,

input [31:0] reg_wr_data,

input reg_rd,

output [31:0] reg_rd_data,

output reg_busy,

input ff_rx_clk,

output [31:0] ff_rx_data,

output ff_rx_eop,

output ff_rx_sop,

output rx_err,

output ff_rx_dval,

input ff_rx_rdy,

input ff_tx_clk,

input [31:0] ff_tx_data,

input ff_tx_eop,

input ff_tx_sop,

input ff_tx_wren,

output ff_tx_rdy

);

(由于微信字数限制,此处省去200多行代码,可以点击阅读原文查看)

2. mac_config

这个模块主要是配置phy芯片寄存器的。

3. Rx Path

这个模块负责从simple_mac接收数据,然后提交给eth_fsm的。 下面是接口列表.

input rst_n,

ff_rx_if.s if_rx,

headers_if if_headers_rx,

output frame_type_t rx_type,

output logic rx_done,

output logic [31:0] data_recv,

output logic data_recv_start,

output logic data_recv_valid,

output logic [15:0] data_recv_len,

output u32_t cur_ripaddr,

output u16_t cur_rport,

input rx_done_clear,

input [31:0] local_ipaddr,

input [31:0] remote_port_local_port

接口列表里有2个interface,

if_rx是与simple_mac连接的接口。

if_headers_rx是保存各种header并提供给eth_fsm的,如mac_header, arp_header,ip_header,udp_header,tcp_header。

rx_done是一帧接收完的信号并提供给eth_fsm。

中间一段用来从一帧中提取数据并提供给eth_fsm 。

下面是配置ip地址和收发端口号的。

4. Tx Path

这个模块从eth_fsm取得数据和各种header,并发送给simple_mac, 下面是接口

input rst_n,

ff_tx_if.s if_tx,

headers_if if_headers_tx,

input frame_type_t tx_type,

input tx_start,

input [13:0] tx_dword_count,

output logic fifo_rdreq,

input [31:0] fifo_q

其中if_tx是与simple_mac的接口, if_headers_tx是从eth_fsm来的各种header,

tx_type是帧的类型,目前支持ARP, ICMP,TCP,UDP。

tx_start是一帧传输开始的信号。

tx_dword_count是发送的字节数除以4 。

fifo_rdreq和fifo_q是从eth_fsm来的数据。

5. eth_fsm

这是整个工程的核心, 是处理协议的状态机和控制数据的流动,下面是接口

input clk,

input rst_n,

input is_link_up,

headers_if if_headers_rx,

input frame_type_t rx_type,

input rx_done,

headers_if if_headers_tx,

output frame_type_t tx_type,

output logic tx_start,

input [31:0] data_recv,

input [15:0] data_recv_len,

input data_recv_valid,

input data_recv_start,

output logic rx_done_clear,

input u32_t cur_ripaddr,

input u16_t cur_rport,

rx_ram_in_if.m if_rx_ram_in,

tx_ram_out_if.m if_tx_ram_out,

input [31:0] remote_port_local_port,

input [31:0] local_ipaddr,

input fifo_rdreq,

output [31:0] fifo_q,

input pkt_send_eop,

output logic [13:0] tx_dword_count,

output logic init_done

由于这个模块过于复杂,就不介绍了。

6. data_source

这个模块提供了与用户模块的接口

input rst_n,

input init_done,

input [7:0] wr_data,

input wr_clk,

input wr_en,

output wr_full,

output [7:0] rd_data,

input rd_clk,

input rd_en,

output rd_empty,

tx_ram_in_if.m if_tx_ram_in,

rx_ram_out_if.s if_rx_ram_out

其中wr开头和rd开头的都是对外提供的fifo接口, 分别用来写和读内部的发送FIFO和接收FIFO.

目前实现情况

目前udp协议可以基本全速运行,但是有丢包的情况,需要有个确认机制。

tcp协议只实现了最基本的功能,能够通信。窗口管理和慢启动,拥塞避免等特性还在完善中,速度只能达到200多M。

对这个工程的介绍就到这里了,希望对大家有用。

关注微信号eetop-1,回复以下红色关键词,阅读推荐文章:

fpga01 - 数字前端及FPGA设计相关书目泛读及点评

Zynq片内XADC应用笔记

Zynq器件时钟子系统介绍

建立及保持时间、建立及保持余量的理解

软核MicroBlaze的C编程经验及技巧

Tcl在Vivado中的应用

Vivado的使用介绍:使用IP核

大话setup time与hold time

Vivado使用详细介绍1:创建工程,编写代码,行为仿真,Testbench

fpga02 - 防止毛刺的时钟切换电路的设计思想

函数发生器实现方法简述

Vivado使用详细介绍2综合实现管脚分配时钟设置烧写

基于FPGA的DDR3多端口读写存储管理设计

在低成本FPGA开发板上实现Oberon系统

全可编程抽象化:你的编程你做主

XILINX FPGA FIFO使用技巧

智能视觉系统中如何处理多图像传感器?

FPGA时钟和复位电路设计

同步器的设计

fpga03 - 数字IC工程师的技能树

FPGA设计,视时序为一切

在FPGA设计中,时序就是全部

利用FPGA对大规模MIMO信道进行特性描述

如何将PetaLinux移植到Xilinx FPGA上

关于FPGA设计仿真和硬件实测不一致问题的讨论

FPGA适合用在哪儿?OpenCL,C,和C++语言对FPGA和全SoC有什么用?

fpga04 - 数字IC工程师的技能树

FPGA设计,视时序为一切

在FPGA设计中,时序就是全部

利用FPGA对大规模MIMO信道进行特性描述

如何将PetaLinux移植到Xilinx FPGA上

关于FPGA设计仿真和硬件实测不一致问题的讨论

FPGA适合用在哪儿?OpenCL,C,和C++语言对FPGA和全SoC有什么用?

趣图:

趣图02:

mn01 : 模拟数字产品开发流程

模拟IC正向设计流程总结

mn02 : 好的模拟IC工程师应该具有的素养

mn03 : 模拟IC设计领域的经典之作

mn04 : 极点零点之我见

mn05 : 六本经典模拟IC书籍精彩评论及总结

mn06 : 模拟设计的100条圣经

mn07 : 模拟电路学习入门的建议

mn08 : 模拟IC流片经验分享

mn09 : 模拟IC年薪几十万师兄的模电学习经历

mn10 : 想成为一名模拟ic设计师在本科期间应该做哪些准备?

mn11 : 模拟电路设计的九重进阶

mn12 : AnalogIC难在哪里,结构?参数?版图?系统?

icsj01 : IC设计完整流程及工具简述

IC芯片设计及生产流程

射频半导体工艺介绍

IC 芯片的成本从哪里来?

icsj02 : 说说芯片设计这点事

icsj03 : 关于IC设计的想法

icsj04 : 数字IC设计的完整流程(非常详细!)

icsj05 : 数字IC Design技术全局观(110页PPT!)

icsj06 : ASIC设计中各个阶段需要注意的问题

icsj07 : 集成电路反向分析的争议性

人生 :

封装:

2014年度中国IC封装测试产业调研报告

封装,IC 芯片的最终防护与统整

非常全面的集成电路封装示意图

非常详细的封装流程介绍

稳压器封装概述

最伟大 :

世界上最伟大的十个公式

统治世界的十大算法

微波射频领域传奇人物

集成电路史上最著名的10个人

电气之王,还原真实的尼古拉·特斯拉

电学实验史话--几个著名的电学实验

六位伟大的“数学学渣”科学家

职业发展01 :

何为技术型复合人才

开发工程师人生之路

数字IC工程师的技能树

好的模拟IC工程师应该具有的素养

3年以上工作经验的工程师中长期职业规划

一位老工程师的心里话

一名工作11年老IC工程师的未来之路的探讨

给去小微初创公司的同学一点建议

电子工程师路线图全剖析

职业发展02 :

业务联系请加个人微信号:jack_eetop 或 QQ:228265511全力打造中国电子工程师微信第一品牌!

点击左下角阅读原文