为了方便各位同学交流学习,解决讨论问题,我们建立了一些微信群,作为互助交流的平台。

2.告知:姓名-课题组-研究方向,由编辑审核后邀请至对应交流群(生长,物性,器件);

欢迎投稿欢迎课题组投递中文宣传稿,免费宣传成果,发布招聘广告,具体联系人:13162018291(微信同号)

研究背景

2D半导体由于其原子薄的几何形状和优异的物理/化学性质,已成为亚3 nm技术节点中用于终极短沟道晶体管的有希望候选者。为此,高质量和稳健的金属接触对于进一步提高2D晶体管的性能和能力是必不可少的。然而,传统的金属化工艺通常会导致金属-2D半导体界面的强耦合,导致不可避免的化学无序和晶格缺陷,这在很大程度上归因于高能金属原子或团簇对接触区域的持续轰击和破坏。因此,金属诱导的间隙态变得明显,导致2D晶体管中明显的费米钉扎效应和不可控的肖特基势垒高度。因此,构建高质量和可靠的金属接触,实现可调的能垒和载流子极性,是2D电子器件中的一个重大技术挑战。为了提高2D器件的接触质量和实现最佳性能,人们一直致力于通过范德华(vdW)集成来构建金属-层间半导体(MIS)接触结构。早期的尝试包括在金属电极和2D沟道之间插入超薄的2D半金属/金属材料作为缓冲层,有效地防止金属原子和团簇对2D沟道的重复轰击。然而,金属层间缓冲层的存在引入了不可避免的垂直串联电阻,这阻碍了从金属电极到2D沟道半导体的高效载流子注入。为了增加载流子注入,研究人员利用低熔融温度的3D金属探索了vdW集成过程,因为这些金属原子或团簇向2D沟道传递的动能最小,因此不会产生可检测到的界面无序。然而,这些低熔点金属和半金属通常具有较低的功函数,使其仅适用于匹配2D半导体的导带。

成果介绍

有鉴于此,近日,

松山湖材料实验室孔令安助理研究员、梁齐杰研究员和湖南大学刘渊教授(共同通讯作者)等合作报道了一种范德华(vdW)集成策略,通过精心调制金属接触组分来精确定制WSe

2

极性

。控制低熔点铋(Bi)的厚度可有效调节Bi/Au与WSe

2

的主导接触。这有助于在n型、双极性和p型之间进行精确的极性转换,电子的场效应迁移率为200 cm

2

V

-1

s

-1

,空穴的场效应迁移率为136 cm

2

V

-1

s

-1

。在这个vdW几何结构中,本文进一步展示了具有增强整流比和电压增益的二极管和互补反相器等基本电学元件。本文的研究结果展示了一种有效且兼容的大规模制造方法,用于精确的2D半导体极性调制,为大规模高性能2D电子器件和集成电路提供了一条有希望的途径。文章以“

Precisely Tailoring WSe

2

Polarity via van der Waals Bismuth-Gold Modulated Contact

”为题发表在著名期刊

Nano Letters

上。

图文导读

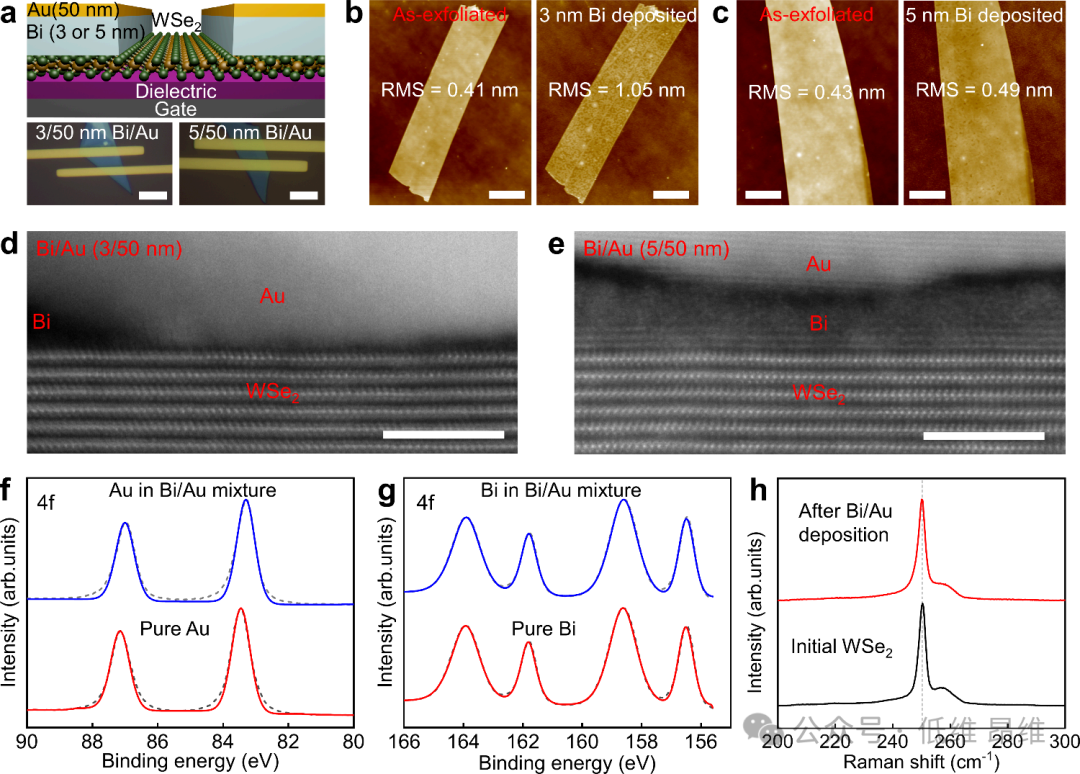

图1. 具有金属vdW集成的器件结构及表征。(a)Bi/Au调制的集成示意图和光学图像。(b&c)剥离的WSe

2

的AFM表征,RMS粗糙度为0.4 nm,沉积3 nm厚Bi层后,RMS值增加到1.05 nm,而沉积5 nm厚Bi层后,RMS值降低到0.49 nm。(d&e)具有3 nm Bi/50 nm Au和5 nm Bi/50 nm Au vdW接触的WSe

2

的横截面HRTEM图像。(f&g)纯Au和Bi薄膜和Bi-Au混合薄膜的XPS表征。(h)剥离的WSe

2

和Bi/Au金属(3 nm/3 nm厚)沉积后的归一化拉曼光谱,峰位于250.37 cm

-1

处不变。

在本文的vdW金属调制策略中,发现具有Bi/Au(3 nm/50 nm)接触的WSe

2

晶体管表现出稳健的p型特性,而具有Bi/Au(≥5 nm/50 nm)接触的WSe

2

晶体管表现出稳健的n型行为。图1a给出了WSe

2

器件的结构示意图和具有不同接触组分的光学图像。为了证实半金属Bi的作用,本文进行了AFM表征,测量了WSe

2

薄片顶部Bi层的表面形貌。最初,剥离的WSe

2

薄片表面粗糙度的均方根(RMS)值为0.4 nm。热沉积3 nm厚Bi后,WSe

2

的RMS值增加到1.05 nm(图1b)。这种粗糙度的变化可能归因于WSe

2

上不连续的岛状超薄Bi层,与报道的金属沉积相一致。相比之下,当在WSe

2

表面上沉积5 nm厚的半金属Bi层时,它表现出均匀且平坦的薄膜形态,其RMS值与WSe

2

表面的RMS值相当(~0.49 nm),表明5 nm厚的金属足以实现电极接触质量(图1c)。Bi是一种低熔点的半金属,具有最低的热导率,已经证明了费米能级的去钉扎效应,可以忽略接触势垒。为了确认调制的金属与WSe

2

之间的vdW界面,进行了横截面HRTEM表征。如图1d所示,具有Bi/Au(3 nm/50 nm)金属组分的器件与WSe

2

的主要接触层为Au封盖层。在这种情况下,Bi形成岛状或多孔状,提供缓冲层以减轻高能Au原子与WSe

2

的强相互作用,从而在沉积的Au和WSe

2

之间构建vdW接触。当在WSe

2

沟道上沉积Bi/Au(5 nm/50 nm)金属组分时,横截面HRTEM显示整个接触区域被均匀的Bi层覆盖,具有原子级锐利和洁净的Bi/WSe

2

界面(图1e)。这在很大程度上是由于Bi层足够的厚度和与先前报道一致的低能蒸发过程。重要的是,这种主导接触的调制来自Au封盖层,而不是Bi-Au合金的形成,正如XPS测量所证实的那样(图1f和g),其中Bi/Au混合物的特征峰与单个金属的峰保持相同。此外,这种Bi/Au调制的vdW接触保留了WSe

2

接触区域的本征物理性质,剥离的单层WSe

2

和在Bi/Au顺序沉积后,都在250.4 cm

-1

处显示出相同的归一化拉曼峰(E

1

1g

),表明Bi/Au没有引起损伤或掺杂(图1h)。

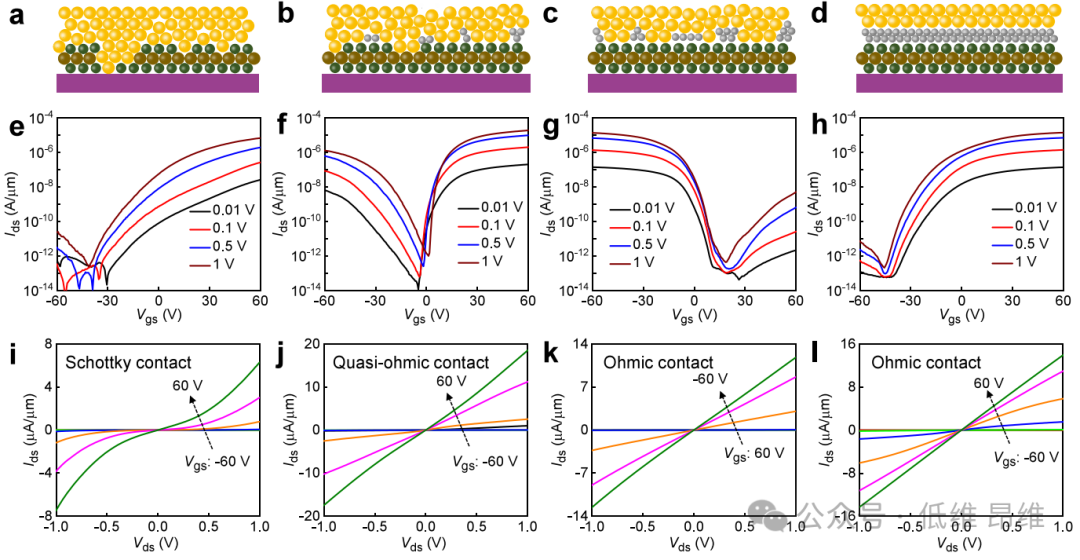

图2. 具有不同Bi/Au接触组成的WSe

2

晶体管的电学性质。(a-d)具有不同Bi厚度的器件结构示意图,随着Bi厚度增加,金属与WSe

2

之间的相互作用由强耦合转变为弱耦合。(e-h)具有不同Bi厚度的WSe

2

晶体管的转移曲线和n型、双极性、p型、n型行为。(i-l)具有不同Bi厚度的WSe

2

晶体管对应的输出曲线,分别为肖特基接触、准欧姆接触、欧姆接触、欧姆接触特性。

本文在保持Au封盖层固定的情况下,对具有相同WSe

2

厚度但不同Bi厚度的WSe

2

晶体管进行了详细的电学测量。图2显示了不同Bi厚度的器件示意图和代表性电学测量结果。当只有Au接触而没有Bi层沉积时,非理想Au-WSe

2

界面导致明显的n型I

ds

-V

gs

转移特性和非线性I

ds

-V

ds

输出曲线(图2a,e和i),表明Au和WSe

2

之间存在肖特基接触和强费米能级钉扎效应。在WSe

2

表面沉积1 nm厚的薄Bi层后,界面损伤得到适度缓解,但原子扩散和晶格缺陷仍然存在,这是由于超薄的不连续Bi缓冲层不能完全阻止高能Au原子与WSe

2

沟道的相互作用。结果,WSe

2

器件表现出n型主导的双极性输运行为,具有准欧姆接触特性(图2b,f和j),表明在接触界面存在弱费米能级钉扎效应。TEM表征证实,随着在WSe

2

表面沉积较厚的3 nm Bi层,形成了岛状缓冲层,促进了Au封盖层与WSe

2

沟道之间弱耦合vdW接触的产生。因此,电学测量显示出稳健的p型I

ds

-V

gs

转移行为和线性I

ds

-V

ds

输出曲线(图2c,g和k),表明金属Au的费米能级与WSe

2

的价带有效对齐,从而实现了欧姆接触。相反,当沉积5 nm的Bi层时,它会形成一层均匀的薄膜,作为主要的接触层而不是缓冲层(图2d)。图2h和l显示了载流子输运特性,显示了高性能的n型I

ds

-V

gs

转移曲线和相应的线性I

ds

-V

ds

输出曲线,表明成功实现了欧姆接触。这种显著的性能与沉积金属Au/Bi/Au(3/3/50 nm)体系明显不同,其中WSe

2

晶体管无论WSe

2

厚度如何都表现出n型特性。本文的vdW集成策略不仅可以精确定制WSe

2

晶体管的极性,还可以根据不同的电极接触组成有效地将肖特基接触转换为欧姆接触,为调制载流子极性提供了一种有效的方法。

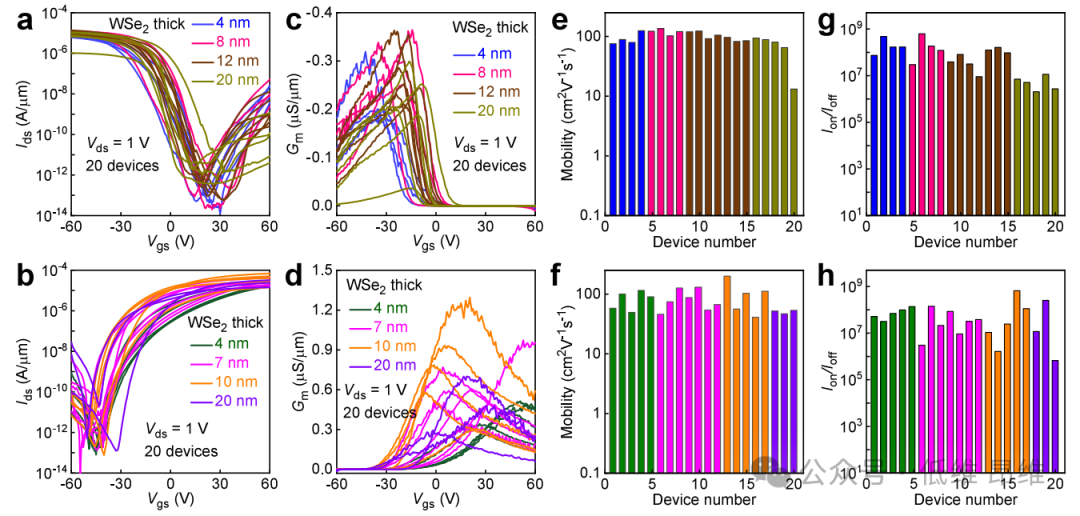

图3. 采用不同主vdW金属接触的p-/n型WSe

2

晶体管的电学性能。(a)20个具有Au vdW接触的背栅p型WSe

2

晶体管的转移特性。(b)20个具有Bi vdW接触的背栅n型WSe

2

晶体管的转移特性。(c&d)提取的跨导(G

m

)随V

gs

的变化。(e&f)p型和n型WSe

2

晶体管的场效应迁移率统计。(g&h)p型和n型WSe

2

晶体管相应的I

on

/I

off

统计。

此外,为了验证其稳健的电学性能并定量分析Bi厚度相关的极性变化,本文进一步对20个具有不同WSe

2

沟道厚度的背栅p/n型器件进行了测量。如图3a和b所示,随着厚度增加,I

ds

-V

gs

转移曲线一致地显示出本征p型和n型行为,这表明WSe

2

沟道分别受到vdW接触中高(Au)和低(Bi)功函数金属的影响。相反,在传统的Au接触沉积中,由于费米能级钉扎效应,WSe

2

器件表现出可变的极性类型。建立这种vdW接触特性后,基于I

ds

-V

gs

转移曲线提取两点跨导G

m

(Au和Bi vdW金属接触),如图3c和d所示。Au接触器件的最高G

m

值为0.3 μS/μm,Bi接触器件的最高G

m

值为1.2 μS/μm。此外,本文还提取了双端空穴和电子迁移率μ。图3e和f显示了20个不同WSe

2

厚度、V

ds

为1 V的器件计算的空穴和电子迁移率,p型器件的最大迁移率可达136 cm

2

V

-1

s

-1

(100 K时为153 cm

2

V

-1

s

-1

),n型器件的最大迁移率可达200 cm

2

V

-1

s

-1

(100 K时为236 cm

2

V

-1

s

-1

)。获得的这些电子迁移率与迄今为止报道的WSe

2

晶体管的最高值相当。在不同温度下观察到的显著迁移率很大程度上归因于接触界面上杂质和声子散射的抑制。此外,这些背栅器件表现出长期稳定性和超过10

8

的高电流开关比(I

on

/I

off

),同时保持相对较小的亚阈值摆幅(SS),如图3g和h所示。

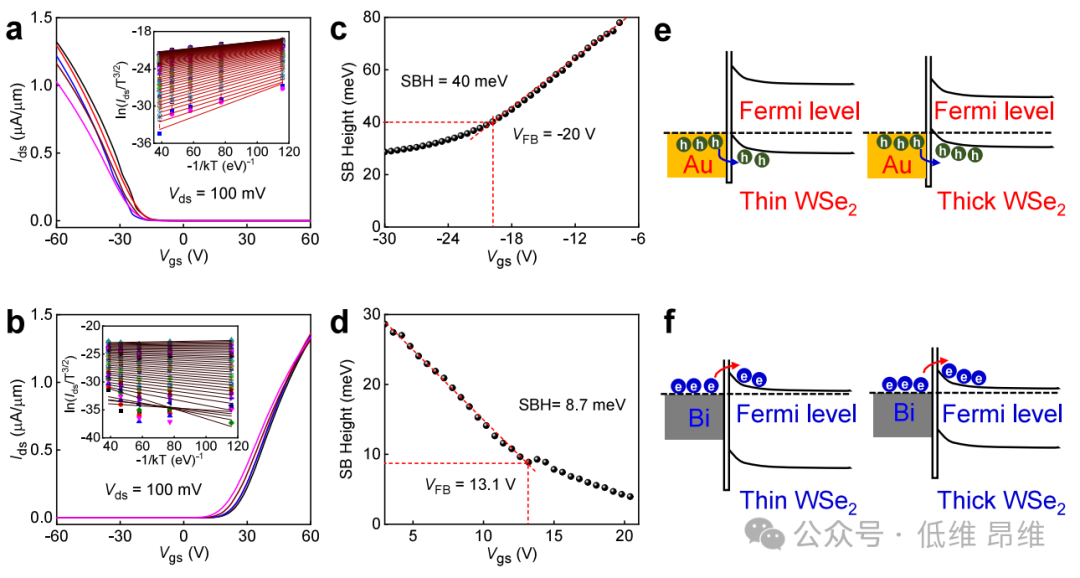

图4. p/n型晶体管提取的Φ

SB

及能带图。(a&b)不同温度下(从300到100 K),在100 mV偏置电压下,使用主导Au vdW接触与Bi坚固且不连续缓冲层和主导Bi vdW接触的WSe

2

晶体管的转移曲线。(c&d)在不同栅极电压下提取的肖特基势垒高度,其中测得p型Φ

SB

为40 meV,n型Φ

SB

为8.7 meV。(e&f)使用主导Au和Bi接触的WSe

2

晶体管的能带示意图。

由于

WSe

2

晶体管的极性可以通过vdW Bi-Au调制接触精确定制,本文进一步使用Arrhenius图方法测量了p型和n型晶体管的肖特基势垒高度(Φ

SB

),如图4a和b所示。在100 mV的偏置电压下,将提取的势垒高度绘制为栅极电压的函数,并通过平带方法定义有效的Φ

SB

。测量到空穴和电子的平带Φ

SB

值分别为40和8.7 meV,低于金属沉积Au接触获得的值(75 meV),如图4c和d所示。这两种载流子的低Φ

SB

值对于高性能2D电子器件的制造至关重要。此外,能带对齐理论解释了WSe

2

的极性取决于金属功函数。由于接触金属和

WSe

2

之间存在vdW间隙,使用vdW Au接触(以Bi作为缓冲层)可以有效地匹配

WSe

2

的价带,并在不同厚度下最小化费米能级钉扎。此外,Bi作为接触层有效地对齐了不同厚度WSe

2

的导带,如图4e和f所示。

图5. 基于互补WSe

2

晶体管的二极管和CMOS反相器。(a)在300 nm SiO

2

电介质上制备的WSe

2

互补反相器的结构示意图和光学图像。(b)不同V

gs

下肖特基二极管的I

ds

-V

ds

输出曲线。(c)肖特基二极管的整流比和理想因子与WSe

2

厚度的关系。(d)互补WSe

2

晶体管在电源电压V

ds

为0.1 V、0.5 V和1 V时的I

ds

-V

gs

转移曲线。(e)在不同电源电压V

dd

下,WSe

2

反相器的电压传输特性与输入电压V