cpu与外部设备、存储器的连接和数据交换都需要通过接口设备来实现,前者被称为I/O接口,而后者则被称为存储器接口。

存储器通常在cpu的同步控制下工作,接口电路比较简单,I/O接口的功能是负责实现cpu通过系统总线把I/O电路和外围设备联系在一起。比如SATA,它是Serial ATA的缩写,即串行ATA。

这是一种完全不同于并行ATA的新型硬盘接口类型,由于采用串行方式传输数据而得名。SATA总线使用嵌入式时钟信号,具备了更强的纠错能力,与以往相比其最大的区别在于能对传输指令(不仅仅是数据)进行检查,如果发现错误会自动矫正,这在很大程度上提高了数据传输的可靠性。串行接口还具有结构简单、支持热插拔的优点。

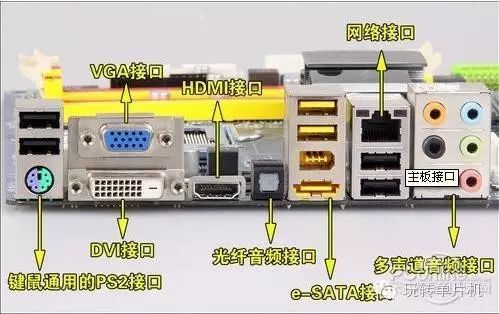

史上最全:主板上常见的接口信号定义

一、cpu接口信号说明

1.A[31:3]# (I/O) Address(地址总线)

这组地址信号定义了cpu的最大内存寻址空间为4GB。在地址周期的第一个子周期中,这些Pin传输的是交易的地址,在地址周期的第二个子周期中,这些Pin传输的是这个交易的信息类型。

2.A20M# (I) Adress-20 Mask(地址位20屏蔽)

此信号由ICH(南桥)输出至cpu的信号。它是让cpu在Real Mode(真实模式)时仿真8086只有1M Byte(1兆字节)地址空间,当超过1 Mbyte位空间时A20M#为Low,A20被驱动为0而使地址自动折返到第一个1Mbyte地址空间上。

3.ADS# (I/O) Address Strobe(地址选通)

当这个信号被宣称时说明在地址信号上的数据是有效的。在一个新的交易中,所有Bus上的信号都在监控ADS#是否有效,一但ADS#有效,它们将会作一些相应的动作,如:奇偶检查、协义检查、地址译码等操作。

4.ADSTB[1:0]# (I/O) Address Strobes

这两个信号主要用于锁定A[31:3]#和REQ[4:0]#在它们的上升沿和下降沿。相应的ADSTB0#负责REQ[4:0]#和A[16:3]#,ADSTB1#负责A[31:17]#。

5.AP[1:0]# (I/O) Address Parity(地址奇偶校验)

这两个信号主要用对地址总线的数据进行奇偶校验。

6.BCLK[1:0] (I) Bus Clock(总线时钟)

这两个Clock主要用于供应在Host Bus上进行交易所需的Clock。

7.BNR# (I/O) Block Next Request(下一块请求)

这个信号主要用于宣称一个总线的延迟通过任一个总线代理,在这个期间,当前总线的拥有者不能做任何一个新的交易。

8.BPRI# (I) Bus Priority Request(总线优先权请求)

这个信号主要用于对系统总线使用权的仲裁,它必须被连接到系统总线的适当Pin 。当BPRI#有效时,所有其它的设备都要停止发出新的请求,除非这个请求正在被锁定。总线所有者要始终保持BPRI#为有效,直到所有的请求都完成才释放总线的控制权。

9.BSEL[1:0] (I/O) Bus Select(总线选择)

这两组信号主要用于选择cpu所需的频率,下表定义了所选的频率:

10.D[63:0]# (I/O) Data(数据总线)

这些信号线是数据总线主要负责传输数据。它们提供了cpu与NB(北桥)之间64 Bit的通道。只有当DRDY#为Low时,总在线的数据才为有效,否则视为无效数据。

11.DBI[3:0]# (I/O) Data Bus Inversion(数据总线倒置)

这些信号主要用于指示数据总线的极性,当数据总在线的数据反向时,这些信号应为Low。这四个信号每个各负责16个数据总线,见下表:

12.DBSY# (I/O) Data Bus Busy(数据总线忙)

当总线拥有者在使用总线时,会驱动DBSY#为Low表示总线在忙。当DBSY#为High时,数据总线被释放。

13.DP[3:0]# (I/O) Data Parity(数据奇偶校验)

这四个信号主要用于对数据总在线的数据进行奇偶校验。

14.DRDY# (I/O) Data Ready(数据准备)

当DRDY#为Low时,指示当前数据总在线的数据是有效的,若为High时,则总在线的数据为无效。

15.DSTBN[3:0]# (I/O) Data Strobe

Data strobe used to latch in D[63:0]# :

16.DSTBP[3:0]# (I/O) Data Strobe

Data strobe used to latch inn D[63:0]# :

17.FERR# (O) FloaTIng Point Error(浮点错误)

这个信号为一cpu输出至ICH(南桥)的信号。当cpu内部浮点运算器发生一个不可遮蔽的浮点运算错误时,FERR#被cpu驱动为Low。

18.GTLREF (I) GTL Reference(GTL参考电压)

这个信号用于设定GTLn Bus的参考电压,这个信号一般被设为Vcc电压的三分之二。

19.IGNNE# (I) Ignore Numeric Error(忽略数值错误)

这个信号为一ICH输出至cpu的信号。当cpu出现浮点运算错误时需要此信号响应cpu。IGNNE#为Low时,cpu会忽略任何已发生但尚未处理的不可遮蔽的浮点运算错误。但若IGNNE#为High时,又有错误存在时,若下一个浮点指令是FINIT、FCLEX、FSAVE等浮点指令中之一时,cpu会继续执行这个浮点指令但若指令不是上述指令时cpu会停止执行而等待外部中断来处理这个错误。

20.INIT# (I) IniTIalizaTIon(初始化)

这个信号为一由ICH输出至cpu的信号,与Reset功能上非常类似,但与Reset不同的是cpu内部L1 Cache和浮点运算操作状态并没被无效化。但TLB(地址转换参考缓存器)与BTB(分歧地址缓存器)内数据则被无效化了。INIT#另一点与Reset不同的是cpu必须等到在指令与指令之间的空档才会被确认,而使cpu进入启始状态。

21.INTR (I) Processor Interrupt(可遮蔽式中断)

这个信号为一由ICH输出对cpu提出中断要求的信号,外围设备需要处理数据时,对中断控制器提出中断要求,当cpu侦测到INTR为High时,cpu先完成正在执行的总线周期,然后才开始处理INTR中断要求。

22.PROCHOT# (I/O) Processor Hot(cpu过温指示)

当cpu的温度传感器侦测到cpu的温度超过它设定的最高度温度时,这个信号将会变Low,相应的cpu的温度控制电路就会动作。

23.PWRGOOD (I) Power Good(电源OK)

这个信号通常由ICH(南桥)发给cpu,来告诉cpu电源已OK,若这个信号没有供到cpu,cpu将不能动作。

24.REQ[4:0]# (I/O) Command Request(命令请求)

这些信号由cpu接到NB(北桥),当总线拥有者开始一个新的交易时,由它来定义交易的命令。

25.RESET# (I) Reset(重置信号)

当Reset为High时cpu内部被重置到一个已知的状态并且开始从地址0FFFFFFF0H读取重置后的第一个指令。cpu内部的TLB(地址转换参考缓存器)、BTB(分歧地址缓存器)以及SDC(区段地址转换高速缓存)当重置发生时内部数据全部都变成无效。

26.RS[2:0]# (I) Response Status(响应状态)

这些信号由响应方来驱动,具体含义请看下表:

27.STKOCC# (O) Socket Occupied(cpu插入)

这个信号一般由cpu拉到地,在主机板上的作用主要是来告诉主机板cpu是不是第一次插入。若是第一次插入它会让你进CMOS对cpu进行重新设定。

28.SMI# (I) System Management Interrupt(系统管理中断)

此信号为一由ICH输出至cpu的信号,当cpu侦测到SMI#为Low时,即进入SMM模式(系统管理模式)并到SMRAM(System Management RAM)中读取SMI#处理程序,当cpu在SMM模式时NMI、INTR及SMI#中断信号都被遮蔽掉,必需等到cpu执行RSM(Resume)指令后SMI#、NMI及INTR中断信号才会被cpu认可。

30.STPCLK# (I) Stop Clock(停止时钟)

当cpu进入省电模式时,ICH(南桥)将发出这个信号给cpu,让它把它的Clock停止。

31.TRDY# (I/O) Target Ready(目标准备)

当TRDY#为Low时,表示目标已经准备好,可以接收数据。当为High时,Target没有准备好。

32.VID[4:0] (O) Voltage ID(电压识别)

这些讯号主要用于设定cpu的工作电压,在主机板中这些信号必须被提升到最高3V。

二、VGA接口信号说明

1.HSYNC (O) CRT Horizontal SynchronizaTIon(水平同步信号)

这个信号主要提供CRT水平扫描的信号。

2.VSYNC (O) CRT Vertical Synchronization(垂直同步信号)

这个信号主要提供CRT垂直扫描的信号。

3.RED (O) RED analog video output(红色模拟信号输出)

这个信号主要为CRT提供红基色模拟视频信号。

4.GREEN (O) Green analog video output(绿色模拟信号输出)

这个信号主要为CRT提供绿基色模拟视频信号。

5.BLUE (O) Blue analog video output(蓝色模拟信号输出)

这个信号主要为CRT提供蓝基色模拟视频信号。

6.REFSET (I) Resistor Set(电阻设置)

这个信号将会连接一颗电阻到地,主要用于内部颜色调色板DAC。这颗电阻的阻值一般为169奥姆,精度为1%。

7.DDCA_CLK (I/O) Analog DDC Clock

这个信号连接NB(北桥)与显示器,这个Clock属于I睠接口,它与DDCA_DATA组合使用,用于读取显示器的数据。

8.DDCA_DATA (I/O) Analog DDC Clock

这个信号连接NB(北桥)与显示器,这个Data与Clock 一样也属于I睠接口,它与DDCA_CLK组合使用,用于读取显示器的数据。

三、AGP接口信号说明

1.GPIPE# (I/O) Pipelined Read(流水线读)

这个信号由当前的Master来执行,它可以使用在AGP 2.0模式,但不能在AGP 3.0的规范使用。在AGP 3.0的规范中这个信号由DBI_HI(Dynamic Bus Inversion HI)代替。

2.GSBA[7:0] (I) Sideband Address(边带地址)

这组信号提供了一个附加的总线去传输地址和命令从AGPn Master(显示卡)到GMCH(北桥)。

3.GRBF# (I) Read Buffer Full(读缓存区满)

这个信号说明Master是否可以接受先前以低优先权请求的要读取的数据。当RBF#为Low时,中裁器将停止以低优先权去读取数据到Master。

4.GWBF# (I) Write Buffer Full(写缓存区满)

这个信号说明Master是否可以准备接受从核心控制器的快写数据。当WBF#为Low时,中裁器将停止这个快写数据的交易。

5.ST[2:0] (O) Status Bus(总线状态)

这组信号有三BIT,可以组成八组,每组分别表示当前总线的状态。

6.ADSTB0 (I/O) AD Bus Strobe 0(地址数据总线选通)

这个信号可以提供2X的时序为AGP,它负责总线AD[15:0]。

7.ADSTB0# (I/O) AD Bus Strobe 0(地址数据总线选通)

这个信号可以提供4X的时序为AGP,它负责总线AD[15:0]。

8.ADSTB1 (I/O) AD Bus Strobe 1(地址数据总线选通)

这个信号可以提供2X的时序为AGP,它负责总线AD[31:16]。

9.ADSTB1# (I/O) AD Bus Strobe 1(地址数据总线选通)

这个信号可以提供4X的时序为AGP,它负责线总AD[31:16]。

10.SB_STB (I) SideBand Strobe(SideBand选通)

这个信号主要为SBA[7:0]提供时序,它总是由AGPn Master驱动。

11.SB_STB# (I) SideBand Strobe(SideBand选通)

这个信号为SBA[7:n0]提供时序只在AGP 4X 模式,它总是由AGP Master驱动。

12.CLK (O) CLOCK(频率)

为AGP和PCI控制信号提供参考时序。

13.PME# Power Management Event(电源管理事件)

这个信号在AGPn 协议中不使用,但是它用在PCI协议中由操作系统来管理。关于PME#的详细定义请参加PCI协议规范。

14.TYPEDET# Type Detect(类型检查)

从AGP发展来看,有1X、2X、4X和8X四种模式,每种模式所使用的电压也不尽相同,那AGP控制器怎么知到你插的是什么样的显卡呢?就是通过这个信号来告诉AGP Control的。用这个信号来设定当前显卡所需的电压。

15.FRAME# (I/O) Frame(周期框架)

在AGP管道传输时这个信号不使用,这个信号只用在AGP的快写方式。

16.IRDY# (I/O) Initiator Ready(起始者备妥)

这个信号说明AGPn Master已经准备好当前交易所需的数据,它只用在写操作,AGP Master不允许插入等待状态。

17.TRDY# (I/O) Target Ready(目标备妥)

这个信号说明AGPn Target已经准备好整个交易所需要读的数据,这个Target可以插入等待状态。

18.STOP# (I/O) Stop(停止)

这个信号在AGP交易时不使用。对于快写方式,当STOP#为Low时,停止当前交易。

19.DEVSEL# (I/O) Device Select(设备选择)

在AGP交易时不使用。在快写方式,当在一个交易不能完成时,它就会被使用。

20.REQ# (I) Request(请求)

这个信号用于向中裁器请求当前总线使用权为开始一个PCI orn AGP交易。

21.GNT# (O) Grant(保证)

当中裁器收到Initiator发出请求后,若当前总线为空闲,中裁器就会通过GNT#把总线控制权交给Initiator。

22.AD[31:0] (I/O) Address Data Bus(数据地址总线)

这些信号用来传输地址和数据。

23.C/BE[3:0]# (I/O) Command/Byte Enable(命令/位致能)

当一个交易开始时,提供命令信息。在AGPn Master做写交易时,提供有效的位信息。

四、Memory 接口信号说明

1.SCMDCLK[5:0] (O) Differential DDR Clock(时钟输出)

SCMDCLK与SCMDCLK#是差分时钟输出对,地址和控制信号都在这个两个Clock正负边沿的交叉点采样。每个DIMM共有三对。

2.SCMDCLK[5:0]# (O) Differential DDR Clock(时钟输出)

这个Clock信号的意义同上。

3.SCS[3:0]# (O) Chip Select(芯片选择)

当这些信号有效时,表示一个Chip已被选择了,每个信号对应于SDRAM的一行。

4.SMA[12:0] (O) Memory Address(内存地址)

这些信号主要用于提供多元的行列地址给内存。

5.SBA[1:0] (O) Bank Address(Bank选择)

这个些信号定义了在每个内存行中哪个Bank被选择。Bank选择信号和内存地址信号联合使用可寻址到内存的任何单元。

6.SRAS# (O) Row Address(行地址)

行地址,它和SCAS#、SWE#一起使用,用来定义内存的命令。

7.SCAS# (O) Column Address(列地址)

列地址,它和SRAS#、SWE#一起使用,用来定义内存的命令。

8.SWE# (O) Write Enable(写允许)

写允许信号,它与SRAS#、SCAS#一起使用,用来定义内存的命令。

9.SDQ[63:0] (I/O) Data Lines(数据线)

这些信号线用于传输数据。

10.SDM[7:0] (O) Data Mask(数据屏蔽)

当在写周期有效时,在内存中传输的数据被屏蔽。在这八个信号中每个信号负责八根数据线。

11.SDQS[7:0] (I/O) Data Strobe(数据选通)

这些信号主要用于捕获数据。这八个信号每个信号负责八根数据线。

12.SCKE[3:0] (O) Clock Enable(时钟允许)

这个信号在上电时对内存进行初始化,它们也可以用于关闭不使用的内存数据行。

五、HUB 接口信号说明

1.HL[10:0] (I/O) Packet Data(数据包)

这些信号主要用于Hub Interface读写操作时传输数据。

2.HISTRS (I/O) Packet Strobe(数据选通)

3.HISTRF (I/O) Packet Strobe Complement

这个信号与HISTRS一起在HUBn inteface上传输与接收数据。

六、LAN LINK接口信号说明

1.LAN_CLK (I) Lan I/F Clock(网络时钟)

这个信号由Lann Chipset驱动输出,它的频率范围在5~50Mhz。

2.LAN_RXD[2:0] (I) Received Data(接收数据)

这些信号是由Lan Chipset驱动输出到南桥。n

3.LAN_TXD[2:0] (O) Transmit Data(传输数据)

这些信号是南桥驱动输出到Lan Chipset。n

4.LAN_RSTSYNC (O) Lan Reset(Lan Chip 复位信号)

七、EEPROM 接口信号说明

1.EE_SHCLK (O) EEPROM Shift Clock(EEPROM时钟)

这个信号由南桥驱动输出到EEPROM。

2.EE_DIN (I) EEPROM Data In(EEPROM数据输入)

这个信号是由EEPROM传数据到南桥。

3.EE_DOUT (O) EEPROM Data Out(EEPROM数据输出)

这个信号是由南桥传数据到EEPROM。

4.EE_CS (O) EEPROM Chip Select(片选信号)

当这个信号有效时EEPROM被选择。

八、PCI接口信号说明

1.AD[31:0] (I/O) Address Data Bus(地址数据总线)

是用来传送起始地址。在内存或组态的交易期间,此地址的分辨率是一个双字组(Double Word)(即地址可被四整除),在读取或写入的交易期间,它是一个字节特定地址。

2.PAR (I/O) Parity Signal(同位信号)

在地址阶段完成后一个频率,或是所有写入交易的数据阶段期间,在IDRY#被驱动到僭态后一个频率,由Initiator驱动。所有读取交易的数据阶段期间,在TRDY#被驱动到僭态后一个频率,它也会被目前所寻址的Target驱动。在地址阶段完成后的一个频率,Initiator将PAR驱动到高或低态,以保证地址总线AD[0:31]与四条指令/位组致能线 C/BE#[0:3]是偶同位(Even Parity)。

3.C/BE[3:0]# (I/O) Command/Byte Enable(指令或字节致能)

由Initiator驱动,在AD Bus上传输地址时,用来表示当前要动作的指令。在ADn Bus上传输数据时,用来表示在目前被寻址之Dword 内将要被传输的字节,以及用来传输数据的数据路径。

4.RST# (O) PCI Reset(复位信号)

当重置信号被驱动成低态时,它会强迫所有PCI组态缓存器Master及Target状态机器与输出驱动器回到初始化状态。RST#可在不同步于PCI CLK边缘的状况下,被驱动或反驱动。RST#的设定也将其它的装置特定功能初始化,但是这主题超出PCI规格的笵围。所有PCI输出信号必须被驱动成最初的状态。通常,这表示它们必须是三态的。

5.FRAME# (I/O) Cycle Frame(周期框架)

是由目前的Initiator驱动,它表示交易的开始(当它开始被驱动到低态时)与期间(在它被驱动支低态期间)。为了碓定是否已经取得总线拥有权,Master必须在同一个PCI CLK信号的上边缘,取样到FRAME#与IRDY#都被反驱动到高态,且GNT#被驱动到低态。交易可以是由在目前的Initiator与目前所寻址的Target间一到多次数据传输组成。当Initiator准备完成最后一次数据阶段时,FRAME#就会被反驱动到高态。

6.IRDY# (I/O) Initiator Ready(备妥)

Initiatorn 备妥被目前的Bus Master(交易的Initiator)驱动。在写入期间,IRDY#被驱动表示Initiator准备接收从目前所寻址的Target传来的资料。为了确定Master已经取得总线拥有权,它必须在同一个PCI CLK信号的上升边缘,取样到FRAME#与IRDY#都被反驱动到高态,且GNT#被驱动到低态。

7.TRDY# (I/O) Target Ready(目标备妥)

Target备妥被目前所寻址的Target驱动。当Target准备完成目前的数据阶段(数据传输)时,它就会被驱动到低态。如果在同一个PCI CLK信号的上升边缘,Target 驱动TRDY#到低态且Initiator驱动IDRY#到低态的话,则此数据阶段便告完成。在读取期间,TRDY#被驱动表示Target正在驱动有效的数据到数据总线上。在写入期间,TRDY#被驱动表示Target准备接收来自Master的资料。等待状态会被插入到目前的资料阶段里,直到取样到TRDY#与IRDY#都被驱动到低态为止。

8.STOP# (I/O) Stop(停止)

Target驱动STOP#到低态,表示希望Initiator停止目前正在进行的交易。

9.DEVSEL# (I/O) Device Select(设备选择信号)

该信号有效时,表示驱动它的设备已成为当前防问的目标设备。换言之,该信号的有效说明总在线某处的某一设备已被选中。如果一个主设备启动一个交易并且在6个CLK周期内设有检测到DEVSEL#有效,它必须假定目标设备没能反应或者地址不存在,从而实施主设备缺省。

10.IDSEL (I) Initialization Device Select(初始化设备选择)

IDSEL是PCI装置的一个输入端,并且在存取某个装置的组态缓存器期间,它用来选择芯片。

11.LOCK# (I/O) Lock(锁定)

这是在一个单元(Atomic)交易序列期间(列如:在读取/修改/写入操作期间),Initiator用来锁定(Lock)目前所寻址的Target的。

12.REQ# (I) Request(请求)

表示管理者要求使用总线,此为一对一之信号,每一管理者都有与其相对应之REQ#信号。

13.GNT# (O) Grant(保证)

表示管理者对总线使用之要求已被同意,此为一对一之信号,每一管理者都有与其相对应之GNT#信号。

九、Serial ATA接口信号说明

1.SATA0TXP (O) Serial ATA 0 Transmit(串行ATA0 传送)

2.SATA0TXN (O) Serial ATA 0 Transmit(串行ATA0 传送)

这个信号与SATA0TXP组成差分信号对,用于传输数据。

3.SATA0RXP (I) Serial ATA 0 Receive(串行ATA0 接收)

4.SATA0RXN (I) Serial ATA 0 Receive(串行ATA0 接收)

这个信号与SATA0RXP组成差分信号对,用于接收数据。

5.SATARBIAS (I) Serial ATA Resistor Bias(串行ATA电阻偏置)

6.SATARBIAS# (I) Serial ATA Resistor Bias(串行ATA电阻偏置)

这个信号与SATARBIAS一样外接一颗与GND相接的电阻,为SATA提供一个电压偏置。

7.SATALED# (OD) SATA Drive Activity Indicator(SATA 读写指示)

当这个信号为Low时,表示当前的SATA硬盘正在读写数据。

十、IDE 接口信号说明

1.DCS1# (O) Device Chip Select(设备芯片选择)

这个信号为设备选择信号For Rang 100 。

2.DCS3# (O) Device Chip Select(设备芯片选择)

这个信号为设备选择信号 For Rang 300。

3.DA[2:0] (O) Device Address(设备地址)

这些信号用于传输地址信号。

4.DD[15:0] (I/O) Device Data(设备数据)

这些信号用于传输数据信号。

5.DREQ (I) Device Request(设备请求)

当IDE Device要做一个DMA读写动作时,就会驱动这个信号向南桥发DMnA请求。

6.DACK# (O) Device DMA Acknowledge(设备DMA确认)

当IDEn Device已做了一个DMA请求后,若当前总线空闲,南桥就会驱动个信号,把控制权受权给IDE Device。

7.DIOR# (O) Disk I/O Read(磁盘I/O读)

这个信号由南桥来驱动,当它有效时,表示要对磁盘进行一个读操作。

8.DIOW# (O) Disk I/O Write(磁盘I/O写)

这个信号由南桥来驱动,当它有效时,表示要对磁盘进行一个写操作。

9.IORDY (I) I/O Channel Ready(I/O通道备妥)

这个信号由IDEn Device来驱动,当它有效时,表示IDE Device已经准备OK。

十一、LPC接口信号说明

1.LAD[3:0] (I/O) LPC Command、Address、Data

这四信号线用来传输LPCn Bus的命令、地址和数据。

2. LFRAME# (I/O) LPC Frame(LPC框架)

当这个信号有效时,指示开始或结束一个LPC周期。

3.LDRQ# (I) DMA Request(DMA请求)

当Super I/O上的Device需要用DMA Channel时,就会驱动这个信号向南桥发出请求。

十二、USB 接口信号说明

1.USBP+ (I/O) USB Signal(USB 信号)

2.USBP- (I/O) USB Signal(USB 信号)

这个信号与USBP+组成差分信号对,组成一个USB Port,用来传输地址、数据和命令。

3.OC# (I) Over Current(过电流保护)

当有USBn Device过电流时,这个信号会拉Low,告知南桥有过电流发生。

十三、SMBus接口信号说明

1.SMBDATA (I/O) SMBus Data(数据线)

2.SMBCLK (I/O) SMBus Clock(时钟线)

上面两个信号线为系统管理总线,以南桥为控制中心,对主机板的一些Device进行读写操作,如倍频IC、SPD等等。这两个信号在外部必须通过电阻进行Pull High。

十四、AC-Link接口信号说明

1.RST# (O) Reset(复位信号)

这个讯信号由南桥驱动,对Audion Chip进行初始化。

2.SYNC (O) Sync(同步信号)

3.BIT_CLK (I) Bit Clock(时钟输入)

这是一个由Codec产生一个12.288Mhz串行数据时钟给南桥。

4.SDOUT (O) Serial Data Out(串行数据输出)

由南桥发出数据到Codec。n

5.SDIN (I) Serial Data In(串行数据输入)

由Codec发出数据到南桥。

十五、FDC接口信号说明

1.DRVDEN0 (OD) Drive Density Select Bit(驱动器密度选择位)

驱动器密度选择信号。

2.INDEX# (I) INDEX(索引)

此Pin为施密特触发器输入,当这个为Low(有效时),通过索引孔把磁头定位起始磁道。

3.MOA# (OD) Motor A On(马达A打开)

当此信号为Low时,马达A起动。

4.DSA# (OD) Drive Select A(驱动A选择)

当此信号为Low时,驱动器A被选择。

5.DIR# (OD) DIR(列目录)

磁头步进马达移动方向,为High时,向外移动,为Low时向内移动。

6.STEP# (OD) Step(步进)

步进输出脉冲,当此信号为Low时,将产生一个脉冲移动磁头到另一个磁道。

7.WD# (OD) Write Data(写数据)

写数据,当此信号为Low时,写数据到被选择的驱动器。

8.WE# (OD) Write Enable(写允许)

写允许,当为Low表示允许写入盘片。

9.TRACK0# (I) Track 0(0磁道)

0磁道,当此信号为Low时,磁头将被定位到最外的一个磁道(0磁道)。

10.WP# (I) Write Protected(写保护)

写保护,当此信号为Low时,磁盘片被写保护,只能读出数据不能写入。

11.RDATA# (I) Read Data(读数据)

当为Low时从软盘读数据。

12.HEAD# (OD) Head(磁头)

磁头选择,当为High时选择0面的磁头,当为Low时选择1面的磁头。

13.DSKCHG# (I) Diskette Change(更换磁盘)

盘片更换,当此信号为Low时,在上电状态可随时取出盘片。

十六、Parallel Port 接口信号说明

1. SLCT (I) Printer Select Status(打印机状态选择)

这个Pin主要用于选择打印机模式,为High时,表示打印机被选择。打印有两种模式可以被设定ECP和EEP。

2. PE (I) Page End(页面结束)

当这个信号为High时,表示打印机已检测到页面结束。

3. BUSY (I) Busy(打印机忙)

当这个信号为High时,表示打印机很忙没有准备去接收数据。

4. ACK# (I) Acknowledge(确认)

当这个信号为Low时,表示打印机已接收数据,并准备接受更多的数据。

5. ERR# (I) Error(错误)

当这个信号为Low时,表示打印机在打印时出错。

6. SLIN# (O) Printer Select(打印机选择)

这个信号为打印机输出线检查。

7. INIT# (O) Initialization(初始化)

当这个信号为Low时,表示对打印机进行初始化。

8. AFD# (O) Auto Line Feed(自动走线)

当打印机打印针出问题时,这个信号会被拉Low,打印机会自动再打一遍。

9. STB# (O) Strobe(锁定)

当这个信号为Low时,表示要把并行数据锁定到打印机里。

10. PD[7:0] (I/O) Printer Data(打印机数据)

这些信号用于传输打印机数据。

十七、Serial Port 接口数据说明

1.CTS# (I) Clear To Send(清楚发送)

这个信号用于Modem控制输入,这个功能可以通过读握手状态寄存器Bit 4来测试。

2.DSR# (I) Data Set Ready(数据准备)

这个信号为Low时,表示Modem或数据放置已准备可以传输数据。

3.RTS# (I/O) Request To Send(请求发送)

这个信号为Low时,表示Modem或调制解调器可准备去发送数据。

4.DTR# (I/O) Data Terminal Ready(数据终端准备)

这个信号为Low时,表示数据终端已准备可以进行通信。

5.SIN (I) Serial Data In(串行数据输入)

这个信号用于去接收数据。

6.SOUT (O) Serial Data Out(串行数据输出)

这个信号用于去发送数据。