逻辑综合其实可以很简单,下面以github上一个riscv core cv32e40p的代码(

https://github.com/openhwgroup/cv32e40p

)为例介绍一下怎么从零开始做综合。

一、先找到RTL

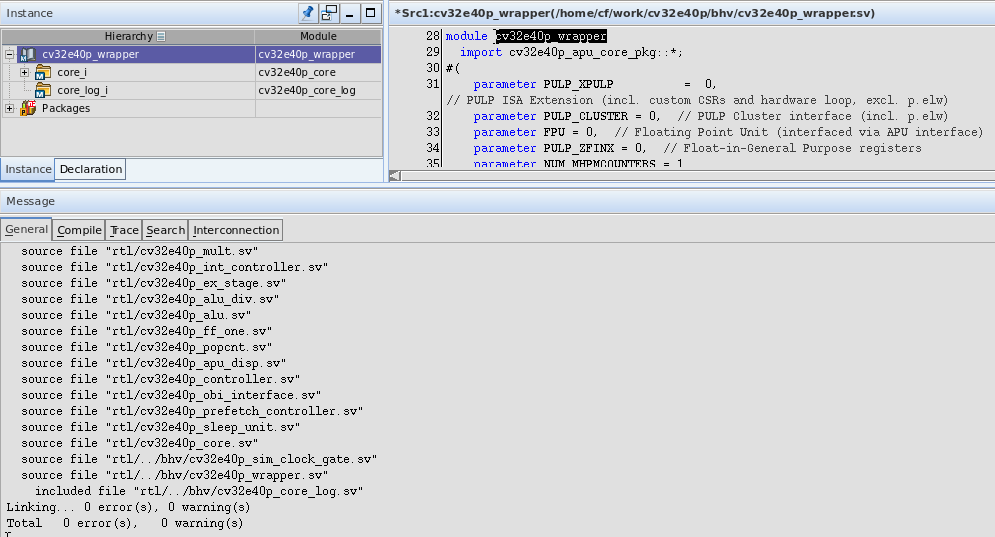

很幸运,在这个开源项目的根目录里,正好有一个file list:cv32e40p_manifest.flist。尝试用verdi打开看看是否缺文件:

export DESIGN_RTL_DIR=rtlverdi -sv -f cv32e40p_manifest.flist

二、阅读getting start文档

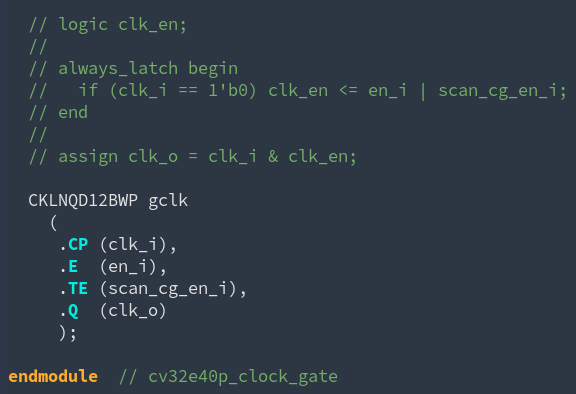

按照文档里的描述,需要把bfm里仿真用的clock gate换成具体工艺里的icg。

文档链接:

https://docs.openhwgroup.org/projects/cv32e40p-user-manual/getting_started.html

三、写综合脚本

set top cv32e40p_coreset_svf ${top}.svf

set stdlib_path ../libset ss_lib wc.dbset search_path [concat $search_path $stdlib_path]set target_library [list $ss_lib]set synthetic_library [list dw_foundation.sldb]set link_library [list * $ss_lib $synthetic_library]

analyze -format sverilog -vcs " +incdir+../rtl/include +incdir+../rtl/../bhv +incdir+../rtl/../bhv/include +incdir+../rtl/../sva" { ../rtl/include/cv32e40p_apu_core_pkg.sv ../rtl/include/cv32e40p_fpu_pkg.sv ../rtl/include/cv32e40p_pkg.sv ../rtl/../bhv/include/cv32e40p_tracer_pkg.sv ../rtl/cv32e40p_if_stage.sv ../rtl/cv32e40p_cs_registers.sv ../rtl/cv32e40p_register_file_ff.sv ../rtl/cv32e40p_load_store_unit.sv ../rtl/cv32e40p_id_stage.sv ../rtl/cv32e40p_aligner.sv ../rtl/cv32e40p_decoder.sv ../rtl/cv32e40p_compressed_decoder.sv ../rtl/cv32e40p_fifo.sv ../rtl/cv32e40p_prefetch_buffer.sv ../rtl/cv32e40p_hwloop_regs.sv ../rtl/cv32e40p_mult.sv ../rtl/cv32e40p_int_controller.sv ../rtl/cv32e40p_ex_stage.sv ../rtl/cv32e40p_alu_div.sv ../rtl/cv32e40p_alu.sv ../rtl/cv32e40p_ff_one.sv ../rtl/cv32e40p_popcnt.sv ../rtl/cv32e40p_apu_disp.sv ../rtl/cv32e40p_controller.sv ../rtl/cv32e40p_obi_interface.sv ../rtl/cv32e40p_prefetch_controller.sv ../rtl/cv32e40p_sleep_unit.sv ../rtl/cv32e40p_core.sv ../rtl/cv32e40p_clock_gate.sv}elaborate ${top}check_designuniquify

source -echo -verbose ../constraints/cv32e40p_core.sdccheck_timing

compile

report_constraints -all_violators > vio.rptreport_area -nosplit -hierarchy > area.rpt

change_names -rules verilogwrite_file -format verilog -hierarchy -output ${top}_syn.vwrite_sdc -nosplit ${top}_syn.sdc

四、运行脚本

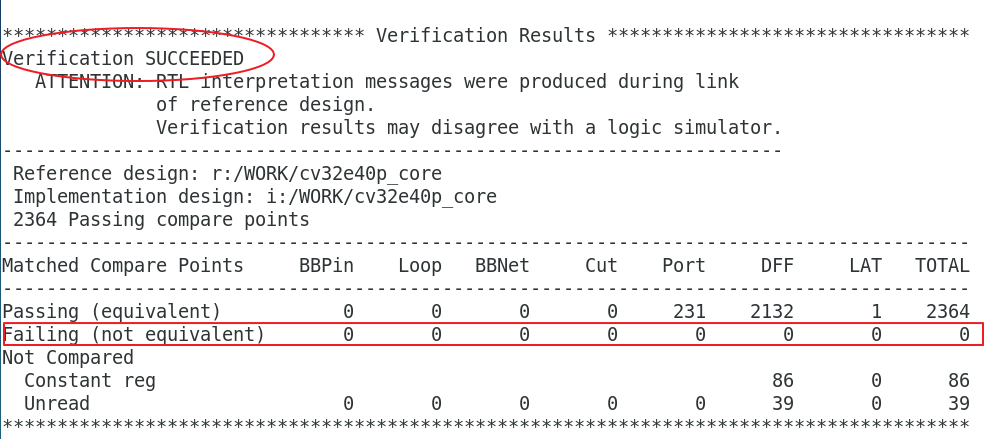

五、确认RTL与网表逻辑一致

鼠标点点,结果如下图:

作者:陈锋

来源:ExASIC

版权归原作者所有,如有侵权,请联系删除