9月9日,在无锡举办的2019年中国半导体封装测试技术与市场年会上,中国工程院院士许居衍发表了《复归于道-封装改道芯片业》的精彩演讲。

许院士指出,半个多世纪以来,在摩尔定律的指导下,业界努力朝着芯片面积更小、晶体管数量更多的方向迈进,深刻地革新了现代社会的方方面面。

然而,业界对单片集成的狂热追求已经偏离了“正道”,正面临着严峻的挑战和风险。

当前,3D 集成和多片异构集成技术正在成熟,有望在不远的将来引导业界重回“正道”,为整个半导体行业带来更深层次的技术变革。

演讲伊始,许院士历数了集成电路发展历程中的几个关键节点,从登纳德缩放定律(Dennard Scaling)引领时钟频率(clock rate)狂飙突进,到 4 GHz 止步;

从单核处理器向多核处理器发展;

从 CPU + GPU 单片同构集成向多片异构集成演进;

苹果 A10 处理器采用了台积电(TSMC)的集成扇出(InFO)先进封装技术;

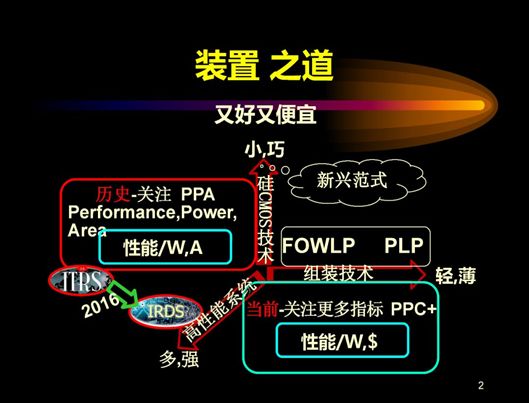

2016年国际半导体技术路线图(ITRS)宣布不再以摩尔定律(ML)为目标;

从 ITRS 到国际器件与系统路线图(IRDS),业界的关注重心也在迁移。

许院士指出:

“历史事件犹如枝上嫩芽,总在它要长出的地方露头,结出果子。

”异构计算激发多芯片先进封装(MCP),有望带来新产业生态系统和新商业模式。

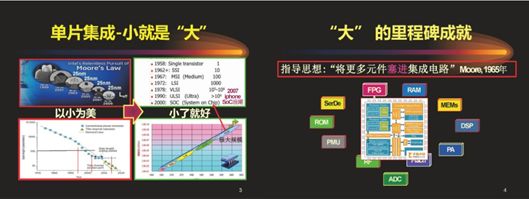

纵观半导体集成电路数十年的发展历史,也基本上算是单片集成的历史,可以总结出极为明晰的发展哲学:

装置之道在于“又好又便宜”,业界关注重点从 PPA(性能、功耗和面积)转向 PPC+(性能、功耗、成本、etc.)。

“便宜”容易理解,那什么是“好”?

对于当前的业界,好就是“又小又大”,“小”就是“大”。

所谓“小”,晶体管的尺寸越来越小。

半导体制程半个多世纪以来沿着摩尔定律稳步减小,从诺伊斯(Robert Noyce)和基尔比(Jack Kilby)发明集成电路的久远年代,到99年的 0.18 μm,再到目前尚未量产的 5 nm,甚至 1 nm 制程在实验室里也早已不是神话。

所谓“大”,集成度越来越大。

芯片面积保持不变或略有减少的情况下,放进越来越多的晶体管:

从肖克利(William Shockley)发明晶体管,到后来极大规模集成电路(ULSI)、系统级芯片(SoC)和专用芯片(ASIC),单一芯片内部的晶体管数目已经高达百亿。

当今社会的一切电子产品,小到随处可见的手机电脑,大到互联网、物联网乃至人工智能所依托的数据中心服务器,再到执行人类登月计划的超级计算机,其背后都有集成电路的身影,集成电路的大发展彻底地改变了我们的生活。

然而,业界一直以来奉为圭臬的单片集成哲学早已偏离了“初衷”:

电子系统的基本要求是使用最经济的资源,实现最理想的功能。

这包括内架构与外环境的优化、高性能与低功耗的兼顾、小体积与长寿命的融合。

业界一直以来所重视的PPA和PPC逻辑已然迷了路。

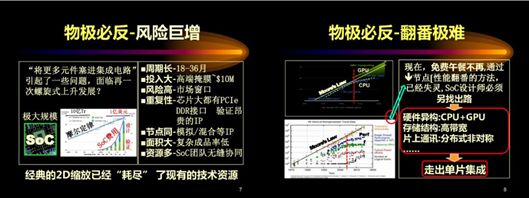

首先,半导体制程已进入10 nm 以下,再进一步微缩将会触及物理学和经济学的双重极限。

沟道长度(channel length)在该尺度上,已经无法忽视量子隧穿所带来的漏电流问题,即便鳍式场效应晶体管(FinFET)和环绕栅极(Gate-All-Around)也回天乏术。

而半导体制造光刻工艺需要极端苛刻的光刻精度,极紫外光线(EUV)光刻机的研发也困难重重。

制程进一步微缩所需要的研发经费已呈指数级增长,制造工艺所要求的高端掩模的价格急剧攀升,极端复杂的集成度也进一步拉低了芯片良率,盈利风险越发明显。

经典的 2D 缩放已经“耗尽”了现有的技术资源。

其次,最新制程的研发时间再难以遵循摩尔定律,以“翻番”闻名于世的摩尔定律已经日薄西山,业界只能摒弃单片集成,转而寻找新的出路。

比如异构集成(heterogeneous integration)、片上网络(NoC)、硅通孔(TSV)、3D 封装乃至模块化芯粒(chiplet)集成等。

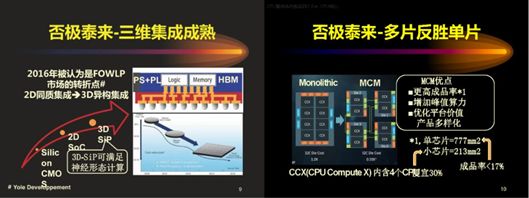

当前3D 集成技术日渐成熟,业界已经意识到 2D 同构集成向 3D 异构集成转变的优越性。

2016年,苹果 A10 处理器率先采用了扇出型晶圆级封装(FOWLP)技术,推动 FOWLP 技术成为业界焦点。

而 3D 系统级封装(3D SiP)则能为人工智能深度学习提供助力。

3D 集成与封装技术的进步使在单个封装(包含采用多项技术的芯片)内构建复杂系统成为可能,成为了业界走出单片集成、实现逻辑复归的契机。

从单片(Monolithic)到多片(MCM),不仅成品率显著提升,成本下降,峰值算力也得以突破单片屏障。

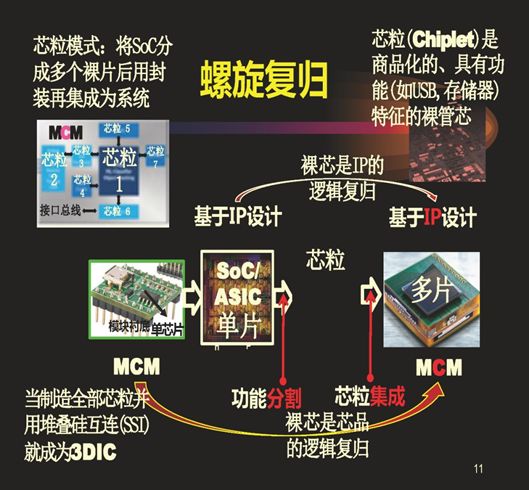

这里要提一下“芯粒”(chiplet)。

芯粒是商品化的、具有特定 IP (知识产权)的未经封装的裸芯片。

芯粒可以像搭积木一样通过先进的集成技术封装在一起,形成一个新型 SoC。

芯粒模式,实质上讲就是硅片级别(硬 IP)的复用,区别于传统 SoC里面软件级别(软IP)的复用,实现了“MCM”到“MCM”的逻辑复归。

前者的C表示软 IP,后者的C表示硬 IP。

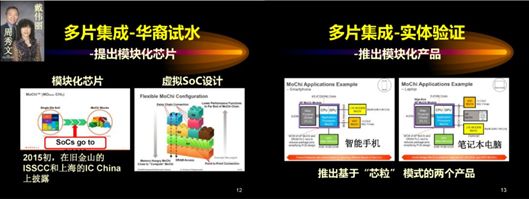

早在2015年就有华裔专家进行了多片集成的尝试,不仅提出模块化芯片的构想,还推出了基于“芯粒”的模块化产品。

2017年 DARPA 在电子复兴计划(ERI)中启动了名为通用异构集成及知识产权复用策略(CHIPS)的项目,旨在通过混合和匹配即插即用式芯粒构建一个模块化的计算框架。

2018年,多家公司成立了开放特定领域架构组织(ODSA),希望制定芯粒开放标准,促进形成芯粒生态系统。