文章链接:https://www.sciencedirect.com/science/article/pii/S0927796X24001232

单片三维集成电路

已经出现了三种主要的三维集成类型:硅通孔 (TSV) 集成、晶圆到晶圆 (W2W) 或芯片到晶圆 (D2W) 键合以及单片 3D (M3D) 集成。TSV 集成依赖于通常由铜 (Cu) 或钨 (W) 制成的垂直互连,嵌入硅基板内以连接堆叠的器件层。硅是用于器件层的主要半导体材料。W2W 和 D2W 键合通过在晶圆或芯片级对准和键合预制层来实现集成。对于 W2W 和 D2W 键合,通常使用SiO2和低κ 电介质材料来支持电气隔离和结构完整性。虽然这些方法通过缩短互连来提高性能,但它们面临着与对准精度、异构接口和热预算限制相关的挑战。

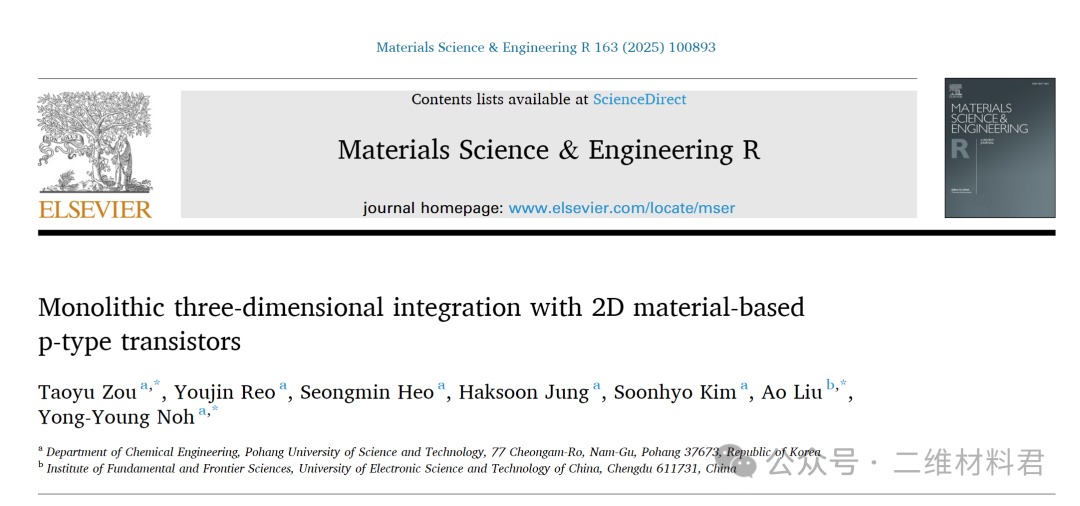

相比之下,M3D 集成可以在单个基底上顺序制造多个器件层,实现原子级对准,同时将层间寄生效应降至最低。这种架构降低了功耗,增强了信号完整性,并且比 TSV 和基于键合的技术具有更高的集成密度。此外,M3D 集成为整合 2D 材料提供了一个无缝的平台,这些材料非常适合超薄晶体管层,并提供卓越的短沟道效应控制。与基于硅通孔的 3D 集成相比,这些基于 2D 的 M3D 集成的集成密度高出十倍以上,比传统的 M3D 集成提高了 150%(图 16 a)。这些优势使基于 2D 的 M3D 集成成为在未来电子系统中实现紧凑、高性能和节能电路的有希望的途径。

图 16。(a) TSV-3D、传统 M3D 和拟议的 2D-M3D 的估计层厚度和集成密度。(b) 通过逐层 vdW 组装垂直集成的多层功能设备,包括存储器、逻辑和传感器。 (c) 通过 MoS2沟道和电路层的多循环层压集成的 10 层 M3D 系统示意图。 (d) 10 层 M3D 系统的相应光学图像。比例尺:30 µm。

M3D 与 2D p 型晶体管集成的发展已从机械剥离进展到大规模制造,从而实现了多层堆叠和环栅 (GAA) 架构。最初使用剥离式 2D 材料的尝试证明了具有互补 p 型沟道的 MoS2垂直 FET(例如 WSe2和 Bi2Sr2Co2O8)的可行性,为早期 3D 系统提供了概念验证。通过 CVD 等技术向晶圆级制造的过渡使得能够实现具有垂直堆叠的 n-FET 和 p-FET 的 CFET。最近在具有嵌入式传感和存储功能的多功能 M3D 集成电路多层堆叠方面取得的突破,凸显了 M3D 平台内计算和功能的融合。最新的进展涉及 GAA 架构,其中栅极长度缩小至 41 纳米,使用高迁移率 NMOS 和 PMOS 晶体管以及高 k 电介质来增强性能。因此,通过结合多层 2D 材料,可以开发高度紧凑、高效和多功能的电子系统,以充分发挥与 CMOS 兼容的 3D 架构的潜力。

2D NMOS的M3D集成

各种典型的二维材料,如 MoS2 、 hBN 和少层石墨烯,分别用作半导体、电介质和接触/栅极材料。这些材料可以通过逐层堆叠工艺组装成垂直集成的多层器件,从而创建 16 个独立二维材料层的示意堆叠(图 16b)。该技术实现了全二维多功能设备的垂直集成,包括存储器、逻辑和传感器功能。然而,依赖于机械剥离和转移方法的制造工艺很复杂并且仅限于小规模。为了解决这一限制,通过将 CVD 生长的 MoS2 层依次转移到基板上,实现了垂直堆叠的 NAND 和 NOR 逻辑电路,确保了精确对准并实现了紧凑逻辑设计的多层集成。与传统平面架构相比,这些电路表现出清晰的逻辑功能并提高了面积效率。最近报道了一种使用一步范德华转移法的替代低温 M3D 集成方法(图 16c-d)。在该方法中,在牺牲晶圆上预制低κ层间电介质、电极、栅极电介质、互连和垂直通孔等基本组件。然后,将这些组件释放并在 120°C 下层压到 2D 半导体上,以防止损坏 2D 晶格。使用这种方法,成功集成了具有 10 个电路层的大规模 M3D 系统。电气特性表明,与传统工艺不同,即使添加多个层后,底部的 2D 晶体管仍不受影响。通过垂直互连不同层的设备,实现了各种协同功能,包括存储器上的逻辑和逻辑上的传感器。这种低能耗、逐层范德华层压方法为二维半导体和其他与传统工艺不兼容的新兴材料的 M3D 集成带来了有希望的进步。人们已经研究和探索了使用 n 型二维晶体管的 M3D 器件在各种应用中的潜力,包括逻辑功能、高密度存储器和人工智能处理硬件。

将二维材料与硅基工艺相结合,为推进单片三维集成和光电子学提供了新的机遇。将 p 型绝缘体上硅晶体管与 n 型 MoS 2晶体管相结合的异质 CFET 展示了如何通过堆叠栅极调制和迁移率调整来缓解迁移率失配,在 3 V 电源电压下实现 142.3 的电压增益,同时保持较低的热预算。除了传统电子学之外,这些架构还利用二维材料的能带结构和光响应性扩展到光电子学领域,实现集成电路中的光电探测器等应用。补充研究强调需要优化二维材料以满足与硅兼容制造的要求,解决接触电阻、费米能级钉扎和掺杂不一致等挑战。

2D CMOS的M3D集成

最近,结合 n 型和 p 型 2D 晶体管的 M3D 集成电路取得了重大进展,进一步提高了其性能和应用范围。早在 2016 年,Sachid 等人就展示了 MoS2(n 型)和 WSe2(p 型)晶体管的 M3D 集成(

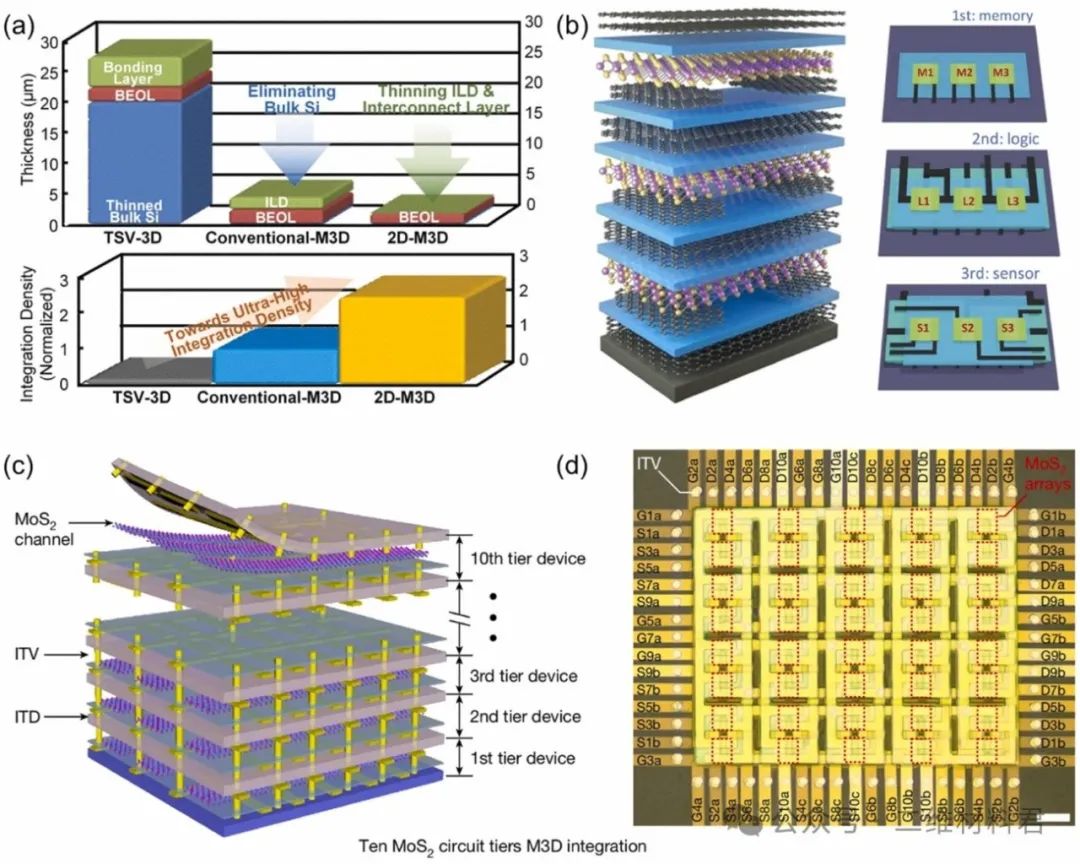

图 17a-b ),方法是将机械剥离的 MoS2转移到 Si/SiO2基底上,然后用 XeF2蚀刻进行图案化,并沉积源/漏极和 ZrO2栅极氧化物。对于第二层,WSe2以类似的方式被转移、图案化和金属化。该过程产生具有独立栅极的垂直堆叠晶体管,从而可以创建 M3D 集成电路,包括反相器、NAND 和 NOR 逻辑门,以及差分放大器和共源放大器等模拟电路。这些M3D结构设计将集成密度显著降低至约42%-46%(图17c)。

图 17。(a) 共享栅极 M3D CMOS 结构的 HRTEM 图像。 MoS2和 WSe2区域的 EDS 映射。 (b) 模拟电路底层和顶层的光学图像。 (c) 平面 CMOS 和堆叠 CFET 技术公共电路单元的面积比较。 (d) 基于 2D CFET 的反相器的静态功率的箱线图和比较。 (e) CFET 4 T SRAM 的布局图像和功能。 比例尺:10 μm。 (f) 基于 CFET 设计的半加器的电路原理图、布局图像和功能。 比例尺:10 μm。

最近的进展使得用于 M3D 集成电路的 p 型 2D 材料的大规模生长成为可能。这种发展使得可以精确控制材料特性和层对齐,从而提高 p 型晶体管的性能和可靠性。2022 年,Xiong 等人通过 CVD在 SiO2 /Si 衬底上直接沉积大单晶单层或双层 WSe2,进一步推进了用于低功耗集成电路的 3D 堆叠 CFET 。一个关键的制造步骤是在氩气气氛下在 200°C 下进行后金属退火,以优化顶栅 p-WSe2的性能。该工艺在 VD = −2 V 时实现了创纪录的594 μA/μm 的I on,沟道长度为 135 nm。由于 p-WSe2和 n-MoS2晶体管的对称阈值电压,基于 CFET 的反相器表现出全输出摆幅行为、轨到轨操作和低于纳瓦的低功耗,从而导致电压增益高达 18 V/V 且静态功耗低 (< 2 nW)(图 17d)。此外,4 T SRAM 电路在蝴蝶曲线中表现出双稳态交叉点,噪声裕度超过 80%(图 17e),16 T 半加器电路使用 3D 架构确认了数字逻辑门的功能性(图 17f)。这些进步凸显了采用 CVD 生长 2D 材料的 CFET 在先进、低功耗、高性能 M3D 集成电路中的潜力。

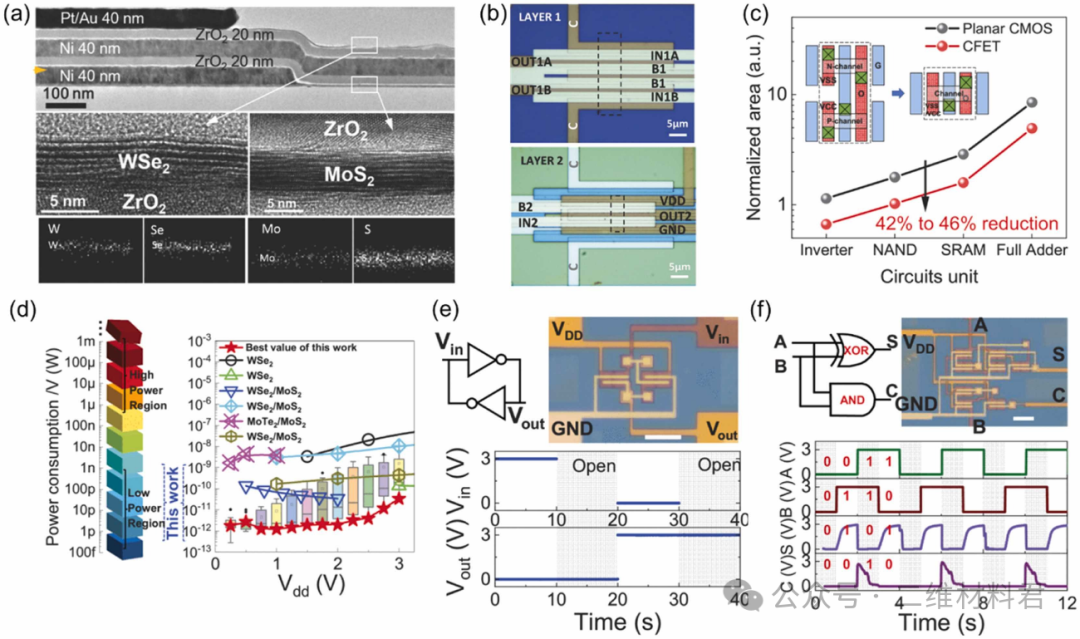

开发 M3D 与 2D p 型晶体管集成的主要挑战之一是缺乏可控的 p 掺杂 2D 半导体掺杂方案,这严重阻碍了互补逻辑电路的扩展。最近,通过将 TMD(如 MoS2)放置在 vdW 反铁磁绝缘体 CrOCl 之上,取得了突破。这使得通过强 vdW 界面耦合可以将 MoS2中的载流子极性从 n 型重新配置为 p 型。所得晶体管的室温空穴迁移率高达约 425 cm2/Vs,开/关比达到 106,并且在空气中稳定运行一年以上。该方法有助于构建垂直集成的互补逻辑电路,包括具有六个 vdW 层的反相器、具有 14 个 vdW 层的 NAND 和具有 14 个 vdW 层的 SRAM(图 18a)。这一进展对于基于二维逻辑门的 M3D 集成电路的未来至关重要,为更复杂、更高效的电子设备铺平了道路。然而,这种方法依赖于机械剥离的二维材料,这可能会限制可扩展性。

图 18。(a) 具有垂直反向极化场效应晶体管的未来 M3D 集成电路展望。 (b) “摩尔定律”和“超越摩尔定律”技术中 2D FET 3D 集成潜力示意图。 (c) 三层芯片的光学图像。插图是三层 3D 设备堆栈之一的假彩色 SEM 图像的顶视图。

为了解决可扩展性问题,已经展示了使用大面积生长的 MoS2和 WSe2进行多功能 2D FET 的 M3D 集成,以实现晶圆级 M3D 集成(图 18b-c)。这包括晶圆级双层集成,每层超过 10,000 个 MoS2 FET,三层集成,第 1 层和第 2 层有 800 个 MoS2器件,第 3 层有450 个 WSe2器件,以及每层超过 200 个缩放 MoS2 FET 的双层集成,沟道长度为 45 纳米。此外,还展示了具有 M3D 反相器、存储器、存储和光传感功能的 3D 电路。这是第一个使用大面积生长的 2D 材料的三层 3D 芯片和晶圆级 3D 集成。然而,这项工作也存在一些缺点:WSe2 FET 表现出双极传输,p 型导电占主导地位,而且 WSe2晶体管的性能在I on 中值、SS 值和器件间差异方面仍然低于 MoS2。此外,转移薄膜中存在应变效应。Das 团队进一步展示了 CMOS 电路的 M3D 集成,实现了垂直堆叠的逻辑门,如反相器、NAND 和 NOR 门。使用双层结构,在第一层制造 n-FET,在第二层制造 p-FET,通过 300 nm 宽的层间通孔以 1 μm 间距连接。低温制造(<200 °C)确保与 BEOL 工艺的兼容性,而 MOCVD 生长的 WSe2可在各层之间提供均匀的沟道层。优化的 Pd 和 Ni 接触可实现互补的 p 型和 n 型行为。

栅极控制是 M3D 集成中的关键组件,因为它直接决定了静电控制。有效的栅极调制对于最小化短沟道效应、抑制漏电流以及确保晶体管在纳米级尺寸下稳定运行至关重要。GAA 结构已成为一种关键解决方案,它通过用栅极完全包围沟道来提供卓越的控制,从而最大限度地提高调制效率并提高电流处理能力。基于纳米片的 GAA 晶体管利用由 2D 材料(例如 WSe2和 MoS2)形成的堆叠沟道,栅极包裹在每一层周围。这种架构不仅增强了栅极控制,而且还增加了导通电流密度,同时保持了较小的器件占用空间,这对于 M3D 集成至关重要。例如,具有单层 MoS2沟道的 GAA 晶体管已展示出 410 µA/µm 的导通电流,具有出色的漏极感应势垒抑制和低关断漏电流,证实了该设计具有卓越的静电性能。 GAA 结构的进一步发展包括垂直堆叠的 CFET,由 p 型 WSe2和 n 型 MoS2纳米片构成。这些 CFET 显著减少了占用空间,电流密度超过 700 µA/µm。

2023 年,首个使用 WSe2纳米带的 PMOS GAA 晶体管被演示,这意味着二维材料在 CMOS 缩放方面的潜力。该器件由转移到源极和漏极电极上的 2-4 层 WSe2