文章链接:https://onlinelibrary.wiley.com/doi/10.1002/aelm.202400386

摘要

基于过渡金属二硫族化物(TMDCs)的首次大规模p型浮栅场效应晶体管(FGFET)存储阵列已成功制备。通过化学气相沉积生长的无缝共平面2H-和1T′-MoTe2分别作为沟道和源/漏电极,高介电常数Al2O3层作为隧道层和阻挡层。阵列式的Pd/Au用作浮栅和顶栅。该器件的整体性能在已报道的TMDCs基FGFET存储器中表现优异。典型器件在±10 V和±5 V的栅极电压扫描范围内分别表现出约11.5和2.8 V的大存储窗口,以及约104和103的开关比,具有超过105秒的长保留时间和超过5×104次编程/擦除循环的良好应力耐受性。通过施加短时的±5 V电压脉冲,可精确调节器件的电导。该器件的良品率分别在±10 V和±5 V条件下达到100%和93%。整个制造过程无需转移,且与传统硅技术兼容。此项工作为TMDCs在大规模集成电路中的应用铺平了道路。

研究背景和主要内容

非易失性存储器(NVM)是一种重要的信息存储器件,在民用电子产品中得到了广泛的应用。浮栅场效应晶体管(FGFET)是一种典型的NVM结构,具有工作电压低、编程/擦除速度快、数据保持时间长、抗应力性能好等特点。在FGFET存储器中,当在栅极电极上施加电压时,电子(空穴)可以从沟道穿过隧道氧化物隧穿到浮栅,并且在栅极电压(VG )移除后仍能在那里保持很长时间,表现出非易失性。

过渡金属二硫属化物 (TMDC) 具有原子级薄的厚度、相对较弱的非平面范德华相互作用和没有悬挂键的原子级锐利表面,可以堆叠在任意基底上而不需要晶格匹配要求,成为实现高密度、低功耗集成器件的有希望的候选材料。最近,各种基于 TMDC 的非易失性存储器件已被成功制备 ,它们被认为是硅基存储器件的有希望的补充。例如,Simone Bertolazzi 等人展示了基于剥离n -MoS2的FGFET 存储器件,其中他们使用石墨烯代替金属作为接触电极以提高器件性能。Taro Sasaki 等人报道了一种使用 MoTe2作为沟道材料、以h -BN 作为隧道层的FGFET 存储器件。然而,在大多数的工作中,TMDCs都是被机械剥离的,这限制了它们在大规模器件集成中的进一步应用。

2017 年,Quoc An Vu 等人首次报道了一种基于大面积化学气相沉积 (CVD) 合成单层 MoS2的 FGFET 存储器阵列,推动了基于 TMDCs 的存储器器件的实际应用。2020 年,Migliato Marega 等人展示了一种基于大规模 CVD 合成单层n -MoS2的新型逻辑存储器阵列,其中典型存储器窗口在±12.5 V 的V G扫描范围内约为 10.6 V。据我们所知,到目前为止,所有关于基于 TMDCs 的存储器阵列的工作都使用了 CVD 生长的 MoS2和与基于硅的加工技术不兼容的转移工艺。此外,大多数已报道的基于 TMDCs 的非易失性存储器件都是 n 型。在实际的集成电路中,需要互补(即n型和p型)存储器。P 型和 n 型存储器器件可以组合形成基于浮栅的可编程 CMOS,这为集成更复杂的系统创造了新的可能性。然而,目前尚未见基于 TMDCs 的p型存储器阵列的报道。

在本工作中,我们制备了一种基于半导体 2H-MoTe2的大规模p

型 FGFET 存储器阵列,该存储器阵列具有无缝共面金属 1T′-MoTe2接触,该接触通过 CVD 方法直接在器件衬底上合成。异相结构表现出类欧姆接触行为,并且接触电阻低。高κ Al2O3层充当隧穿层和阻挡层。Pd/Au(6/6 nm)薄膜充当电荷存储浮栅。另一层 Pd/Au(10/50 nm)薄膜用作顶栅。FGFET 的栅极传输特性具有高度的一致性。在已报道的基于 TMDC 的 FGFET 存储器中,器件的整体性能非常出色。典型器件在栅极电压扫描范围±10 和±5 V 内表现出约11.5 和2.8 V 的大存储窗口、约104和103的开/关比,并具有超过105 s 的长保持时间和超过5 × 104 次编程/擦除循环的良好应力耐受力。此外,通过施加脉冲宽度为2 ms、幅度为5 V 的栅极电压脉冲可以精细地控制存储器件的电导。值得注意的是,该类型的FGFET 可以在低至±5 V 的工作电压下工作,这具有实际意义,因为5 V 是半导体集成电路中标准互补金属氧化物半导体(CMOS)器件的工作电压。对 30 个器件的统计结果表明,在 ±10 和 ±5 V VG扫描范围内器件成品率分别为 100% 和 93%。我们的成果归功于 CVD 生长的高质量 2H- 和 1T′-MoTe2无缝共面异相结构以及无需转移过程的简便制备技术。我们的工作为 TMDCs 在大规模集成电路中的应用奠定了基础。

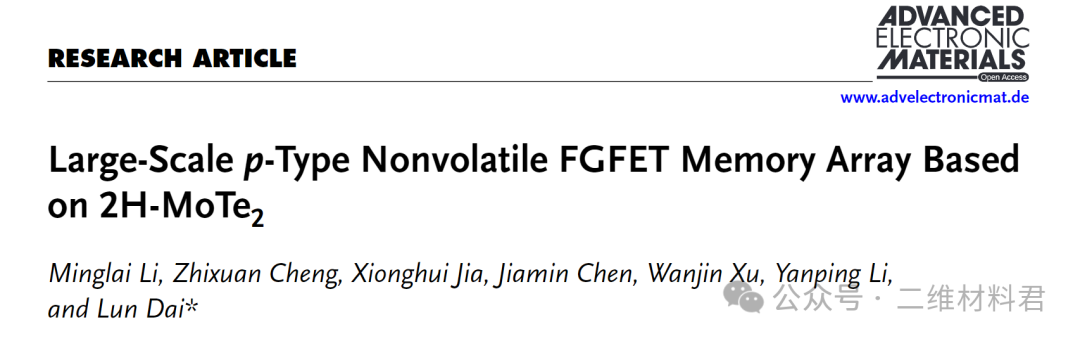

图1 a) MoTe2 FGFET 存储器设备的 3D 和 b) 侧视示意图。FG,浮栅。c-f) 在制造过程中拍摄的光学图像。c) 共面 2H-MoTe2 /1T′-MoTe2图案。d) 隔离的 1T′-2H-1T′ MoTe2阵列。e) 带浮栅的 1T′-2H-1T′ MoTe2阵列。f) 大规模 2H-MoTe2 FGFET 存储器阵列。

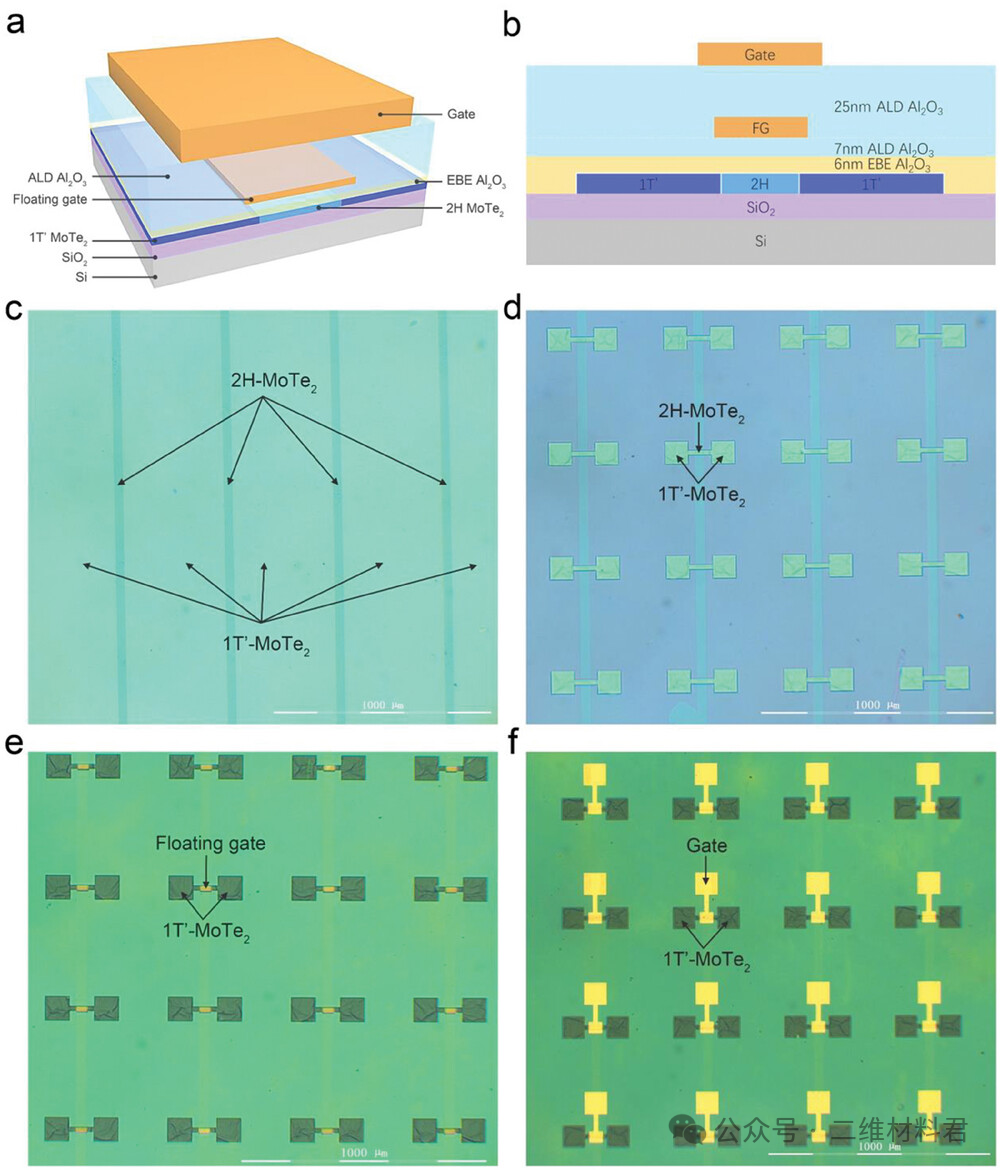

图2 a)无金属浮栅的控制器件的栅极传输特性(I DS – V G曲线)。V DS = 1 V。箭头表示扫描方向。该器件表现出典型的p型 FET 特性。阈值电压滞后仅 ≈1 V,这表明氧化层内和氧化层/半导体界面处的电荷影响很小。b) V DS = 1 V时 FGFET 的栅极传输特性( I DS – V G曲线)。记忆窗口(Δ V th)估计为 ≈11.5 V。c)不同V G扫描范围下的正移和负移阈值电压( V th)。±3、±5、±7 和 ±10 V 扫描范围内的记忆窗口分别约为 ≈0.4、2.8、6.2 和 11.5 V。d)在各种栅极电压脉冲之后,在V G = 0 V下测量 FGFET 的I DS – V DS曲线。脉冲宽度为 1 s。线性行为表示 2H-MoTe2沟道与 1T′-MoTe