随着电子产品小型化、数字化、高频化和多功能化等的快速发展与进步,作为电子产品中电气的互连件—PCB中的导线的作用,已不仅只是电流流通与否的问题,而且是作为“传输线”的作用。

也就是说,对于高频信号或高速数字信号的传输用的PCB之电气测试,不仅要测试线路的“通”、“断”、“短路”等是否合乎要求,而且还要其“特性阻抗值”是否合乎要求,只有这两方面都“合格”了,PCB才符合允收性。

1、信号传输线的提出

这是为了区别常规导线而提出的名称。按IPC-2141的3.4.4条的定义:“当信号在PCB导线中传输时,若导线的长度接近信号波长的1/7,此时的导线便成为信号传输线”了。有的文献认为,导线的长度接近波长的1/10时,应按信号传输线处理。显然,后者更严格(显得‘过分’),但大多数人认定为前者。

大家知道,电流通过导体时,会受到一个“阻力”,在直流电中是电阻,符合欧姆定律。

即: R=V/I

在交流电中的“阻力”是由“电阻”、“感抗”和“容抗”的综合结果,

即: Z=〔R2+(XL-XC)2〕1/2

元件有很高频率信号传输,但经过导线传输后,频率下降(时间延迟)了,导线越长,时间延长越厉害,当导线的长度接近于波长时,或信号速度(频率)提高到某一范围时,传输的信号便会出现明显的“失真”。

⑴高频信号的传输

假设:(一)元件的信号传输频率f=10MHZ,导线L=50cm,则

C=f*λ

λ= C/f

λ/L= C/f*L=60

属于常规导线。

元件的信号传输频率f=1GHZ,导线的长度L=10cm

则 λ/L= C/f*L=3

不属于常规导线,应进行特性阻抗值控制的传输线。

⑵脉冲信号的传输。

在数字电路中从“0”到“1”的上升时间tr是很短的.但可用下面公式来计算频率fmax:

fmax=0.35/tr

假设:元件的上升时间tr是=2ns,

则 fmax=0.35/tr=175 MHZ L= C/ fmax*7=24.5 cm

当导线长度≥24.5 cm时,应作为信号传输线处理。

目前:TTL(transister-transister logic)的tr为4ns→1ns→0.5ns→

ECL(emitter-coupled logic) 的tr为3ns→1ns→0.5ns→

⑶信号传输线必须进行特性阻抗值控制。

如果不进行特性阻抗值控制时,在线路中产生的信号“反射”,会“抵消”正在传输信号。λ/L比率越小,“反射”越严重,则会产生如下问题:

①信号(或能量)传输效率明显下降;

②由于反复干扰(抵消)信号传输,将随着频率增加而严重化;

③部分“能量”是会以电磁波辐射出去,在内部导线或网络之间形成EMI。

信号普通线与信号传输线的差别主要有三个方面:

⑴信号普通线是指第一信号传输被接受完成后,才发送第二个信号,因此第一个信号传输过程中的“反射”信号,不会抵消第二个信号。而信号传输线的特征是第一个信号传输还没有被接受,就发送第二个信号,因此第一信号传输过程中产生的“反射”信号就可抵消第二个信号而削弱了第二个信号,频率越快的传输信号,则“失真”就越多,甚至信号消失。

⑵信号普通线,由于信号传输速度慢,“反射”信号不会抵消后面传输的信号。因此,导线的粗细、缺陷(缺口、针孔)等是允许某些程度存在着。而在信号传输线中,这些粗细、缺陷等要进行十分严格的要求。

⑶信号普通线,不要求特性阻抗值控制,只要求“通”、“断”、“短路”的电气测试。而信号传输线要求特性阻抗值控制,即除了要求“通”、“断”、“短路”的电气测试外,还必须有特性阻抗值控制的测试。

2、PCB中特性阻抗值Z0的设计

主要有两种:微带线和带状线及其派生的各种各样的结构,如何选用,应视元件和电子产品而定。

微带线(适合Z0较大的场合)。

Z0 ={87/(εr+1.41)1/2 }ln{5.98H/(0.8W+T)}

带状线(适合Z0较小的场合)。

Z0 =60ln{4D/[0.67π(0.8W+T) ]}

公式中的D为介质量层厚度。

根据信号传输线的不同位置可以形成各种各样的结构及其计算方法(参见《现代印制电路基础》一书第十四章)。

⑴选用合适的基板(CCL)材料和PCB结构,确定信号传输线的长度等以确定PCB尺寸。

⑵合理的布局与布线,使每组(网络)导线的特性阻抗值Z0与元(组)件的特性阻抗值相匹配。

⑶应考虑基板材料品质的不稳定波动、PCB制造过程的偏差与控制和PCB设计的因素等带来在PCB中特性阻抗值Z0偏差的补救与修正的措施和办法。

3、信号传输线的布设

根据信号“传输线”的定义,信号线布设得很短,使其长度小于1/7传输信号波长,便可消除传输信号被“反射”信号而削弱问题。或者说,信号线布设,其长度短到小于1/7传输信号波长,则其布设的导线便可按普通线处理。

如何使信号线布设得更短呢!除了高频的元件合理布设外,应在PCB板上的互连结构上下工夫,如采用埋/盲孔、盘内孔(hole in pad)、叠孔和HDI/BUM等结构来缩短走线。

介质层越厚,电磁交叉感应越强,串扰越严重!

介质层要薄,必须选择低εr材料。

密集的平行走线将带来更大的电感与电容,从而产生更大的串扰,也是产生杂音的

原因之一。应采用:

⑴相邻的导线层之间互为直角布设;

⑵同一层上采用阶梯式斜向(45度)布设;

⑶通过导通孔的绞线布设。

采用差分传输线可以明显减小传输线的干扰,这在高频和高速数字的信号传输中非常重要。

⑴差分传输线可以明显减小传输线中信号的干扰,提高传输信号的完整性,这是PCB设计者所熟悉的。但是,不同差分传输线减小干扰信号的程度是不同的。为了减小对传输信号的“共模”干扰,采用的差分传输线,主要应做到如下四个 :

(一)形状和长度相同,做到“共模”拐角,即不要使形状和长度不相同而引起“共模”干扰;

(二)由直角改为45度角,实验表明,其“共模”干扰可降低50%;

(三)采用补偿 电容,如在 拐角的短线加一个合适的电容,可降低干扰;

(四)形成双绞方式差分传输线。

⑵双绞差分传输线。采用通孔在不同层之间来形成双绞差分传输线是目前最有效地降低干扰信号的方法。

①有偏位(移)双绞差分传输线。又可称为常规双绞差分传输线。

②没有偏位(移)双绞差分传输线。可获得较好的降低信号干扰。

4、特性阻抗值Z0对基板(CCL)材料的要求

从Z0 ={87/(εr+1.41)1/2 }ln{5.98H/(0.8W+T)}公式中可以看出:影响特性阻抗值Z0的主要因素:

(一)介电常数εr;

(二)介质层厚度H;

(三)信号传输线的宽度W;

(四)信号传输线的厚度。这些表明:特性阻抗值Z0与基板材料是息息相关着。实验也表明,影响特性阻抗值Z0从大到小是9(二)、(三)、(一)、(四)顺序排列的。

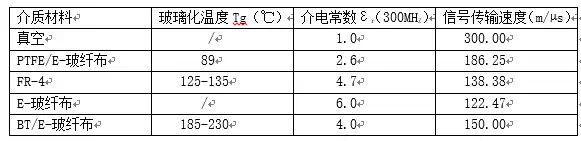

⑴介电常数εr影响着信号的传输速度。

信号的传输速度是随着介电常数εr的增加而下降。根据电磁波理论中的马克斯威尔公式,即: Vs=c/(εr)1/2

表1

⑵介电常数εr的大小是复合材料的“加权和”。这就是说,介电常数εr的大小是与介质层的组成、结构(复合组成与结构)有关。

如FR-4材料中,由于采用E-玻纤布的结构(如7628、2116、1080、106等)不同,其树脂含量是不同的,因此,其介电常数εr值是不一样的。对于严格控制特性阻抗值Z0来说,PCB设计和制造都应该了解和加以计算,才能获得更精准的控制与结果。

⑶εr值变动的大小比其它因素影响大,位居第三位。介电常数εr对特性阻抗值Z0的影响可以从Z0的公式中看出来:

Z0 ={87/(εr+1.41)1/2 }ln{5.98H/(0.8W+T)}

显然,介电常数εr值越小,Z0值越大,εr值变动的大小影响大,应加以认真控制。

⑴从Z0的公式中可看出,Z0的值是与介质厚度H的自然对数成正比的。

⑵在相同的厚度下,微带线有较大的Z0值。

⑶厚度偏差对Z0值的影响是处于第一位的,因此必须很好控制介质层的厚度。但由于厚度偏差主要是由CCL制造商,其次是PCB制造者(多层压板)来控制的,一般偏差可控制在较小的范围内。

⑴从Z0的公式中可看出,Z0的值是随着导线厚度T的减少而增加着。

⑵在相同的厚度下,微带线有较大的Z0值。

⑶厚度偏差对Z0值的影响是最小的。

⑴从Z0的公式中可看出,Z0的值是随着导线宽度W的下降而增加。

①计算与实验表明,导线宽度W对特性阻抗值Z0的影响是最大的。

②导线宽度W是PCB生产最难控制的,也是最需要进行控制的。

⑵导线宽度偏差控制的意义。

导线宽度偏差控制的意义,在某种程度上是控制了PCB(OEM设计)的特性阻抗值Z0的范围。因为选定CCL材料和完成PCB设计之后,这意味着:

①介电常数εr值、介质厚度H值和导线厚度T值等基本不变,或变动不大;

②导线宽度偏差最大,也最难控制,因为制造过程长、影响多。

③导线较长又是用来传输信号的,导线宽度偏差是影响特性阻抗值Z0的最大因素。

所以,导线宽度偏差值的控制是当今HDI/BUM板的关键技术。

⑶导线宽度偏差的控制。

①导线宽度尺寸的迅速缩小,其控制越难,属于“精细”节距的控制。

②常规的图形转移技术越来越不能满足精细导线的要求了。

③激光直接成像技术是目前最好的制造精细导线的选择。

5、特性阻抗值Z0的测试

特性阻抗的测试样板可按IEC 61188-1-2规定进行。IPC-D-275(四种电路板传输线),IPC-D-317(高速电路板设计规范中传输线的种类)和IPC-TM-650等也作了规定。

目前是以英国Polar公司生产的特性阻抗测试仪。它是由时域反射计(TDR)、台式计算机和特制的附有1米长电缆测试探头以及待测的样板(或互连板)等组成。

特性阻抗的测试原理是由时域反射计(TDR)向印制板发射出一个信号电压(高频信号或高速脉冲信号的电压),测量出反射回来的电压变化,然后通过PC计算并输出特性阻抗值Z0来。

计算公式:Z0 =Z参V线/(V参-V线)