8月开播的明星真人秀节目中国版《极速前进》第四季,在国庆期间划上句号。乒坛名将张继科与其父张传铭组成的父子档较早被淘汰,但张继科的一句玩笑话于我颇有启发。

在我印象中,张继科不止一次说他爹“有偶像包袱”。这当然是开玩笑,都知道张继科本人才是偶像。不过,玩笑中也有道理:我们这些五十多岁的人,做事确实容易有思想包袱,怕犯错,放不开。

反映到写作上,就是力求把事情说清楚,成文总是写不短。读者要看,保不齐还得先做一番心理建设。

不妨适度放下包袱,不求严谨,有话就说。譬如,探讨些小道消息,或者抒发一两点感悟,总之是想到哪儿就写到哪儿,没有很明确的目标。为了与其他文章区分开来,这类文章标题全部以“狒”(废)字开头,取不太正式之意,姑且称之为“狒系列”。关注“企事录”公众号的朋友们想必已经看到,9月份就有3篇“狒系列”的文章发布,也分别挂在今天推送的三、四、五条上,供大家参考。

迟来的解释之后,让我们回过头看看国庆长假。在此期间,IT业界吸引较多人关注的一件事是英特尔前CEO欧德宁(Paul Otellini)去世,引发一众怀念。今天所要讨论的主题,由欧德宁辞世消息传出前一天Intel宣布推出基于Arria 10 GX FPGA的可编程加速卡(Programmable Acceleration Card,PAC)展开。

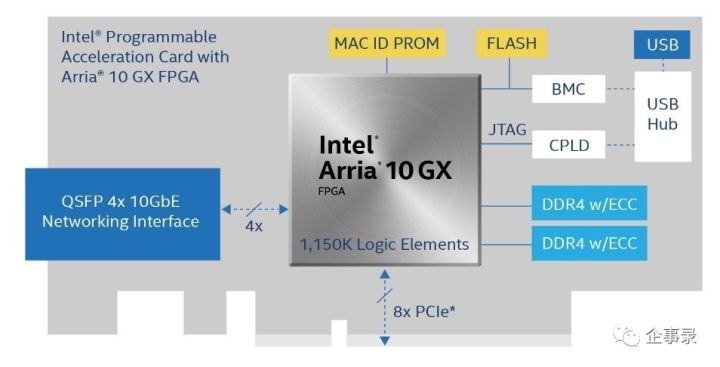

PAC看起来是PCIe x16的接口

很重要的一点,这款FPGA就是英特尔原计划与Skylake版至强CPU封装在一起(MCP,多芯片封装)、共用一个Socket P(LGA3647)插座的型号。在2015年斥资167亿美元收购Altera之后不久,Intel就开始着手这项工作。如今,代号Skylake的初代至强可扩展处理器(Xeon SP)及Arria 10 GX的独立插卡版本已先后推出,Xeon+FPGA的片上集成版本——也就是我在《

至强SP简析:FPGA及Fabric版本揭密

》一文中解析的至强“P”版本,却还没有确切的消息。

实际电气上为PCIe x8,还有一个4x 10GbE(万兆以太网)接口

我曾经在公开和私下场合多次说过“Intel是最不像半导体公司的半导体公司”,而Altera可以说仍是典型的半导体公司,这里面很重要的一个区别是对解决方案(Solution)和最终用户的态度不同。尽管随着ABC——按火爆顺序先后可能是CBA,即云计算、大数据、人工智能(AI)——的兴起,传统的半导体公司也越来越重视完整的解决方案和直接教育最终用户。个人感觉,近年来nVIDIA在这方面做得也不错。

在解决方案和教育市场方面,不能不提 IDF,即 Intel Developer Forum。去年8月在旧金山召开的2016年秋季 IDF 上,第三天留给所谓的 ISDF,即 Intel SoC FPGA Developer Forum,是Altera演变而来的PSG(Programmable Solutions Group,可编程解决方案事业部)的舞台。因为只有春季IDF才在中国举行,所以英特尔之后还单独把ISDF在北京办了一站。

到了2017年,欧德宁的接班人科再奇,在把春季IDF搬到深圳没取得预期效果之后,干脆把IDF整个取消了!这样一来,至少就我个人而言,接受Intel FPGA再教育的机会,只剩下IFTD,即Intel FPGA Technology Day(英特尔FPGA技术大会)。

IFTD 2017北京站的举办日期,恰与“英特尔精尖制造日”撞车。于是,只能上午听完英特尔的10nm及其他先进制程(如22FFL),从东三环赶到北三环,赶场IFTD。这样一来,完美错过IFTD上半场讲解Stratix 10和Arria 10 FPGA&SoC的部分。

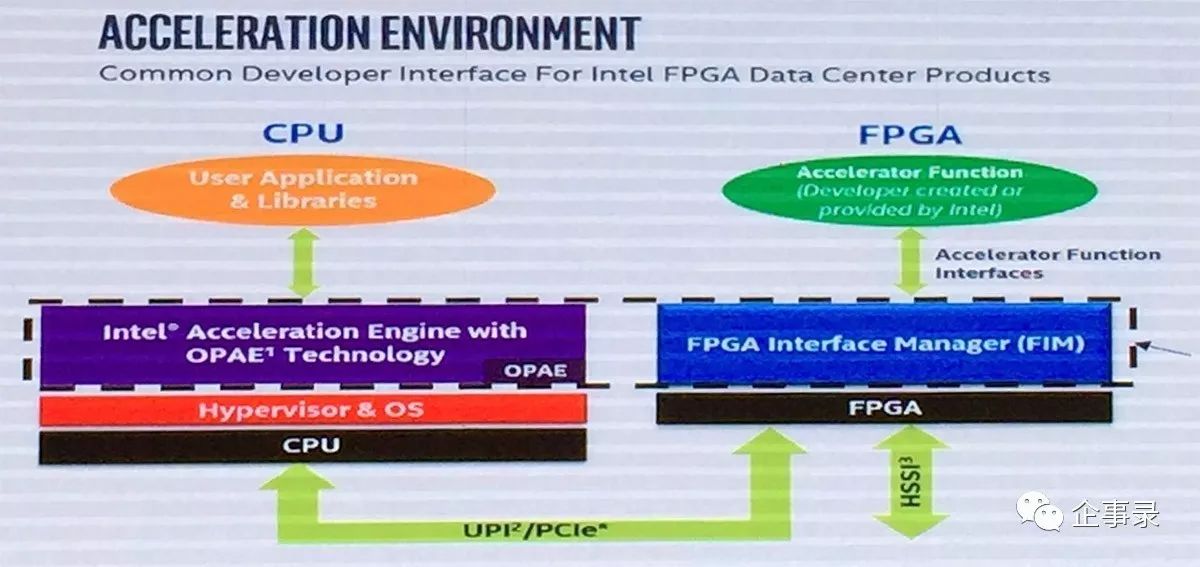

注意下方CPU与FPGA互连的UPI/PCIe选项

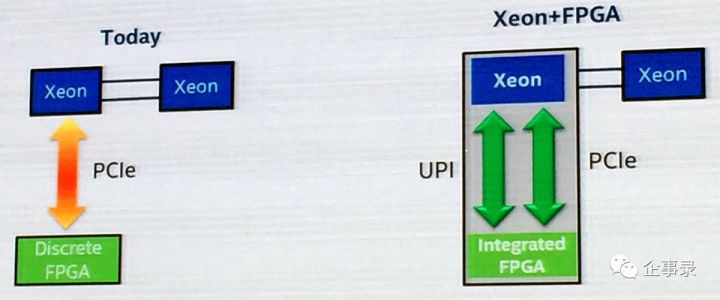

好在,下午的议程中,还是出现了(Xeon)CPU与FPGA通过UPI(Intel Ultra Path Interconnect)或常规的PCIe这两种互连选项,看起来片上集成的计划并没有取消。

左为常规的PCIe互连,右为通过UPI的片上互连:从早先的规划来看,Arria 10 GX 1150与Skylake之间有1组9.6GT/s的UPI,速率略低于Skylake之间互连所能达到的10.4GT/s;还有2个PCIe 3.0 x8,供FPGA对外提供HSSI(High Speed Serial Interface,高速串行接口)以连接其他设备,如高速以太网