现在每一个闪存厂家都在向3D NAND技术发展。3D NAND技术的好处不言而喻,它能够提供比现有2D闪存更大的存储空间,存储密度可以达到现有闪存的3倍以上,未来甚至可以作出10TB以上的2.5英寸SSD出来。另外它还有一个重要的特性,就是(每单位容量)成本比现有技术更低,而且因为无需再通过提升制程工艺、缩小存储单元来增加容量密度,可靠性和性能会更好。

2017年上半年处理器、主板多不景气,唯有NAND、DRAM等存储芯片市场继续高涨。有分析师表示2017年DRAM内存涨价将达到39%,NAND闪存涨价也有21%,市场价值大涨60%到70%,厂商的运营利润也维持在40-60%的高位。两相对比之下,可以看出DRAM内存涨幅高于NAND闪存,这主要是因为上游厂商产能更偏向NAND闪存,导致DRAM供应减少。也正因为此,NAND闪存涨幅略低,产能也在增大。根据预测,2017年Q4季度之后3D NAND产能转换基本完成,将逐步化解供应短缺的问题。2017年NAND出货量将增长36%,明年则增长45%,均价会有所下滑(19%),不过厂商的盈利并不会受到影响,因为智能手机、SSD市场具有很大的价格弹性,而先进工艺也会使得制造成本大幅下降。

预计2018年是NAND、DRAM涨价的一个分水岭,特别是NAND闪存,三星、美光、东芝、西数、Intel等厂商在2017年将完成3D NAND闪存转换,今年内3D NAND就要超过2D NAND成为主流,而今年量产的主力是64层及以上的3D NAND,它被视为3D闪存的“甜点”(Sweet point)。

但是,和任何一项技术创新一样,3D NAND的研发之路注定是不平坦的。在大量资金投入博弈的背后,还有研发人员辛勤的汗水。最近《Semiconductor Engineering》的执行编辑Mark LaPedus写了一篇文章,题目是《NAND Market Hits Speed Bump》,分析了从平面到 3D NAND 的过渡,为什么比预期的更加困难和费时。为了方便阅读,《智慧产品圈》以作者的口气,带领大家认识和了解在3D NAND研发和量产的背后所遭遇的各种困难和挑战。

由于系统数据的猛增,NAND闪存的需求依然强劲,但整体的NAND闪存市场充满了挑战,陷入了一个产品短缺,诸多供应链问题和技术转型困难重重的不平顺周期。

英特尔,美光,三星,SK海力士以及东芝/西部数据等厂商仍在市场上销售传统的平面NAND,但这个技术在目前的1xnm节点下将很快达到物理极限。所以这些供应商在销售传统平面产品的同时,一直在致力于开发一种称之为3D NAND的新一代存储技术,它可以被广泛地应用于智能手机和固态存储驱动器(SSD)。

预计3D NAND技术将在年底成为主流,比预期的大约晚了两到三年。事实证明,3D NAND比以前想象的更难制造。与2D结构的平面NAND不同,3D NAND类似于一座垂直的摩天大楼,其中水平层被堆叠起来,然后使用微小的垂直通道进行连接。

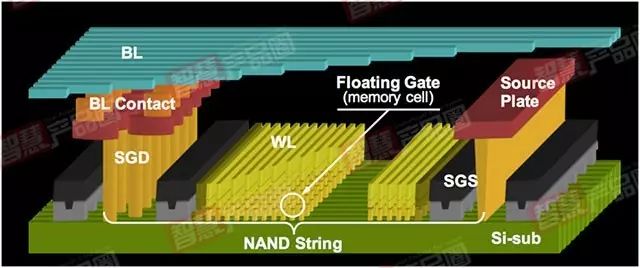

▲ Fig. 1 2D NAND 结构(来源:西部数据)

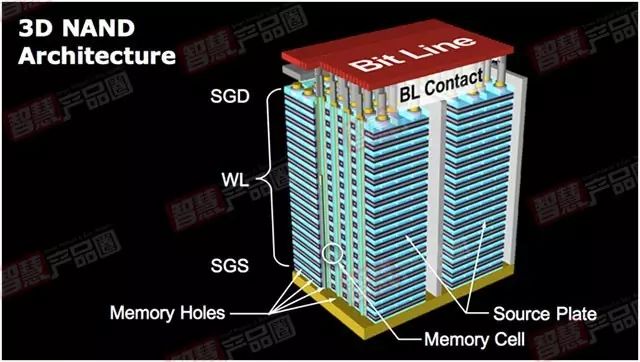

▲ Fig. 2 3D NAND结构(来源:西部数据)

▲ Fig. 2 3D NAND结构(来源:西部数据)

尽管如此,NAND闪存的供应商持续将其产能的很大一部分比例从平面转移到3D NAND。但这个转移似乎需要更长时间,一些供应商3D NAND产品的生产跟不上市场的需求,有些厂家甚至连发货都成问题。

自从2016年7月开始,平面和3D NAND闪存产品已经供不应求,这种状况延续至今。供应商们原计划2017年整个NAND市场可实现40%的增长,事实上,根据Objectiv Analysisi研调机构的预计,2017年需实现45%的增长才能满足目前的市场需求。

“供货短缺已经变得越来越厉害,” Objectiv Analysisi的分析师Jim Handy说,“每家供应商都在瞄着40%的增长目标,他们计划通过扩充新的产能并将这些产能全部用来生产3D NAND产品。但从平面向3D NAND的转换并没有像预期那样顺利,因此,生产环节的增长没能跟上需求的增长。”

虽然NAND的价格相对平稳,但供应链问题并没有彻底解决。“我们预计这个短缺会一直延续到2018年中期,”Handy说。“我们关注的是,作为一个具有成本优势的产品,我们还需要多久才能解决3D NAND的量产问题。在正式量产之前,我们预计短缺会进一步增长,因为需求在增长,生产却赶不上需求的增长。”

另外,现在的NAND市场还存在不少问题,归结起来主要有以下几个方面:

来自市场上的并不都是坏消息,2017年预计将是3D NAND 的一个重要年份。应用材料公司硅系统部的存储材料部总经理Er-Xuan Ping表示:“到今年年底,3D NAND的位元出货量预计将超过2D NAND。“

根据应用材料的统计,一年以前,全球3D NAND的晶圆每月开工量达到了35万到40万片(wspm)。据该公司称,截至年底,该数字将会达到50万至70万片(wspm)之间。

此外,从平面到3D NAND 的转换正在引发资本支出的激增。根据Pacific Crest Securities统计, 总体上闪存部分的资本支出预计将在2017年达到236亿美元,比2016年上涨24%。据该公司称,总的半导体资本支出预计将达到766亿美元,比2016年上涨18%。

Lam Research的全球产品部首席技术官Yang Ping说:“我们在3D NAND中继续保持强劲势头,它是半导体制造设备的最大驱动力。”

近年来,平面NAND在闪存驱动器,智能手机和固态硬盘等数据存储应用中经历了巨大的发展。但由于多方面原因,供应商正在从平面转换为3D NAND。

经过多年的努力,供应商现在已将NAND单元从120nm缩小到1xnm节点,集成度提高了上百倍。然而,在1xm处问题开始显现。 Handy表示:“作为控制门的浮栅门其耦合电容出现了不希望的减少。”

可以说平面NAND已是强弩之末,3D NAND的晶圆较平面工艺有成本优势。根据Objective Analysis的数据,平面工艺的300mm的晶圆成本为1200美元,每片晶圆的容量分别为5.6TB,换算为每千兆字节(GB)的成本是0.21美元。在3D NAND中,晶圆成本为2,000美元,每片晶圆的容量为17.2兆字节,转化为每千兆字节(GB)的成本为0.12美元。

最重要的是,3D NAND在系统中有较大优势。Applied的Ping说,“数据需求在大大增加,3D NAND在速度和可靠性方面远优于2D NAND。”

数据中心的主要驱动力在于,基于3D NAND的SSD正在取代传统的硬盘驱动器(HDD)。通常,SSD比HDD更昂贵,但是SSD消耗的功率更少,并且减少了空间。根据Forward Insights的说法,NAND闪存从2D到3D技术的转变使得企业级SSD的容量已经超过企业级硬盘,“推出QLC(每单元四位)技术有望推动SSD产能更高。”

然而,3D NAND也在面临一些新的技术竞争,一种被称为3D XPoint的ReRAM技术据称比NAND速度还要快。

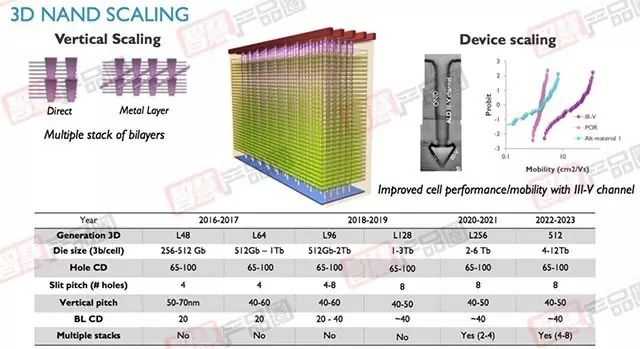

3D NAND将成为一个巨大的市场。三星的NAND闪存在2013年问世,那是三星发布的全球首款3D NAND器件。今天我们已经看到, 32层和48层器件已在市场大量出货,而64层和72层芯片刚开始起量,96层和128层产品还处于研发状态。

“我们将不断拓展业内第一代V-NAND生产的极限,使业界更加接近太比特V-NAND时代的到来。”三星电子Flash产品和技术团队执行副总裁Kye Hyun Kyung表示:“我们正在开发的下一代V-NAND产品与全球IT行业同步,以便能够为最新推出的新系统和服务做出贡献,为消费者带来更高的满意度。”

▲ Fig. 4: 3D NAND flash roadmap. Source: Imec

在平面NAND中,存储单元是水平方式相互联结的。然而,在3D NAND中,联接线被折叠并垂直起来,单元是以垂直方式堆叠的。在多晶硅层之上的横排的走线是结构中的字线,位线的走线是垂直于字线的。

垂直堆叠可以有几个平面或是多层的。随着层级的增加,存储器位密度也随着增加,但也意味着制造难度增加。Forward Insights的分析师Greg Wong表示:“一般来说,由于资本支出强度增加和收益率下滑,64- / 72-层的变化一直是有挑战性的。……收益正在慢慢改善,他们会越做越好?大家都这么说,但我不认为它是令人信服的。”

随着业界朝向超越64-/72-层的器件发展,挑战越来越高。然而位密度并不一定在同一条曲线上。“层数增加越来越具有挑战性,3D NAND产品的真正成熟至少还要有四到五代的提升空间。” Wong表示:“从二维到三维NAND,我们可以从每晶圆比特数上有一个飞跃,但是从3D NAND产品到下一代3D芯片这个数字不会增加太多。如果我们只依靠3D到3D的NAND转换,还不足以满足这些需求,未来的需要在产能上将会超过2018年。

在晶圆厂,3D NAND和平面NAND的制程是有差别的。在2D NAND中,制造过程依赖于使用光刻等比例缩放存储器单元的尺寸。

光刻技术仍然用于3D NAND,但不再是关键的一步。对于3D NAND来说,挑战从光刻转移到淀积和蚀刻技术。

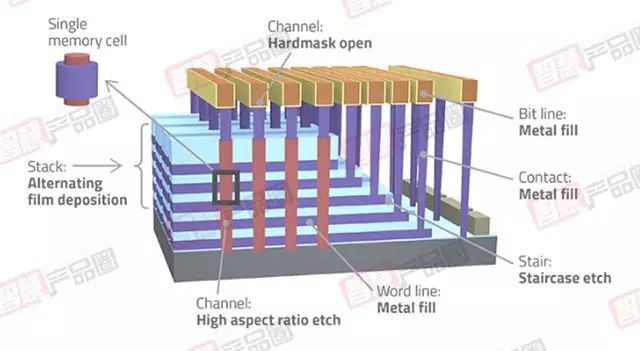

▲ Fig. 5: Key process steps in 3D NAND. Source: Lam Research

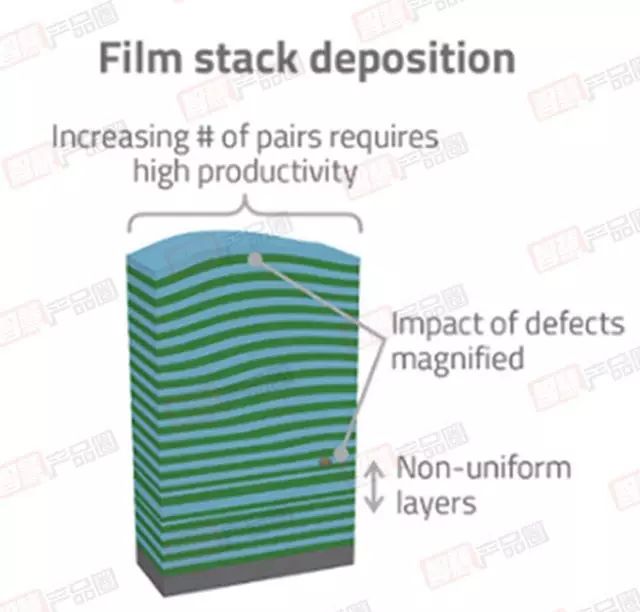

3D NAND工艺从衬底开始,遇到的第一个挑战是堆叠层的淀积。用化学气相沉积(CVD)方法,在衬底上逐层淀积和堆叠薄膜。这个制成就像制作一层蛋糕。首先,在衬底上沉积一层材料,然后在顶部再另外淀积一层。该制成反复多次,直到完成器件所需要的层数为止。每个制造商使用不同的材料来创建堆叠层。例如,三星在衬底上沉积氮化硅和二氧化硅。

在理论上,制造商可以堆叠无限数量的层。但是随着层数的增加,怎样保证这些层的厚度精确性和均匀性是一个挑战,况且它必须在一个高产量下完成。这里最大的挑战是张力和缺陷控制。 Lam的Pan说,“在整个3D NAND制造过程中,需要仔细控制薄膜沉积过程中产生的张力。随着层数的增加,这尤其重要。”

▲ Fig. 6: Film stack deposition challenges. Source: Lam Research.

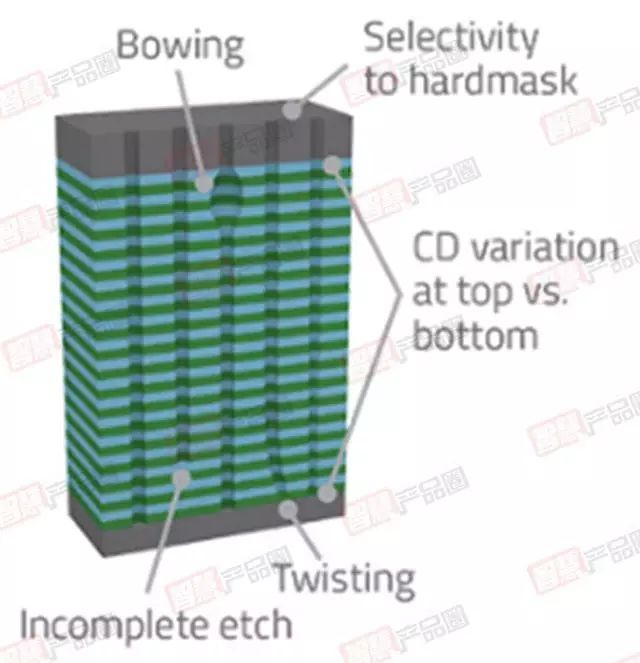

在堆叠层沉积工艺之后,将碳基掩模版施加在膜堆上,并且在顶部上形成孔图案。接着做的是一步最难的工艺:高深宽比(HAR)蚀刻。

对于3D NAND,蚀刻工具必须从器件堆叠的顶部向底部衬底钻出微小的圆形孔或通道,32层和48层器件的深宽比为40:1,64层为60:1。为了描述这一工艺的复杂性,我们以三星的器件举例,三星的3D NAND器件在同一芯片中有250万个微小通道。每个通道必须平行和均匀。每个通道的深度是3微米或大于3微米。

在这个工艺中,用离子刻蚀的方法来刻蚀孔。但是随着蚀刻工艺深入到通道中,离子的数量可能会减少,这反过来降低了蚀刻速率。更糟的是,可能会发生不希望的CD迁移现象。

“高深宽比沟道孔洞的制程仍然是最关键和最具挑战性的工艺模块。” Lam’s Pan表示,“HAR蚀刻过程中,在选择性剖面和CD值之间要做到最好的平衡,仍需要持续的工艺和产品创新。”

▲ Fig. 7: Channel etch challenges. Source: Lam Research.

今天,HAR蚀刻和其他设备能够开发64层3D NAND器件。但对于下一代96层和128层器件以及更高层数的器件,情况可能会有所不同。“96层很可能是一个临界点,”应用材料的Ping说,“目前的介电蚀刻机可能面临96层的挑战,挑战来自掩模版。”

在96和128层,HAR蚀刻机必须能够蚀刻更深结构里的微小孔,深度大约在6微米左右。如果不是现行的掩模版影响的话,今天的蚀刻机也可以做到60:1这个复杂的HAR蚀刻。问题在哪里?Ping说:“现在困难来自掩膜版。掩模版与介电蚀刻机相互作用。就像有一个掩膜在顶部,机器就会失去一些能量和力量。”

简单地说,今天的HAR蚀刻设备和掩模版材料可能会在96层或128层时碰到问题。在这一点上,行业面临着一些艰难的选择。制造商可以在这两条路径里选择其一,一是等比例缩小3D NAND单个字符串,二是字符串堆叠。