随着半导体发展脚步接近未来的14埃米,工程师们可能得开始在相同的芯片上混合FinFET和奈米线或穿隧FET或自旋波电晶体,他们还必须尝试更多类型的存储器;另一方面,14埃米节点也暗示着原子极限不远了…

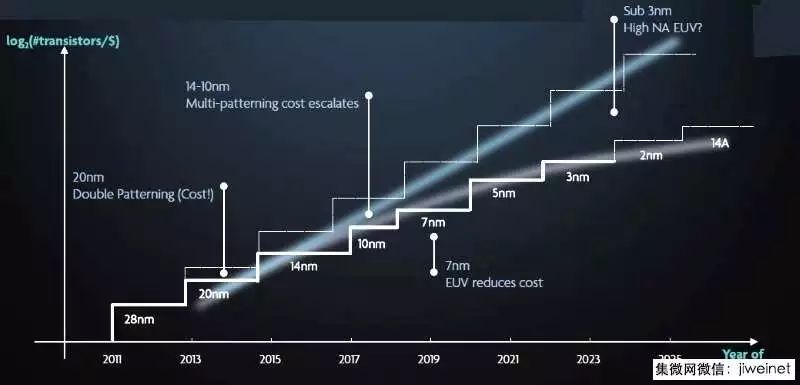

在今年的Imec技术论坛(ITF2017)上,Imec半导体技术与系统执行副总裁An Steegen展示最新的半导体开发蓝图,预计在2025年后将出现新制程节点——14埃米(14A;14-angstrom)。这一制程相当于从2025年的2nm再微缩0.7倍;此外,新的占位符号出现,显示制程技术专家乐观看待半导体进展的热情不减。

Steegen指出:“我们仍试图克服种种困难,但如何实现的途径或许已经和以前所做的全然不同了。”

14埃米节点也暗示着原子极限不远了。单个砷原子(半导体所使用的较大元素之一)大约为1.2埃。

随着半导体发展脚步接近未来的14埃米,工程师们可能得开始在相同的芯片上混合鳍式场效电晶体(FinFET)和奈米线或穿隧FET或自旋波电晶体。他们将会开始尝试更多类型的存储器,而且还可能为新型的非冯·诺依曼电脑(non-Von Neumann)提供芯片。

短期来看,Steegen认为业界将在7nm采用极紫外光(EUV)微影技术、FinFET则发生在5nm甚至3nm节点,而奈米线电晶体也将在此过程中出现。

如今,14埃米节点还只是出现在简报上的一个希望 (来源:Imec)

Steegen表示:“从事硬体开发工作的人员越来越有信心,相信EUV将在2020年初准备好投入商用化。经过这么多年的努力,这一切看来正稳定地发展中。”

Imec是率先安装原型EUV系统的公司,至今仍在鲁汶(Leuven)附近大学校园旁的研究实验室中持续该系统的开发。

Steegen预计,EUV“将在最关键的层级导入制程,”以便在线路终端处完成通道和区块。使用今天的浸润式步进器,这项任务必须通过3或4次的步骤,但透过EUV更精密的解析度,只需一次即可完成。

工程师在这些先进节点上工作时,必须先检查其设计能够搭配使用浸润式或EUV系统。当他们在将芯片发挥到极致时,将会使用EUV更进一步缩小其设计。

无论如何,还需要3或甚至4次的浸润式图案化过程,才能打造具有小于40nm间距的特征尺寸。工程师不要指望设计规则能很快地变得更简单。

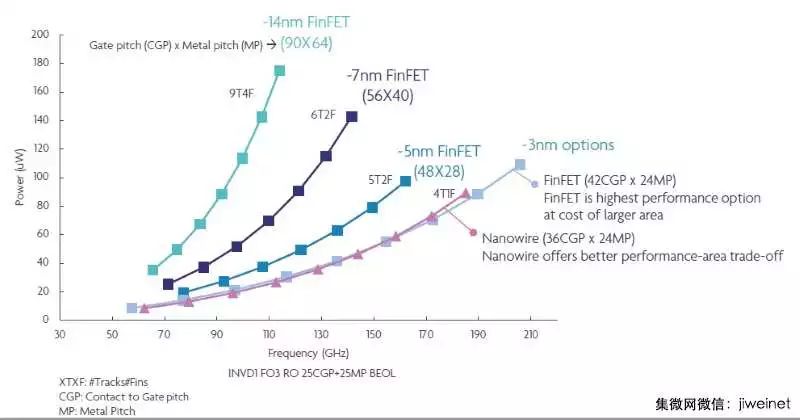

Imec勾勒未来节点可能实现的功率性能

选择抗蚀剂与电晶体

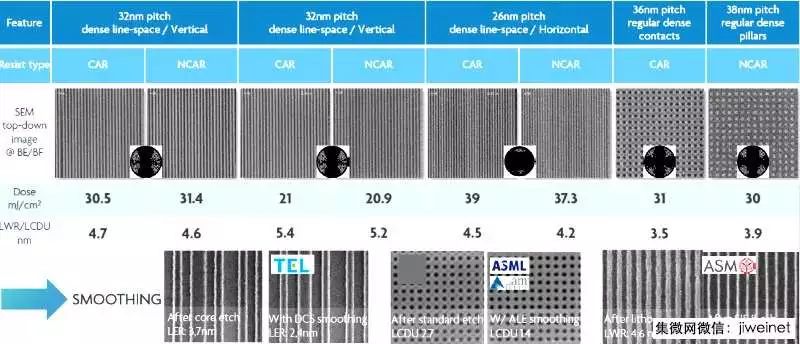

找到合适的抗蚀剂材料是让EUV顺利量产的几项挑战之一。到目前为止,如果研究人员能以20毫焦耳/平方公分的曝光能量进行,就能使EUV顺利进展。

包括ASML、东京电子(Tokyo Electron)和ASM等几家公司正在开发专有(意味着昂贵)的技术来解决问题。它们通常涉及了抗蚀剂处理以及多个制程步骤,才能蚀刻或退火掉粗糙度。

“这项技术看起来非常有希望,所以我们有信心能够克服线边粗糙度(LER)的问题,”Steegen说。

此外,Imec现正开发保护EUV晶圆免于污染的防尘薄膜。它以碳奈米管提供承受EUV曝光超过200W以上所需的强度,而非阻挡大部份光源穿透晶圆。

除了EUV以外,下一个重大障碍是基本电晶体的设计转变——任何元件核心的电子开关。Steegen说:“FinFET的微缩是必须解决的关键问题。”

截至目前为止,研究显示,FinFET可以在5nm时使用,而如果导入EUV的情况顺利,甚至可沿用至3nm节点。Steegen说:“在3nm节点,FinFET和奈米线的效果能几乎一样好,但奈米线闸极间距带来了更多的微缩,”他并展示一项堆叠8根奈米线的研究。

详细观察阻抗剂的问题显示,使用化学助剂和不使用化学助剂(CAR和NCAR)的研究结果。LWR/LCDU是指线边粗糙度的测量值应不超过特征间距尺寸的十分之一,图中的范围约为3.2至2.6。

通道微缩与存储器

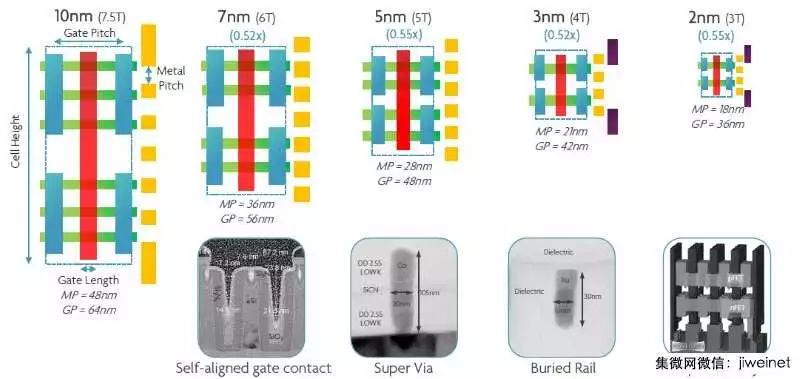

如果EUV一再延迟,芯片制造商将会调整单元库来缩小芯片。Imec正致力于开发一个3轨(3-track)的单元库,这是将芯片制造商目前用于10nm先进制程的7-track单元库缩小了0.52倍。

其折衷之处在于它能实现3nm节点,但仅为每单元1个FinFET保留空间,较目前每单元3个FinFET减少了。此外,随着单元轨缩小,除了从7nm节点开始的挑战,预计工程师还将面对新的设计限制。

Imec正致力于开发几种得以减轻这些困难的设计,包括所谓的超级通道(super-vias),连接3层(而2层)金属以及深埋于设计中的电源轨,以节省空间。

这项工作显示,设计人员可能被迫在3nm时移至奈米线电晶体,实现完全以浸润式步进器为基础的制程。然而,透过EUV,3nm制程仍可能有足够的空间实现5-track的单元库,因而使用基于FinFET的元件。

仅使用浸润式步进器的制程可缩小单元轨,但却会随着闸极(红色)缩小而牺牲FinFET(绿色)数量。而在底部,Imec展示研究人员正开发的4个结构,用于减缓微缩。

无论如何,到了这些更先进的节点时,系统、芯片和制程工程师都必须比以往更加密切地合作。他们必须确定哪些功能可以被整合于单一芯片上,或者是否需要单独的芯片制作,如果是这样的话,那么这些芯片又该如何进行链接等等。

同时,还有一大堆新的存储器架构仍处于实验室阶段。Steegen说,磁阻式随机存取存储器(MRAM)目前是最有前景的替代技术,可用于取代SRAM快取,甚至是DRAM。然而,MRAM到了5nm以后可能还需要新电晶体结构。

此外,还有其他更多有趣的选择,包括自旋轨道转矩MRAM以及铁电RAM,可用于取代DRAM。业界目前正专注于至少5种备选的储存级存储器技术,主要是交错式(crossbar)和电阻式RAM结构的存储器。

此外,Imec正开发新版OxRAM,将有助于物联网(IoT)的设计。目前已经针对可承受汽车设计所需温度条件的方法进行测试了。

面对诸多极其乏味的选择与严苛挑战,Steegen依然乐观。在开始对1,800位与会者发表演讲之前,她还快速地进行了一项调查,结果显示有68%的人认为半导体产业将顺利过渡到3nm节点。

她说:“谢谢所有对这个可能性回答『是』的人,而对于那些认为『不』的人,我会证明你错了。”