引言

在半导体封装行业,先进封装正扮演着越来越重要的角色。作为一种对14纳米/7纳米先进工艺节点的互补,先进封装有着比摩尔定律的等比例缩小(scaling)更实惠、成本更低、性能更优的特点,现在,大多数高性能芯片提供商更乐意选择先进封装来提升芯片性能。先进封装符合高端芯片向尺寸更小、性能更高、功耗更低演进的趋势,因此在封装行业,越来越多的外包封装/测试厂商(OSAT)开始研发先进封装技术。

一、先进封装以及在路线图中的定位

根据国际半导体技术发展线路图的预测,未来半导体技术发展将集中在三个方向:

一是继续遵循摩尔定律等比例缩小的原则,继续提升电路性能、减小尺寸、降低功耗。二是向多类型方向发展,拓展摩尔定律。三是向系统级芯片(SoC)和系统级封装(SiP)发展,构建高价值集成系统。

在后两个发展方向中,都强调了先进封装的重要性,使得先进封装技术的研发成为持续推进半导体产品性能提升和功耗降低的关键因素,也使把不同工艺节点及工艺技术的各类IC 集成到一个 SoC 或 SiP 上成为可能,这也是现阶段和今后相当一段时间内的最佳解决方案。

现有的先进封装技术,比较常见的是晶圆级封装(WLP)、2.5D 和 3D 集成等。晶圆级封装又分为“扇入”(fan-in)和“扇出”(fan-out)两种类型。

二、先进封装对设计流程的挑战

先进封装作为一个方向,已经开始对半导体的设计流程带来影响。首先,这些新技术能够对整体设计做分区,就像一种具有芯片外部特征的互连,这与芯片的内部特征非常相似。先进封装使我们有了集成不同技术(工艺)的能力,例如对存储、射频或电源部分分别进行优化后集成,但同时也为传统的设计工具带来了相关挑战。

西门子业务部Mentor Calibre工程副总裁胡安·雷伊指出,“我们面临的第一个挑战是,先进封装具有非常大的、异构的特性,必须意识到这一点。我们已经修改了我们的传统工具来处理多种新技术。这些新技术也需要物理验证,例如设计规则检查(DRC)、版图和线路图对照检查(LVS)等。在先进封装里,我们必须通过一个中介层或某种类型的互连技术做连接。在这种情况下,它会影响系统的互连特性,以及这些特性如何相互影响。它还影响可制造性特征的设计。所以在现有工具和流程中有些内容需要修改,以便我们可以方便地完成这个任务。”

Marvell也是使用传统的设计软件来做封装设计。因为先进封装的一大特点是可以将不同种类的芯片和封装一起放在基板上。

先进封装带来了设计复杂性的显著增加,需要描述从芯片到基板、从中介层到基板、基板到电路板、基板到测试板的所有互连。这在传统的封装行业来看变得非常难以控制,目前有许多要靠手工集成,夹杂一些零碎的检查,因此开发一个基于传统商用工具的自动化设计流程已经成为了EDA行业的目标,这对于减少封装设计错误和手动设计的风险很有必要。

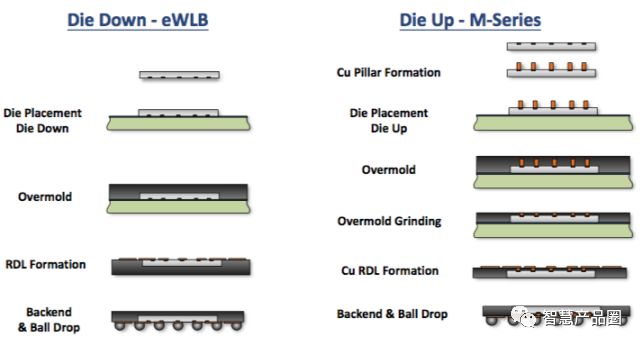

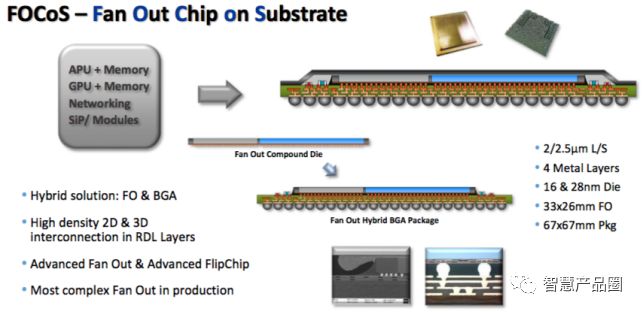

ASE工程高级总监亨特说,“ASE第一个投产的扇出是为英飞凌生产的eWLB(嵌入式晶圆水平球网格阵列),这是一个低密度的产品。它可以按照我们设计晶圆级CSPs(chip-scale package)的方式来设计。但到了2016年,我们推出了FoCoS(基板上的芯片扇出),这是一种中介层解决方案的替代方案。随着密度的发展,我们那些不擅长这种技术的设计师已经能够设计复杂的封装了。布线暂时还必须手动进行。但ASE一直在与供应商合作,尽可能多地实现自动化设计。”

▲ 不同的扇出方式,包括上芯片方法中的铜柱形成物

(来源:ASE)

现在传统的设计工具已经扩展到可以支持先进封装,在这方面已经有相当多的研究与开发活动来探索许多替代方案,并期望附带必要的工具。例如,热区域的相互作用,热效应对路径和电迁移的影响等等。还有一些令人兴奋的进展是从半导体制造领域的传统PDK(工艺设计套件)技术转移到ADK(装配设计套件)类型的例子。这也许是先进封装标准化工艺的开始。

三、今天谁在使用先进封装?

先进封装的驱动力主要来自于人工智能,5G以及电信和数据交换设备。是由高性能驱动的,至少对于一级大客户是如此。他们需要最大的带宽,除了先进节点之外,先进封装满足了他们的性能要求。

eSilicon在16/14纳米节点时代就开始做先进封装。他们有一个基于台积电技术的7纳米工艺平台。eSilicon的先进封装为那些不愿意或不能够采用7纳米的客户所采用,他们通过先进封装对系统进行分区以获得成本和性能的最佳平衡。封装集成化让他们实现了一个更好的解决方案,而不是单一自动地走上老路,即按照摩尔定律的等比例缩小原则将所有东西都塞进硅里,事实上这在成本和性能方面没有任何意义。

先进封装的另一个市场是服务器市场,它主要体现的是异构集成。客户可在两个技术节点之间来分区选取不同的芯片。虽然市场也在开发同质集成,即在同一个节点上分区相同的芯片。但这不仅仅是对硅的分区,它还采用了不同的技术。ASE工程高级总监亨特说,“对于SiP应用,我们有更复杂的扇出结构,在那里客户要求集成过滤器并将被动元件项直接放到扇出结构里。所有这些与中介层解决方案的复杂性不同,但比我们过去使用的更复杂。”

另外在移动性和高性能计算方面,人们对汽车行业以及机器学习类应用和人工智能的兴趣正在增长。这个对先进封装的推动在未来也是不可估量的。因为对汽车电子来说,硅的特征小尺寸并不是主要的。

Marvell封装工程总监刘成林说,“我们更看好高带宽存储市场,因为7纳米工艺太昂贵了。如果只寄希望于硅,芯片的掩膜尺寸会太大了。到时候你别无选择,只能为应用不断调整芯片大小。”

四、与ASIC和FPGA相比,先进封装的

成本是多少?

ASE目前有一个可代替中介层的扇出解决方案,可以做到低于2微米的线宽和间距。这个方案有四个布线层(RDL),一个凸点下金属化层(UBM)加一个铜柱,六层金属布线,良率可以做到98.5%,成本明显低于中介层的解决方案。

是否可以一直缩小线宽和间距呢?亨特认为,“如果缩到1微米以下的线宽和间距,现在还不是一个最佳的解决方案。不过,扇出在电性能和热效能上比中介层解决方案要好的多。我们的RDL比中介层上的走线更厚,通孔也更大,并且没有那么深。所以使用扇出可以得到更好的电性能。”

扇出的另一个好处是可以使封装做的更薄,例如中介层约为100微米厚度,扇出只有25微米。但从成本上看先进封装的价格还是太高了。

▲ 基板上芯片扇出 (来源:ASE)

选择先进封装的客户往往是注意特别选择了小的芯片,而不是在光罩极限上制做一个大规模的ASIC芯片。这更多的也是从成本考虑。eSilicon封装制造高级总监埃里克·托萨亚说,“我们有一个客户,本来可以有两个版本选择,一种是单芯片BGA,另一个是高性能版本集成两个相同的ASIC在一个较大基板中的中介层上,没有HBM。最后他们发现,与两个单一的BGA相比,集成双ASIC方案是一个性价比高的解决方案。这说明这种封装是非常有价值的。”

五、怎样降低先进封装的成本