文章介绍了使用化学气相沉积生长的单层WS2场效应晶体管(FET)的n型金属-氧化物-半导体(nMOS)反相器,展示了其出色的电学性能,包括高开/关比、小亚阈值摆幅和出色的漏极诱导势垒降低。通过优化掺杂工艺和采用HfO2不对称双栅结构,实现了亚阈值工作的单层WS2 nMOS反相器,并在低电源电压下实现了超高增益和低功耗。这些发现突出了单层WS2作为高增益和超低功耗逻辑应用的候选者。

通过化学气相沉积生长的单层WS2 FET,并通过优化掺杂工艺和采用HfO2不对称双栅结构,实现了亚阈值工作的nMOS反相器。

单层WS2 FET具有出色的电学性能,包括高开/关比、小亚阈值摆幅和出色的漏极诱导势垒降低,这有助于实现高增益和低功耗的nMOS反相器。

在电源电压为1V时,实现了超高增益和低功耗的nMOS反相器,这是通过亚阈值工作的晶体管实现的,这有助于逻辑电路在低电压和低功耗条件下工作。

单层WS2不仅适用于nMOS反相器,还可以用于构建包括NAND、AND、NOR、OR和SRAM在内的逻辑电路,展示了其作为高性能逻辑应用的潜力。

单层WS2作为高增益和超低功耗逻辑应用的候选者,其未来的应用前景值得进一步探索和研究。

为了方便各位同学交流学习,解决讨论问题,我们建立了一些微信群,作为互助交流的平台。

2.告知:姓名-课题组-研究方向,由编辑审核后邀请至对应交流群(生长,物性,器件);

欢迎投稿欢迎课题组投递中文宣传稿,免费宣传成果,发布招聘广告,具体联系人:13162018291(微信同号)

研究背景

在过去的几年里,人们进行了大量的研究工作,重点是在金属-氧化物-半导体场效应晶体管(MOSFETs)中使用2D过渡金属硫族化合物(TMDs)作为沟道材料。由于2D TMDs的原子薄厚度可以有效地抑制短沟道效应,因此2D TMDs在超缩放MOSFETs中具有取代Si的巨大潜力。在2D TMDs家族中,MoS

2

和WS

2

已被研究用于高性能n沟道MOSFETs(nMOSFETs),而单层WSe

2

已显示出作为p沟道MOSFETs(pMOSFETs)的前景。晶圆级生长的2D TMDs n/p MOSFETs的进步可以使高性能CMOS器件和系统具有增强的可扩展性和可制造性。2D TMDs也被广泛用于低功耗应用。在当今的移动时代,对低功耗电子器件的需求不断增加。由于2D TMDs具有优异的抗短沟道效应能力和相当大带隙带来的极低关断电流,因此可以为低电压和低功耗电路提供良好的平台。从低功耗的角度来看,在关断状态附近深亚阈值区工作的晶体管可用于实现在低电源电压(V

DD

)下工作的逻辑电路。

成果介绍

有鉴于此,近日,

韩国延世大学Jiwon Chang,梨花女子大学Joon Young Kwak和光云大学Tae-Jun Ha(共同通讯作者)等合作报道了一种使用化学气相沉积(CVD)生长的单层WS

2

场效应晶体管(FET)的n型金属-氧化物-半导体(nMOS)反相器

。本文大面积CVD生长的单层WS

2

FET具有出色的电学性能,包括高开/关比,小亚阈值摆幅和出色的漏极诱导势垒降低。这是通过使用AlO

X

/Al

2

O

3

的

n型掺杂和高k介电HfO

2

双栅结构实现的。由于优越的亚阈值特性,单层WS

2

FET在亚阈值范围内表现出高跨导和高输出电阻,与传统的Si MOSFETs相比,具有显著更高的本征增益。因此,本文成功实现了亚阈值工作的单层WS

2

nMOS反相器,在电源电压(V

DD

)为1 V和2 V时分别具有564和2056的超高增益,并且在V

DD

=1 V时功耗低至~2.3 pW·μm

-1

。此外,单层WS

2

nMOS反相器进一步扩展到逻辑电路的演示,如AND,OR,NAND,NOR逻辑门和SRAM。这些发现表明单层WS

2

在高增益和低功耗逻辑电路中的潜力,并验证了其在大面积内的实际应用。文章以“

Realization of Extremely High-Gain and LowPower in nMOS Inverter Based on Monolayer WS

2

Transistor Operating in Subthreshold Regime

”为题发表在著名期刊

ACS Nano

上。

图文导读

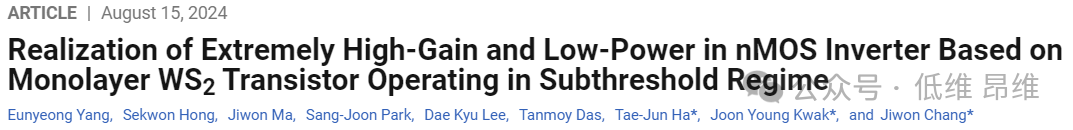

图1. AlO

x

/Al

2

O

3

掺杂WS

2

FET的器件结构、制备工艺及材料表征。(a)单层WS

2

FET的器件结构示意图及制作工艺。(b)具有1.5 nm Al种子层和17 nm Al

2

O

3

的SG WS

2

FET的横截面TEM和EDS图。(c)原始单层WS

2

和含有1.5 nm Al种子层和17 nm Al

2

O

3

的单层WS

2

的拉曼光谱分析。(d)具有1.5、2和3 nm Al种子层的单层WS

2

的拉曼峰移。(e)原始单层WS

2

和具有1.5 nm Al种子层和17 nm Al

2

O

3

的单层WS

2

的PL光谱。(f)具有1.5、2和3nm Al种子层的单层WS

2

带隙。

图1a显示了单层WS

2

FET的器件结构示意图和制造工艺。本文主要研究了两种类型的器件:Al

2

O

3

单栅(SG)和HfO

2

双栅(DG)器件。Al

2

O

3

SG器件具有一个背栅电极,采用20 nm Al

2

O

3

的背栅电介质。而HfO

2

DG器件具有顶栅和背栅电极,背栅电介质为14 nm HfO

2

,顶栅电介质由AlO

X

和Al

2

O

3

组成。如图1a所示,本文首先分别使用不同的背栅电介质Al

2

O

3

和HfO

2

制备了典型的背栅单层WS

2

FET。然后,利用电子束蒸发器(EBE)将Al种子层沉积在单层WS

2

上,暴露在空气中数小时使其完全氧化,然后原子层沉积Al

2

O

3

,诱导n型掺杂。仅对于HfO

2

DG器件,在AlO

X

/Al

2

O

3

的顶部形成顶栅电极,实现不对称DG结构。图1b显示了Al

2

O

3

SG器件的TEM和EDS图像。从TEM图像来看,20 nm Al

2

O

3

背栅电介质上的单层WS

2

被~4 nm的AlO

x

(氧化的Al 1.5 nm种子层)和17 nm的Al

2

O

3

覆盖。在EDS图像中,可以清晰地观察到单层WS

2

中的W和S。为了检验Al种子层和Al

2

O

3

对单层WS

2

的影响,本文制备了不同厚度Al种子层和Al

2

O

3

沉积在单层WS

2

上的样品。Al种子层沉积后,将样品暴露在空气中进行充分氧化。然后进行AFM、拉曼光谱和光致发光(PL)测量。从图1c的拉曼光谱中,E

2g

和A

1g

峰分别在354.0和421.3 cm

-1

处证实了原始单层WS

2

。Al种子层和Al

2

O

3

沉积后,由于面外振动模式的软化,A

1g

峰红移,表明电子浓度更高。先前的研究报道了金属氧化物薄膜ALD沉积过程中两种氧空位的形成:中性空位(V

O

)和二价正电荷空位(V

O

2+

)。在这两个空位中,V

O

2+

诱导电子,在WS

2

、MoS

2

和WSe

2

等2D TMDs中产生n型掺杂效应。因此,AlO

X

和Al

2

O

3

中的V

O

2+

在单层WS

2

中导致n型掺杂。在图1d中绘制了不同厚度Al种子层和Al

2

O

3

下A

1g

峰的负位移量。总的来说,Al种子层和Al

2

O

3

越厚,负位移越多,n型掺杂量越高,但超过7.7 nm Al

2

O

3

时负位移量趋于饱和。图1e和f中PL的负移表明由于Al种子层和Al

2

O

3

沉积的n型掺杂导致带隙减小。在拉曼分析中也可以发现,随着Al种子层和Al

2

O

3

厚度增加,n型掺杂更加明显。由于n型掺杂是由AlO

X

和Al

2

O

3

中的V

O

2+

引起的,并且在较厚的AlO

X

和Al

2

O

3

中产生了更多的V

O

2+

,因此可以预期较厚的Al种子层和Al

2

O

3

中有较高的n型掺杂水平,这与拉曼和PL分析一致。然而,在典型2D TMDs上进行电荷转移掺杂时,有报道称可能会出现两种状态:“陷阱态”和“掺杂态”。陷阱态是指在2D TMDs和氧化物之间的界面处俘获电荷,可能导致SS退化。另一方面,掺杂态在2D TMDs中诱导电荷,而不是在界面处俘获它们,从而避免了SS退化等问题。

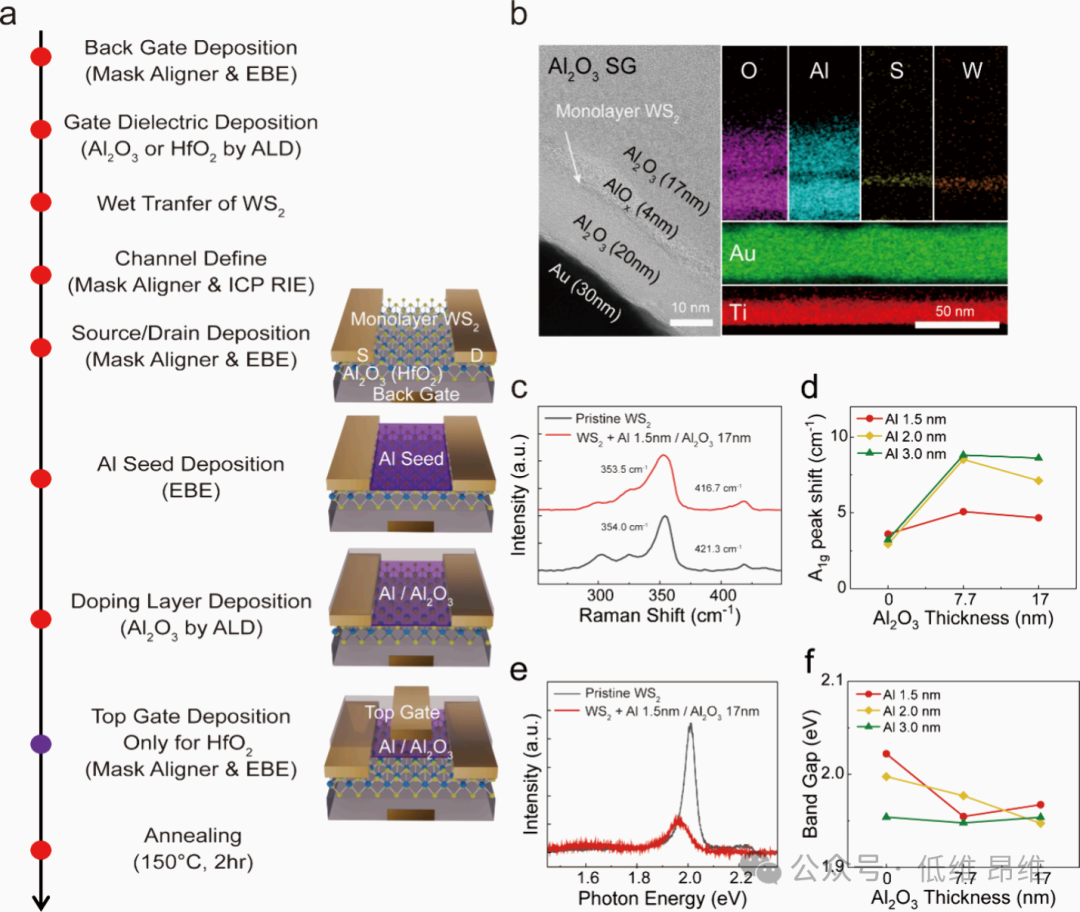

图2. 不同AlO

x

/Al

2

O

3

掺杂条件下单层WS

2

FET的电学性能。(a)具有不同Al

2

O

3

厚度的Al

2

O

3

SG器件在V

GS

=V

TH

+5 V的I

ON

、log(I

ON

/I

OFF

)、SS和V

TH

的统计分布。(b)具有不同Al

种子层

厚度的Al

2

O

3

SG器件在V

GS

=V

TH

+5 V的I

ON

、log(I

ON

/I

OFF

)、SS和V

TH

的统计分布。(c)HfO

2

DG器件、最佳掺杂Al

2

O

3

SG器件(Al 1.5 nm/Al

2

O

3

17 nm)和无掺杂Al

2

O

3

SG器件的转移特性(I

DS

-V

GS

)。(d)不同V

DS

=0.5、1.0、1.5、2.0 V时,最佳掺杂条件下代表性HfO

2

DG和Al

2

O

3

SG器件的I

DS

-V

GS

。

为了分析WS

2

FET的器件性能,本文使用了Al

2

O

3

SG和HfO

2

DG器件。Al

2

O

3

SG器件主要用于获得最佳掺杂工艺。因此,通过改变单层WS

2

上沉积的Al种子层和Al

2

O

3

的厚度,探索了Al

2

O

3

SG器件的器件性能。在确定了最佳掺杂工艺后,本文引入了HfO

2

背栅电介质和DG结构,实现了比Al

2

O

3

SG器件更好的器件性能。因此,只能通过最佳掺杂工艺制备HfO

2

DG器件。由于背栅电介质Al

2

O

3

和HfO

2

不是直接沉积在单层WS

2

上,而是将单层WS

2

转移到背栅电介质上,因此背栅电介质对掺杂的影响很小。因此,本文仅使用Al

2

O

3

SG器件来检测n型掺杂效应。通过深入研究Al种子层厚度和Al

2

O

3

厚度对器件性能的影响,得到了最佳掺杂工艺。与材料表征一样,Al

2

O

3

SG器件采用不同的Al种子层(1.5、2和3 nm)和Al

2

O

3

厚度(3.5、7.7、12和17 nm)组合制成。由于在HfO

2

DG器件中使用了AlO

X

和Al

2

O

3

作为顶栅介质,因此不考虑厚度大于17 nm的Al

2

O

3

。图2a显示了相同Al种子层厚度为1.5 nm时,不同Al

2

O

3

厚度的导通电流(I

ON

)、导通/关断比(I

ON

/I

OFF

)、SS和阈值电压(V

TH

)统计分布。随着Al

2

O

3

厚度增加,I

ON

开始增加,并从7.7 nm厚度开始在10

-8

−10

-7

A·μm

-1

附近饱和,这与拉曼分析结果一致。值得注意的是,从I

ON

/I

OFF

和SS的分布可以证实,随着Al

2

O

3

厚度增加,性能没有下降。相反,随着Al

2

O

3

厚度增加,I

ON

/I

OFF

和SS得到了改善。此外,随着Al

2

O

3

厚度增加,V

TH

向左偏移,表明n型掺杂效应更强。由于Al

2

O

3

厚度为17 nm时WS

2

FET的性能最佳,因此本文在保持Al

2

O

3

厚度固定在17 nm的情况下改变了Al种子层厚度。如图2b所示,给出了Al种子层厚度为1.5、2和3 nm时I

ON

的分布。无论Al种子层厚度如何,都可以获得相似水平的I

ON

(~10

-7

A·μm

-1

)。然而,随着Al种子层厚度增加,I

ON

/I

OFF

降低,SS显著增加,表明在亚阈值区域性能下降严重。这是由于在Al种子层中诱导了氧成键态。此外,当Al种子层厚度从1.5 nm增加到3 nm时,观察到类似的V

TH

左移,表明了更高的n型掺杂水平。然而,尽管掺杂水平较高,但由于2和3 nm Al种子层对SS、I

OFF

和I

ON

/I

OFF

的退化作用显著,因此1.5 nm是Al种子层的最佳厚度。

图2c给出了在V

DS

为1 V时,采用最佳掺杂工艺(Al 1.5 nm/Al

2

O

3

17 nm)的Al

2

O

3

SG和HfO

2

DG器件的I

DS

-V

GS

特性。本文展示了从相应I

DS

-V

GS

特性中提取的I

ON

/I

OFF

和SS的统计分布。比较掺杂和未掺杂Al

2

O

3

SG器件,通过优化的掺杂工艺,I

ON

提高了近10

5

倍。此外,HfO

2

高k介介质和DG进一步提高了器件的性能。由于改进了对沟道的栅极控制,与Al

2

O

3

SG器件相比,HfO

2

DG器件表现出更低的SS和大约10倍的I

ON

,具有相似的I

OFF

。观察到Al

2

O

3

SG和HfO

2

DG器件的高I

ON

/I

OFF

值分别高达~10

9

和~10

10

。在SS的统计分布中,Al

2

O

3

SG器件的平均SS为~180 mV/dec,而HfO

2

DG器件的SS为~88 mV/dec。两种器件在V

GS

=0 V时显示出相似的I

DS

~10

-11

A·μm

-1

。为了量化HfO

2

DG器件中仅通过14 nm HfO

2

背栅电介质对沟道的栅极控制,本文采用最佳掺杂工艺(Al 1.5 nm/Al

2

O

3

17 nm)制备了HfO

2

SG器件。HfO

2

SG器件性能优于Al

2

O

3

SG器件,具有略高的I

ON

/I

OFF

水平(>10

9

)和明显更好的SS(~120 mV/dec),但仍低于HfO

2

DG器件。在图2d中,绘制了沟道长度为6 μm的代表性Al

2

O

3

SG和HfO

2

DG器件在V

DS

=0.5、1.0、1.5和2.0 V时的I

DS

-V

GS

特性。Al

2

O

3

SG和HfO

2

DG器件的DIBL都很小,分别为0.14和0.08 V/V。与Al

2

O

3

SG器件相比,HfO

2

DG器件的DIBL降低了约40%。通过优化的掺杂工艺,可以实现极低的I

OFF

,优异的SS和正V

TH

,从而实现低功耗。

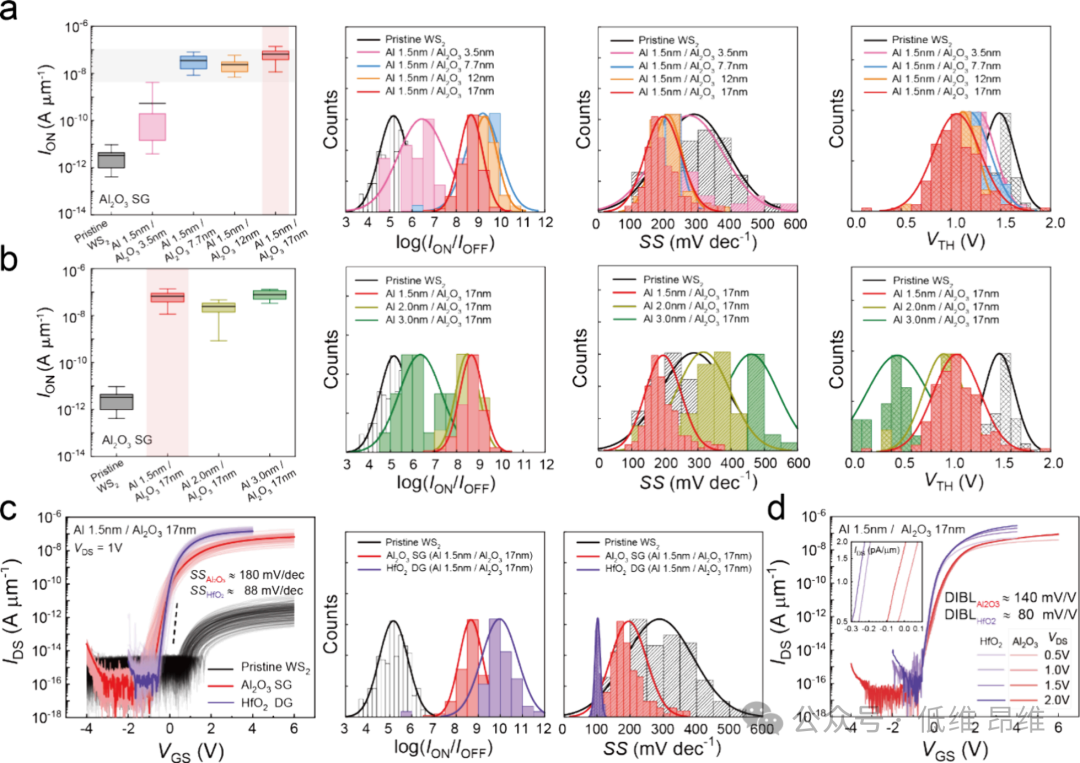

图3. 温度相关的测量。(a)原始WS

2

器件中不同V

GS

的Arrhenius图。(b)最佳掺杂Al

2

O

3

SG器件中不同V

GS

的Arrhenius图。(c)原始WS

2

器件中有效势垒(Φ

Eff

)与V

GS

的关系。(d)最佳掺杂Al

2

O

3

SG器件中Φ

Eff

与V

GS

的关系。(e)在原始WS

2

和Al

2

O

3

SG器件的平带电压(V

FB

)下,单层WS

2

上Ti接触的肖特基结示意图。(f)原始WS

2

和Al

2

O

3

SG器件在V

GS

=V

ON

+3 V时的归一化迁移率。(g)原始WS

2

和Al

2

O

3

SG器件在V

GS

=V

ON

+6 V时的归一化迁移率。(h)原始WS

2

和Al

2

O

3

SG器件的活化能(E

a

)与V

GS

-V

ON

的关系。(i)原始WS

2

和Al

2

O

3

SG器件的界面陷阱密度(D

it

)。

为了更好地理解WS

2

FET中的电荷输运和n型掺杂效应,在Al

2

O

3

SG器件上进行了温度相关的测量。本文分别测量了V

DS

=0.1、0.5和1 V时的转移特性。利用温度相关的2D热离子发射可以提取有效势垒高度(Φ

Eff

)和平带电压(V

FB

)。V

DS

=1.0 V时栅极电压相关的阿伦尼乌斯图如图3a和b所示。Φ

Eff

可在不同V

GS

下确定,分别如图3c和d所示。对于这两种器件,Φ

Eff

在V

FB

以下线性减小,其中热离子发射(TE)是主要的电流机制。在未掺杂的情况下,V

FB

估计为3.8 V,而在最佳掺杂工艺下,V

FB

显著降低至0.5 V。掺杂和未掺杂时在V

GS

=V

FB

处提取的相应有效势垒(Φ

Eff

)分别为~150和~250 meV。掺杂后,2D沟道和金属接触附近的载流子密度增加,从而有效降低Φ

Eff

。从漏极电压相关的阿伦尼乌斯图中,观察到漏极电压与有效势垒高度之间存在微弱的关系。在亚阈值区域,Φ

Eff

与V

GS

呈线性关系。如图3d所示,当V

GS

从-0.8 V变化到0.5 V时,掺杂器件中的Φ

Eff

迅速减小。然而,观察到在未掺杂(原始)器件中Φ

Eff

缓慢下降。因此,使用最佳掺杂工艺(Al 1.5 nm/Al

2

O

3

=17 nm)的器件有望获得高跨导(g

m

)。从图3c和d中可以看出,对于V

FB

以外的V

GS

,Φ

Eff

开始逐渐减小,说明隧穿作用是电流的主要来源。

本文还研究了场效应迁移率对温度的依赖性,以了解器件性能改善的来源。在V

GS

=V

ON

+3和V

ON

+6 V下,分别提取了掺杂和未掺杂Al

2

O

3

SG在不同温度下的迁移率,其中V

ON

为每个Al

2

O

3

SG器件的导通电压,并由T=375 K时的导通电压归一化。V

ON

是在源极和漏极之间开始电荷载流子(电子)积累的V

GS

。与外推法在I

DS

-V

GS

特征的线性区域得到的V

TH

不同,V

ON

是通过搜索I

DS

-V

GS

特征中电流刚刚开始增加的V

GS

来提取的。图3f显示了V

GS

=V

ON

+3 V时的归一化迁移率,观察到无论掺杂与否,迁移率都随着T减小而单调降低,这表明热激活输运在两者中都占主导地位。然而,在图3g的V

GS

=V

ON

+6 V处,掺杂的迁移率随着T减小而增加,这通常在能带输运中观察到。为了进一步研究掺杂对Al

2

O

3

SG中电荷输运的影响,本文分析了活化能。如图3h所示,在掺杂的WS

2

FET中观察到相对较低的E

a

,从而改善了电荷输运。此外,较高V

GS

-V

O

N的E

a

减小意味着费米能级向能带边缘移动。只有当Al

2

O

3

SG掺杂最优时,E

a

才会降低到0 meV以下,这表明主要的输运机制由热激活输运转变为能带输运。基于这些结果,可以推测,在最佳掺杂条件下,Al

2

O

3

SG中器件性能的提高是由于掺杂降低了E

a

和改变了输运机制。此外,本文还研究了掺杂对界面阱密度的影响。如图3i所示,与原始WS

2

(11.9×10

12

cm

-2

·eV

-1

)相比,最佳掺杂Al

2

O

3

SG的D

it

相对较低,为6.7×10

12

cm

-2

·eV

-1

。因此,掺杂有效地抑制了原始WS

2

器件的界面缺陷态,与之前讨论的改进电荷输运特性一致。

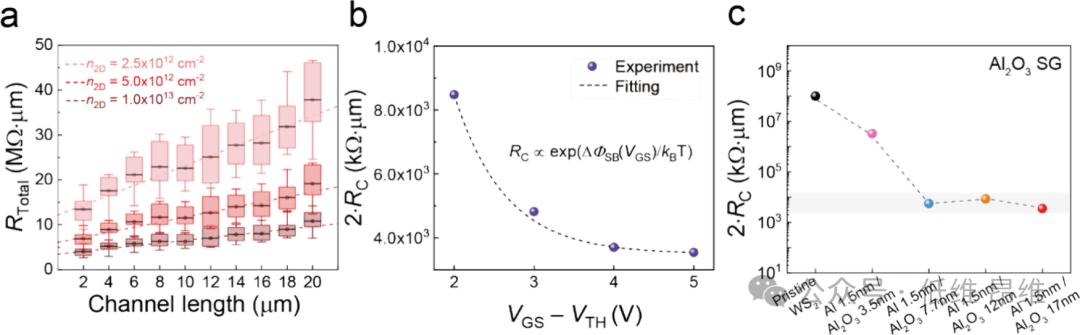

图4. AlO

X

/Al

2

O

3

掺杂的Al

2

O

3

SG器件的接触电阻。(a)总电阻(R

Total

)随2D沟道中载流子密度(n

2D

)的变化。(b)最佳掺杂Al

2

O

3

SG器件的接触电阻(R

C

)随栅极过驱动电压(V

GS

-V

TH

)在2~5 V范围内的变化。(c)不同Al

2

O

3

厚度的Al

2

O

3

SG器件的R

C

。

通过分析掺杂器件中接触电阻(R

C

)对n

2D

和栅极过驱动电压(V

GS

-V

TH

)的依赖关系,证实了隧穿电流的主导作用,如图4a和b所示。在图4a中,采用转移特性(I

DS

-V

GS

)和转移长度法(TLM),在不同n

2D

下从总电阻(R

Total

)中提取R

C

。当n

2D

从2.5×10

12

增加到1×10

13

cm

-2

时,R

C

减小。图4b清楚地显示了V

GS

-V

TH

从2 V到5 V时R

C

的指数下降行为。V

GS

增加导致隧穿势垒厚度减小,从而导致R

C

呈指数下降。此外,本文还研究了R

C

与Al

2

O

3

厚度的关系。图4c显示了通过TLM从R

Total

中提取不同沟道长度的R

C

。由于n型掺杂,R

C

最初随着Al种子层和Al

2

O

3

而降低。然而,当Al

2

O

3

厚度超过7.7 nm时,R

C

开始饱和,并且在7.7、12和17 nm的厚度下R

C

表现相似。最佳掺杂工艺(Al 1.5 nm/Al

2

O

3

17 nm)得到的R

C

(>1 MΩ·μm)可能不像以前报道的各种接触工程那样具有竞争力。然而,在这项工作中,为了在nMOS反相器中实现高增益和低功耗,本文使用在关断状态附近深亚阈值区域工作的晶体管,其中器件性能的特征是SS和DIBL,而不是I

ON

和R

C

。因此,在AlO

X

/Al

2

O

3

n型掺杂所改善的I

ON

、I

ON

/I

OFF

、SS、DIBL和R

C

等器件性能特性中,SS和DIBL是利用深亚阈值操作晶体管实现高增益和低功耗nMOS反相器的关键因素。

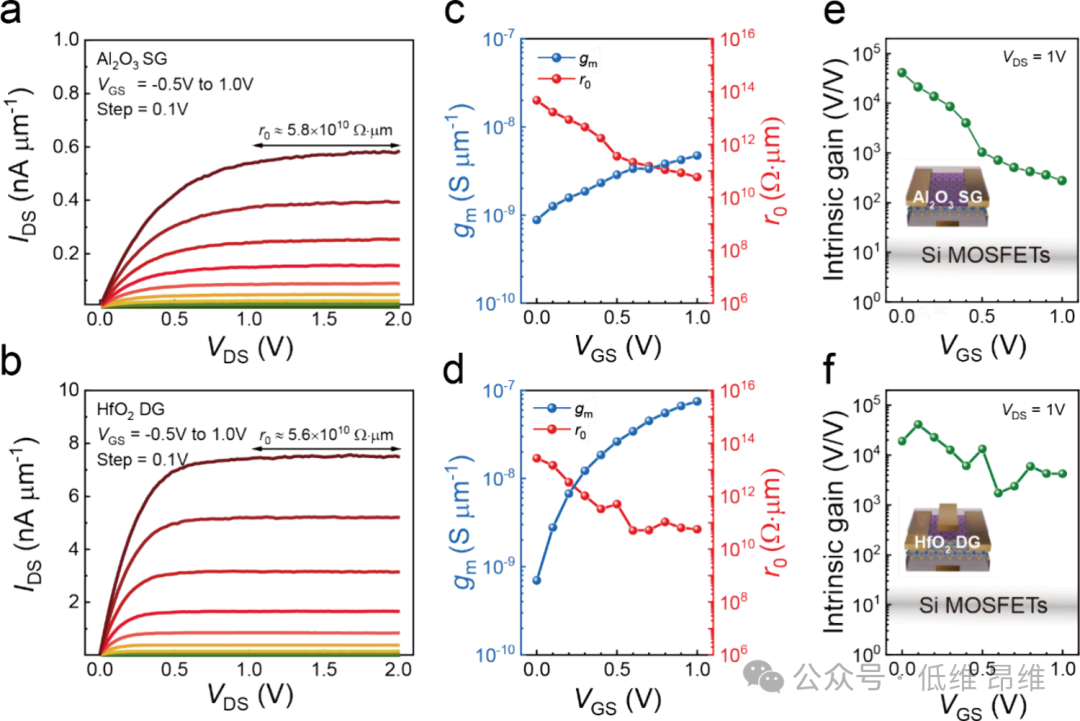

图5. Al

2

O

3

SG和HfO

2

DG器件的输出特性、输出电阻、跨导和本征增益。(a&b)Al

2

O

3

SG和HfO

2

DG器件在不同V

GS

(-0.5~1.0 V)下的输出(I

DS

-V

DS

)特性。(c&d)跨导(g

m

)和输出电阻(r

0

)。(e&f)本征增益。

本文研究了最佳掺杂工艺(Al 1.5 nm/Al

2

O

3

17 nm)下Al

2

O

3

SG和HfO

2

DG器件在亚阈值状态下的应用。首先,在图5中,本文研究了亚阈值工作中V

DS

=1 V时,在小V

GS

范围内(V

GS

=0至1.0 V)的跨导(g

m

)和输出电阻(r