UCLA的电子工程系除了电路领域有Abidi, Razavi和Frank Chang等大咖坐镇外,其实半导体领域也是非常之强,有Kang Wang,Jason Woo等器件大师,也有今天要介绍的超级明星:Subramanian (Subu) Iyer。

早年岁月:Salicide与SiGe HBT

Iyer教授出生于印度,1977年毕业于印度最强的理工科院校——印度理工学院(IIT,被称为印度的MIT,据说很多去美国上MIT的印度学生都是因为IIT没录取才会去美国MIT)。之后,Iyer来到了美国阳光灿烂的加州,并在1981年UCLA电子工程系获得博士学位。所以后来Iyer教授回到UCLA,或许也因为这里有着他年轻时最美好的回忆吧!

在1981年博士毕业后,Iyer加入了IBM的T. J. Watson研究中心。

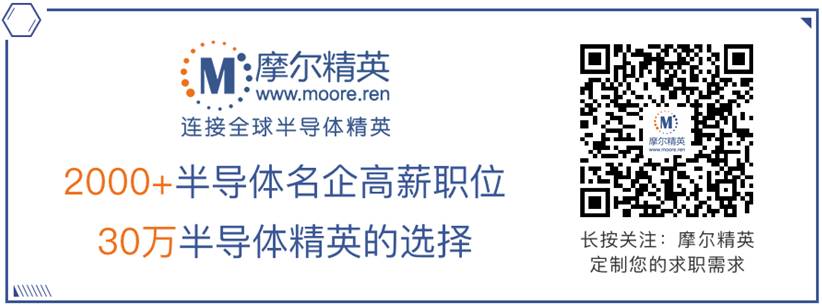

Iyer到了IBM后不久,就对MOSFET工艺做出了非常大的贡献,即Salicide工艺。Salicide是”Self-Aligned Silicide”(自对准硅化物)。Salicide的主要目的是为了减小MOSFET器件中的接触电阻。

其做法是在栅刻蚀及源漏注入以后,以溅射的方式在上面淀积一层金属层,然后进行第一次快速升温煺火处理(RTA),使淀积的金属发生反应,形成金属硅化物。通过设定煺火温度,金属仅仅在想要的区域发生反应,因此是一种自对准的过程。然后再用刻蚀(清除不需要的金属淀积层,留下栅极及其他需要做硅化物的Salicide。

目前,Salicide已经用在几乎所有的MOSFET工艺中,Iyer也因为在Salicide工艺开发中做出的贡献获得了IBM给他颁发的第一个杰出技术贡献奖。

在Salicide之后,Iyer于1985年成立了IBM硅基异质结构项目。当时,异质结以及相关的band engineering研究正是如日中天,Iyer也在这方面做出了杰出的贡献。

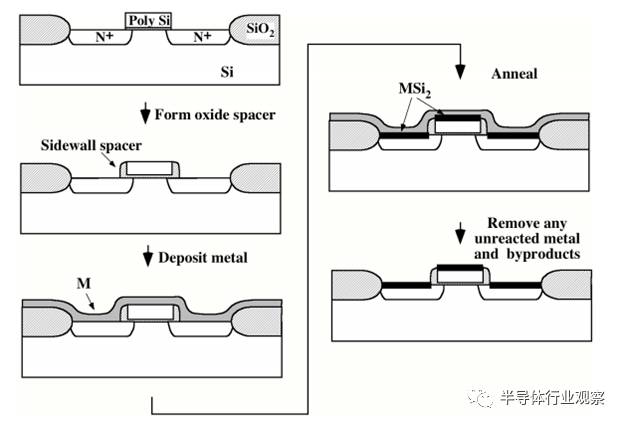

在异质结三极管的异质结构中,中间层有较低的能带,因此电子很容易就由旁边的夹层注入,从而在晶体管中由发射极经过基极到集极的电流可以大大提高,晶体管的放大倍率(beta)也为之增加;同时基极的厚度可以减小,其掺杂浓度可以增加,因而基区渡越时间减小,于是异质结三极管工作速度快,电流增益大,广泛应用于当时的卫星通讯或是移动电话大哥大等设备中。然而,异质结一般使用较贵的半导体材料。

为了解决成本与集成度问题,1987年Iyer第一个成功研制出了使用低价SiGe工艺的异质结三极管。SiGe异质结三极管一开始被用在IBM的高端CPU中,不过由于功耗原因不久就被CMOS取代。之后IBM将SiGe HBT用在了射频系统中,获得了巨大的成功。Iyer因为SiGe异质结三极管而获得了第二个IBM杰出技术贡献奖。

更进一步:eFuse与eDRAM

在Salicide与SiGe HBT后,Iyer在IBM并没有停下前进的脚步。

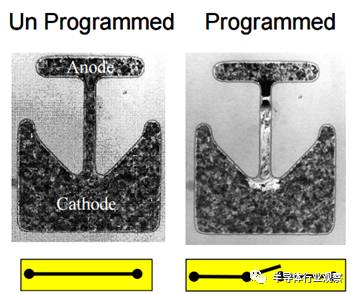

上世纪90年代到本世纪初是计算机相关芯片蓬勃发展的时代。除了依据摩尔定律不断地缩小CMOS特征尺寸以外,还有不少研究者在探索其他的计算机发展方向,例如可重构计算。为了实现实时可重配置,Iyer与他在IBM的同事们在2002年提出了eFUSE,可以通过编程来控制特定导线的通或断。

不过,后来人们发现eFUSE这样的“硬”编程互连线用于可重构计算不如FPGA中的“软”变成互联,所以eFUSE在可重构计算中已经用得不多。然而,eFUSE在今天找到了另一种应用,就是用于保护芯片,阻止用户实施某些操作。例如,用户实施某些非法操作时,eFUSE可以导通使得芯片流过巨大的电流,从而实现芯片自毁功能。微软的XBOX 360中就使用了eFUSE来阻止用户烧入旧版本的firmware。Iyer也由于eFUSE而获得了IBM颁发的第三个杰出技术贡献奖。

在eFUSE之外,Iyer也把目光放到了内存上。在计算机中,DRAM存储密度高,但是访问速度受限,而且由于接口问题处理器访问DRAM的带宽也受限。另一方方面,CPU的片上SRAM访问速度快,带宽大,但是存储密度低,这就导致了很难在CPU上集成很大的存储器。那么,有没有一种既能实现高存储密度,又能集成到CPU上实现高速访问的存储器呢?

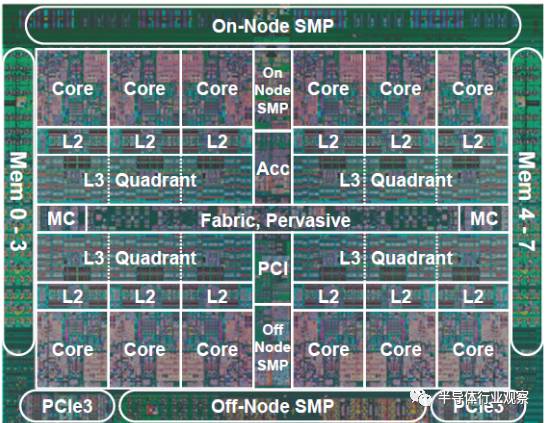

Iyer给出了答案,就是把DRAM搬到CPU的芯片上,即eDRAM(embedded DRAM)。通过使用eDRAM,CPU可以集成非常大的快速访问内存,从而大幅提高性能。例如,在IBM的POWER 8 CPU(下图)中,使用eDRAM作为L3 Cache,集成了高达80MB的eDRAM在芯片上。Iyer也因为在eDRAM方面的工作获得了IBM第四次为他颁发的杰出技术贡献奖。

重返校园:后摩尔定律时代的诗

Iyer在2015年选择回到母校UCLA,目前在电子工程系领“杰出教授”头衔。

在目前,摩尔定律的发展由于器件特征尺寸接近极限而正在变慢。那么如果摩尔定律遇到瓶颈了,我们该怎么办呢?有一种思路,就是“More than Moore”,即不使用直接缩小器件而是挖掘CMOS电路系统其他地方的潜力来进一步实现集成度和性能的提升。在UCLA,Iyer的志向是使用封装技术来实现“More than Moore”。

在当代SoC技术中,所有的片上模块都必须使用同样的工艺。然而,这样会遇到各种各样成本以及技术上的问题。从模块划分角度来看,不同的模块有不同的需求。举例来说,高性能数字模块(如GPU和APU中的运算单元)需要非常快的操作速度,因此更适合使用特征尺寸小的先进CMOS工艺。相反,对于模拟、射频以及混合信号电路来说,先进制程中由于电源电压较小,因此会导致较低的信噪比以及较差的线性度。

因此,这些电路其实更适合使用较成熟的工艺去实现。如果使用SoC,则所有模块都使用同一种工艺,显然不是最优解。因此,使用封装技术实现More than Moore的第一个好处就是不同的模块可以用各自合适的工艺去实现,最后再用封装技术集成在同一封装内。

More than Moore第二个解决的问题是内存访问问题。之前提到过,Iyer提出的eDRAM可以部分解决片上SRAM不够大的问题,但是对于主内存(容量高达几GB)的访问功耗和延迟问题,光eDRAM还是不够的。More than Moore通过高级封装技术把内存与处理器放在同一封装内,从而实现高速内存访问。目前Nvidia的GPU已经在使用基于HBM封装技术的超高速内存以保证性能,可以说是More than Moore的胜利。

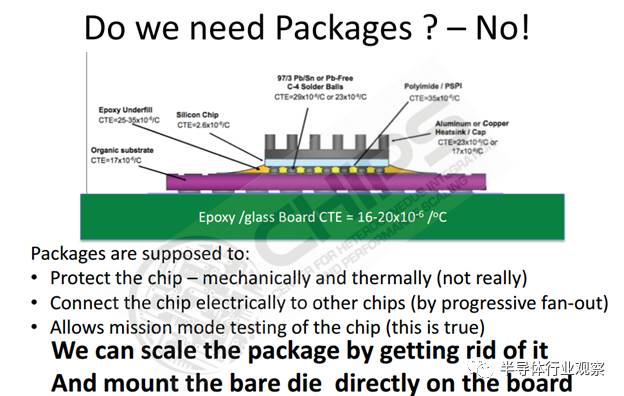

话说回来,Iyer在UCLA的More than Moore研究是大规模异质互联。目前异质互联的模块数量还不高,往往只有两三个芯片模块在封装内做异质互联。Iyer的研究目标则是把异质互联芯片模块数量提升到数十个甚至上百个,而且去掉封装,把所有的芯片直接装在板上。

为什么需要大规模异质互联?这是因为目前小规模异质互联中,每一块芯片都是大规模定制芯片,很难形成规范,也很难统一接口标准。这就造成了设计上的困难,也很难规模化。而且,芯片之间引脚的间距不定,通讯接口必须使用功耗较大的SerDes,这就造成了功耗过大。

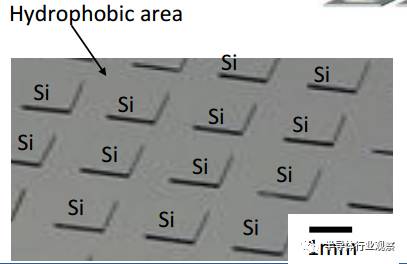

Iyer的思路是,把一块大芯片拆成很多小而且接口标准化的小模块芯片(Dielet),之后用封装级互联集成到一起。由于每块芯片的尺寸小而且形状固定,因此芯片间的间距也可以做到很小,这样大部分SerDes可以省去,只留下部分距离很远的引脚需要SerDes,这就节省了功耗。而且,由于接口和尺寸标准化,因此可以更容易地把规模做大。每一块小芯片都可以是一个IP,这样就诞生了一个新的大规模异质互联的生态。

Dielet互联

为了实现这一伟大目标,Iyer教授在UCLA建立了异质集成与性能进化中心(Center for Heterogeneous Integration and Performance Scaling, CHIPS),并与各个领域的众多大咖(如计算机领域的Jason Cong,医学院的Tzung Hsiai等)合作。让我们期待这位Super Star在UCLA的作为!

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“半导体行业观察icbank”微信公众号。谢谢合作!

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 [email protected]

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 [email protected]

点击阅读原文加入摩尔精英