点击上方

蓝字

关注我们,看更多行业报告

并将

“材料汇”

设为“星标⭐”,第一时间收获最新推送

写在前面

一直在路上,所以停下脚步,只在于分享

分享内容包括:

新

材料/

半导体

/

新能源/光伏/显示材料

等

正文

文章要点:

1、目前集成电路95%以上都采用塑料封装,塑料封装主要应用于民用电子元器件的封装领域。只有航天、航空及军事等高可靠性需求的领域采用金属和陶瓷封装。

2、全球封装基板供应商主要来自日本、韩国和中国台湾地区。包括揖斐电株式会社、新光电气工业株式会社、京瓷集团、三星电机、信泰和南亚科技、欣兴电子、深南电路、珠海越亚、兴森快捷、深圳丹邦、安捷利、中兴新宇、芯智联。另外,软板COF基板的供应商主要有日本旗胜、韩国LGINNOTEK、中国台湾易华电子及韩国STEMCO等。

3、近年来,为满足先进封装产品的要求,各种基板新工艺层出不穷。基板供应商围绕提高材料性能、降低材料成本的方向,不断探索实现封装基板小型化、薄型化、高密度布线、高频高速信号传输的解决方案。

4、覆铜基材是基板制造的核心材料,其发展重点在于提高Tg、降低厚度,加入功能粉体使基材具有散热、埋容功能等,其中聚酰亚胺(PI)是柔性基板中常用的树脂材料,未来采用低介电常数的LCP和氟系树脂材料的覆铜基材在今后的使用量会不断增加。

5、由于集成电路不断朝轻、薄、小的方向发展,因此对基板材料在热、力等方面的固有性能提出了更高的要求。对于刚性基板,其发展重点主要是降低热膨胀系数和提高热导率;对于柔性基板,则要求其在保持高柔性和透明性的同时,降低热膨胀系数、提高热导率和热稳定性。

6、目前主要的研究热点包括负热膨胀系数无机填料技术、无机导热粒子及其表面改性技术、高填充技术、高导热树脂及聚合物改性技术等。

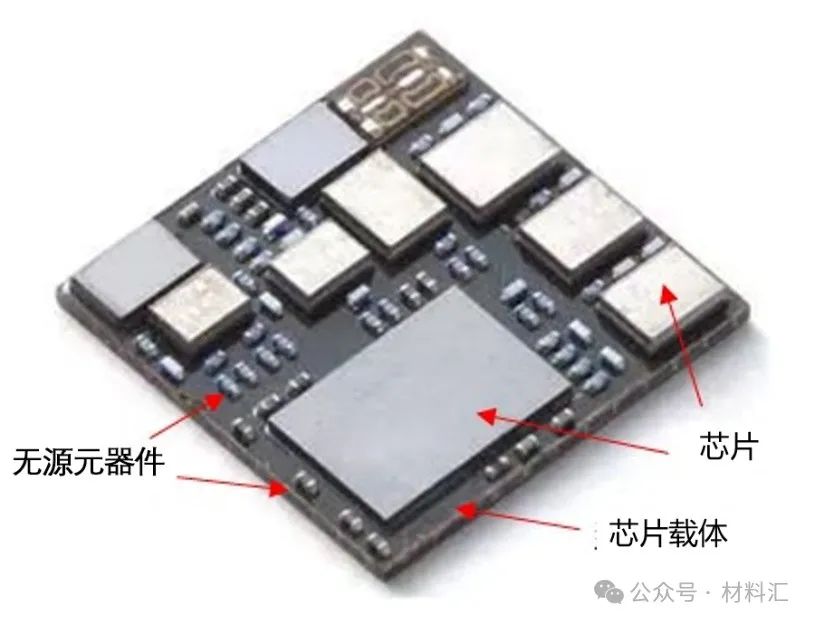

芯片载体材料(Chip carrier)一般又称为封装载板或封装基板

,是集成电路封装的关键材料,是集成电路的重要组成部分,是裸芯片与外界电路之间的桥梁,图1所示为SiP集成封装组件图。

图1 SiP集成封装组件图

芯片载体材料在集成电路封装中的主要作用包括:

(1)为芯片/芯片与芯片/组装用印制电路板之间

提供电流和信号的连接

。

(2)为芯片提供

机械的支撑和保护

。

(3)芯片向外界

散热

的主要途径。

(4)芯片与外界电路之间

空间上的过渡

。

集成电路封装按照常用的芯片载体的材料可以分为

金属封装、陶瓷封装和塑料封装

三大类。其中,金属和陶瓷封装属于气密性封装,塑料封装由于有机材料本身的材料特性(如吸潮等)属于非气密性封装或准气密性封装。塑料封装具有成本低、生产效率高、适合大规模工业化生产的特点,

目前集成电路95%以上都采用塑料封装,塑料封装主要应用于民用电子元器件的封装领域

。

只有航天、航空及军事等高可靠性需求的领域采用金属和陶瓷封装

。

一、芯片载体材料在先进封装中的应用

(一)芯片载体材料的产生与发展

传统的IC封装采用金属引线框架(Lead-frame)作为支撑和保护芯片的载体

,IC封装通过分布在两侧或四周的引脚与芯片焊盘形成电连接,如四方扁平封装(Quad Flat Package,QFP)。随着芯片功能不断增加,芯片需要的I/O端口数越来越多,传统的引线框架无法满足高密度引脚需求。当引脚数超过300个时,QFP等传统封装形式已经不能满足高密度封装的需求,因此出现了以

球栅阵列封装、芯片级封装等为代表的面阵列封装形式

,随之产生了封装基板这一新型的芯片载体。

与引线框架类封装相比,基板封装具有引脚数更多、封装尺寸更小及优良的电学性能等突出优点。

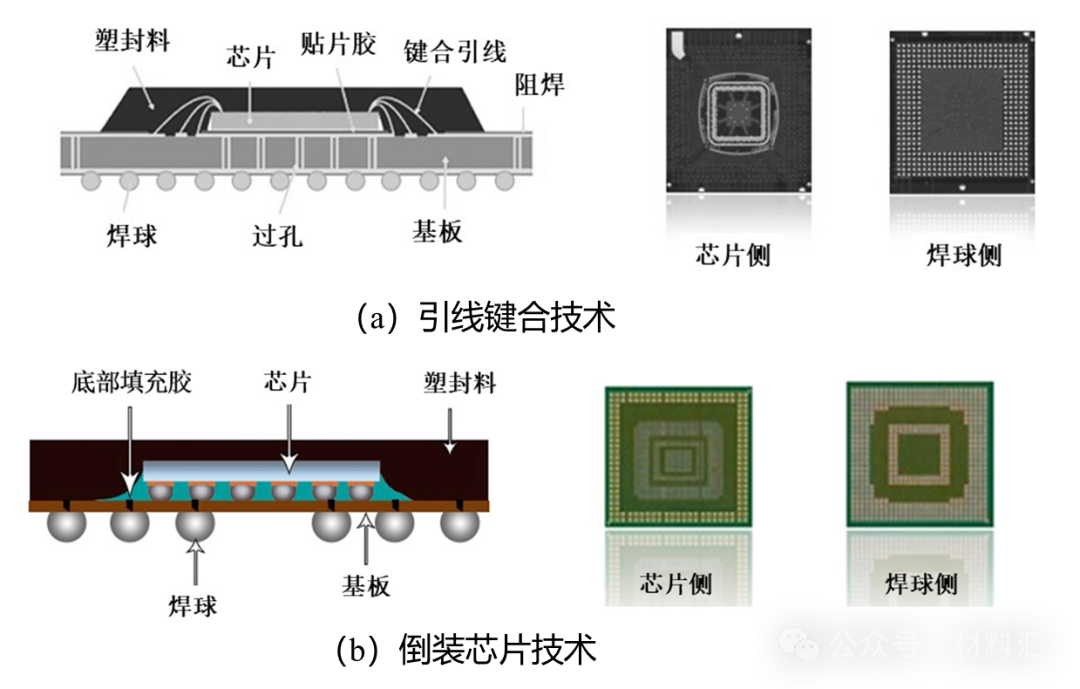

引线键合(Wire Bonding,WB)和倒装芯片(Flip Chip,FC)技术是实现封装基板与芯片间电互连的常用技术,

如图2所示。

图2 封装基板与芯片的常用互连技术及相应封装基板

引线键合技术使用金、银、铜等金属或合金键合丝

,通过施加热、压力、超声波能量使金属丝与基板和芯片焊盘紧密焊接实现互连。

引线键合技术是目前主流的芯片封装互连技术

,其发展成熟、成本较低、可靠性高,

尤其适合多芯片堆叠,被广泛应用于闪存芯片封装,75%~80%的芯片封装采用引线键合技术,引线键合技术占有约90%的市场份额

。在引线键合技术中,焊盘以周边阵列的形式分布在芯片表面,可支持的单个芯片最大I/O端口数可达1000个,最小焊盘节距可达到40μm以下,相应地,键合引线的直径持续缩小至0.6mil(约15μm)乃至更细。

倒装芯片技术首先在芯片表面制造金属凸点,然后把芯片有凸点的表面翻转并通过回流、热压等方式使其与基板上对应的焊盘键合。与引线键合技术相比,倒装芯片技术具有很多优点,主要包括优异的电学性能和热学性能、可支持更高的I/O端口数、封装尺寸更小等。

倒装芯片技术通过凸点实现电互连

,相较键合引线大幅缩短了互连长度,降低了电阻,减小了RC延迟,改善了封装的电学性能。金属凸点热导率高,呈面阵列形式均匀排布在芯片表面,是很好的散热通道,再配合散热片、封装及基板结构的设计,可以降低热阻,提高封装的导热性。

引线键合技术的局限性主要在于互连线只能在芯片四周排布,要提高引脚数必须不断缩小焊盘尺寸和节距。而采用面阵列分布的倒装芯片技术可以在较大的焊盘尺寸和节距下实现更高的封装密度,且线路分布更灵活,基板焊盘的位置与芯片焊盘基本一致,布局更加紧凑,减小了封装的外形尺寸。因此,

倒装芯片技术更适用于高I/O端口数、功能多、功耗高、频率高的IC封装产品中

。与其他封装材料的发展规律相似,封装基板也是随先进封装技术的演进而不断发展的。

近年来,倒装芯片技术得到了广泛的应用,

倒装芯片类封装基板逐渐取代引线键合类封装基板,成为核心基板产品

。

目前,

全球封装基板供应商主要来自日本、韩国和中国台湾地区

。其中以

揖斐电株式会社(Ibiden)、新光电气工业株式会社(Shinko)、京瓷集团(Kyocera)

等为代表的日本公司技术实力非常强,占据着有机基板中利润率最大的中央处理器封装所需基板的主要市场;韩国的

三星电机(SEMCO)、信泰(Simmtech)和中国台湾的南亚科技(Nanya Technology)、欣兴电子(Unimicron)

等公司由于具有产业链的优势,占据着市场中的重要份额。另外,软板COF基板的供应商主要有

日本旗胜(Nippon Mektron)、韩国LGINNOTEK、中国台湾易华电子及韩国STEMCO

等。

中国大陆地区封装基板产业由于起步较晚,加之在关键原材料、设备及工艺等方面的差距,因此目前在技术水平、工艺能力及市场占有率上相较日本、韩国和中国台湾地区的知名封装基板产业仍然处于落后地位。中国大陆地区主要的封装基板制造企业都不是本土企业。出于市场及劳动力成本的考虑,台资封装基板制造商(如Unimicron、Nanya PCB、Kinsus、ASEM及臻鼎科技等)陆续在中国大陆建立了相应的制造基地,但是其高端封装基板还没有在中国大陆大规模生产。

在内资企业中,率先介入封装基板行业的企业主要有

深南电路股份有限公司(简称深南电路)、珠海越亚半导体封装基板技术股份有限公司(简称珠海越亚)、深圳兴森快捷电路科技股份有限公司(简称兴森快捷)、深圳丹邦科技股份有限公司(简称深圳丹邦)、安捷利实业有限公司(简称安捷利)、深圳中兴新宇软电路有限公司(简称中兴新宇)

等,香港金柏科技有限公司、江苏长电科技股份有限公司(简称长电科技)投资成立了专注于MIS基板的

江阴芯智联电子科技有限公司(简称芯智联)

。

(二)芯片载体材料的分类与应用

根据材料及应用的不同,封装基板可以分为

陶瓷基板、金属基板、有机基板及硅/玻璃基板(中介转接层)

等。

1.陶瓷基板

陶瓷是封装基板最初选用的材料,这种材料可以支持较高的I/O密度,材料性能非常稳定,其热膨胀系数与硅接近,适用于气密性封装。

陶瓷基板是在陶瓷基材表面制造金属导电图形而制成的,通常采用烧结工艺将陶瓷与金属紧密结合。

陶瓷基板的优点主要包括高耐热性、高热导率、热膨胀系数适当和易实现精细布线等

。按烧结温度的区别,

陶瓷基板可分为高温共烧陶瓷(High Temperature Co-Fired Ceramics,HTCC)基板和低温共烧陶瓷(Low Temperature Co-Fired Ceramics,LTCC)基板

。

二者的主要差异在于玻璃含量不同,前者玻璃的含量在8%~15%之间,后者玻璃的含量大于或等于50%

。一方面,玻璃可以降低介电常数,有利于制造高速电路;另一方面,玻璃会降低共烧陶瓷基板的机械强度和热导率。

共烧法是制造多层电路陶瓷基板常用的金属化方法

,采用共烧法的优点包括可以形成精细布线并实现多层布线;绝缘层和导体层形成一体化结构,可以实现气密性封装;可以通过成分、成型压力和烧结温度等参数的选择,控制烧结收缩率等。

高温共烧陶瓷基板材料包括氧化铝(Al2O3)、氮化铝(AlN)、碳化硅(SiC)等,烧结温度一般在1500~1900℃之间

。氧化铝的价格低、综合性能好、气密性好、可靠性高,但其热导率仅为20W/(m·K),介电常数约为10,无法适应集成电路的发展要求,需要进行性能改良。此类低介电常数的陶瓷基板,易实现多层化,主要用于高速器件封装,如高频器件的输入输出板、光通信器件、混合集成电路等。氮化铝的热导率是氧化铝的20倍,热膨胀系数与硅相匹配,且具有机械强度高、质量小等优点,是高密度、大功率电子封装中理想的陶瓷载板,广泛应用于高频器件、高亮度发光二极管、半导体激光器件、大功率晶体管器件等产品中。碳化硅的机械强度仅次于金刚石,具有优良的耐磨性和耐腐蚀性,其热导率高于铜,且热膨胀系数与硅更接近,但其介电常数较高,仅适用于低电压电路及高散热器件的封装。

低温共烧陶瓷基板的烧结温度一般在850~950℃之间

,由于温度较低,金、银、铜等低电阻率的材料都可以被选作导体金属,因此形成的电路图形更加精细,可以实现高密度布线。低温共烧陶瓷基板具有介电常数低、热膨胀系数与硅接近、机械强度高等优点,是制造复杂集成电路多芯片产品的重要部件。其主要应用领域包括超级计算机部件、新一代汽车用电子控制单元部件、高频控制部件、高电子迁移率三极管及光通信用界面模块等。

2.金属基板

金属基板是以铝、铜、铁、钼等金属板为基材,在基材上制造绝缘层和导电层(铜箔)而制成的

。

金属基板的优异性能包括散热性、机械加工性、电磁屏蔽性、尺寸稳定性、磁性及多功能性。金属基板在集成电路、汽车、办公自动化、大功率电子器件、电源设备等领域有很多应用,在发光二极管封装产品中的应用更为广泛。此外,由于金属封装材料可以作为大面积浮动地线使用,可以减少信号间电感、电容及串扰,加之其电磁屏蔽功能,因此常用于军事和一些定制的专用气密性封装中。

3.有机基板

有机基板是在传统印制电路板的制造原理和工艺的基础上发展而来的。与传统印制电路板相比,有机基板的板子薄、线路密、对位精度要求高、电气结构更复杂,其制造难度远高于传统印制电路板。早期有机基板产品以双面基板为主,而随着高功能集成电路I/O端口数的增加及高散热性的要求,有机基板逐渐向多层化、薄型化和高密度化发展。有机基板主要面向计算机、通信产品、消费类电子及汽车电子产品等方面的应用。

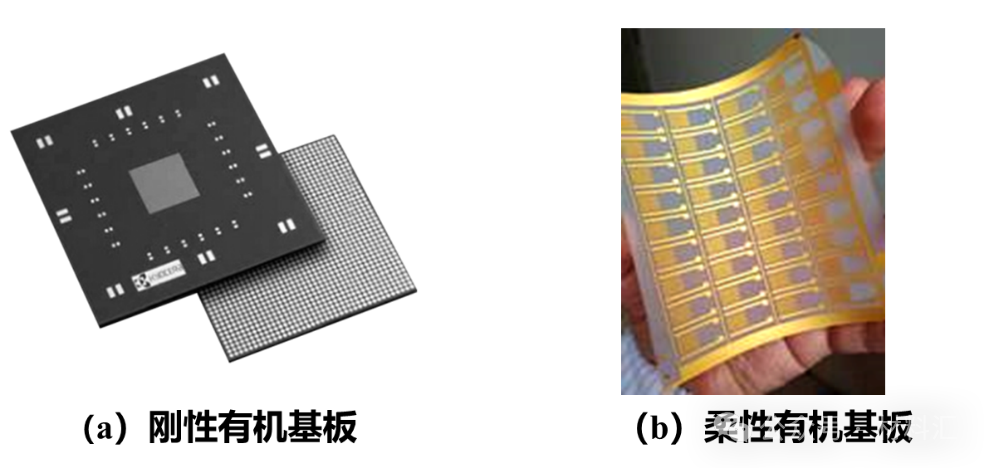

根据不同的物理特性和应用领域,

有机基板可分为以有机树脂为基材的刚性有机基板和以柔性薄膜为介质层的柔性有机基板

,如图3所示。

图3 有机基板

刚性有机基板是以有机树脂,特别是热固性树脂(如BT)为基材,以无机填料和玻璃纤维为增强材料

,首先采用热压成型工艺制成层压板,然后与铜箔复合制成的。刚性有机基板面向的封装包括引线键合(WB)类和倒装芯片(FC)类的球栅阵列封装、芯片级封装等。其中,WB-BGA产品被广泛应用于各种通用芯片的封装;计算机和服务器中的处理器(中央处理器、图形处理器等)及一些南北桥芯片采用FC-BGA封装;智能手机中的处理器及其他部件(如基带、蓝牙等)则多采用倒装芯片尺寸级封装(Flip Chip-Chip Scale Package,FC-CSP)。

柔性有机基板主要采用热膨胀系数低且平整度较高的PI薄膜作为介质层

,由介质层与铜箔通过适当的工艺复合制成,多采用卷对卷带式加工实现大批量生产。柔性有机基板封装形式包括球栅阵列封装、芯片级封装、COF(Chip On Flex)等,其应用包括发光二极管/液晶显示器、触控屏、计算机硬盘和光驱的连接及功能组件、智能手机、平板电脑、可穿戴电子设备中对柔性要求较高的电子产品。

4.硅/玻璃基板(中介转接层)

三维集成技术可以将多个不同功能的芯片及无源器件组成的高性能系统集成在一个封装模块中,形成功能完整、高性能集成的微系统,目前逐步在通信(如智能手机等)、传感器探测(如可穿戴电子设备等)等领域得到广泛应用。

但三维集成技术仍面临集成工艺和技术方面的障碍与挑战,如

工艺兼容性问题

,实现异质集成需要兼顾不同材料、不同结构、不同集成工序的差异;

可靠性问题

,某一个芯片、元件、模块出现问题都可能导致微系统整体的失效。

为解决以上问题,出现了

基于封装通孔(Through Package Via,TPV)的中介转接层(Interposer)技术

。利用中介转接层来实现多个芯片之间的互连和再布线,将芯片IO数减少后再连接到传统基板或印制电路板上。中介转接层可以广泛应用于图形处理器(GPU)、现场可编程门阵列(FPGA)及专用集成电路(Application Specific Integrated Circuit,ASIC)等器件的异质集成中,

目前已成为先进封装技术中的关键材料之一

。

中介转接层的制造基于集成电路工艺,使用的图形转移技术基于集成电路制造前道工艺的光刻而非传统基板工艺,图形可以更加精细,满足更大尺寸芯片的精细布线要求。

应用于先进封装的中介转接层材料按照基体材料的不同主要分为硅、玻璃及有机体系三大类

,对中介转接层材料的主要要求包括高热导率、低热膨胀系数、低介电常数等。由于在热膨胀系数方面和功能芯片匹配,可以在很大程度上减小芯片与基板之间的应力,因此硅/玻璃中介转接层的应用十分广泛。

由于硅具有十分平整的表面和良好的物理性能,因此硅中介转接层可用于几乎所有集成电路器件的封装中,如超高速、散热要求高的应用。硅中介转接层的优点还包括可在其中埋置电阻和有源器件;可通过掺杂使其起到接地层的作用,省去金属化;与硅晶圆的热膨胀系数完全匹配;硅的热导率[85~135W/(m·K)]较高;易于用铝或其他金属进行金属化等。

与硅材料相比,玻璃的优点包括玻璃为绝缘材料,可以省去在通孔内部制造一层绝缘层的工艺,成本有所下降,且高频传输特性更优;玻璃的热膨胀系数可调,可以获得更好的热匹配性,从而减少热处理后的基板弯曲;玻璃的成型性能好于硅,可以获得更平整更薄的基板,从而取消背面减薄工艺,并且玻璃比单晶硅便宜。

陶瓷基板和金属基板的制造工艺较复杂、制造效率较低、造价较高,多用于有高可靠性要求、大功率、高频的气密性封装产品中

。

硅/玻璃中介转接层采用前道工艺制造,与传统基板制造工艺相比成本较高,多用于高端三维集成封装中

。由于以上几类基板的应用范围有限,且市场占有率不高,因此不进行重点介绍。针对市场占有率高的有机基板材料,将对其类别、性能及技术发展进行详细分析和阐述。

二、硅/玻璃中介转接层的基本结构及关键工艺

(一)TSV关键工艺及材料

硅通孔(TSV)技术是硅中介转接层的关键技术。

利用硅片制造带有TSV的硅中介转接层可以实现垂直方向上各层芯片、被动元件等结构的异质集成及电互连,这种封装形式被称为2.5D封装。TSV的制造可以通过不同的工艺方法和工艺顺序实现,硅中介转接层中的TSV制造一般采用前道工艺。

如图4所示,TSV制造工艺流程包括:

(1)

深孔制造:干法刻蚀

制造高深宽比的孔。

(2)在深孔侧壁

沉积绝缘层和扩散阻挡层

。

(3)在深孔侧壁

沉积种子层

。

(4)

电镀铜填充

:在深孔内填充金属。

(5)

正面CMP

:去除表面的过电镀金属层。

(6)

正面RDL布线

:利用再布线层工艺在表面进行布线,实现电互连。

(7)利用临时键合胶将硅片正面与基板

临时键合

在一起。

(8)通过机械研磨、抛光对硅片背面进行

减薄

,并暴露出导电铜柱。

(9)

背面RDL布线

:利用再布线层工艺在硅片背面布线,实现电互连。

图4 TSV制造工艺流程图

以下将针对TSV制造的关键工艺进行介绍。

1.深孔刻蚀

TSV深孔刻蚀要求快速制造侧壁光滑的深孔,同时保证TSV的高深宽比。减小孔径可以增大T

SV的密度,因此,

小孔径、高深宽比的TSV结构是三维集成电路发展的关键

。由于侧壁的起伏会导致小孔径TSV制造困难,并且影响热力学性能、铜扩散等,可能带来可靠性问题,因此

减小甚至消除侧壁起伏也是TSV制造的技术目标之一

。

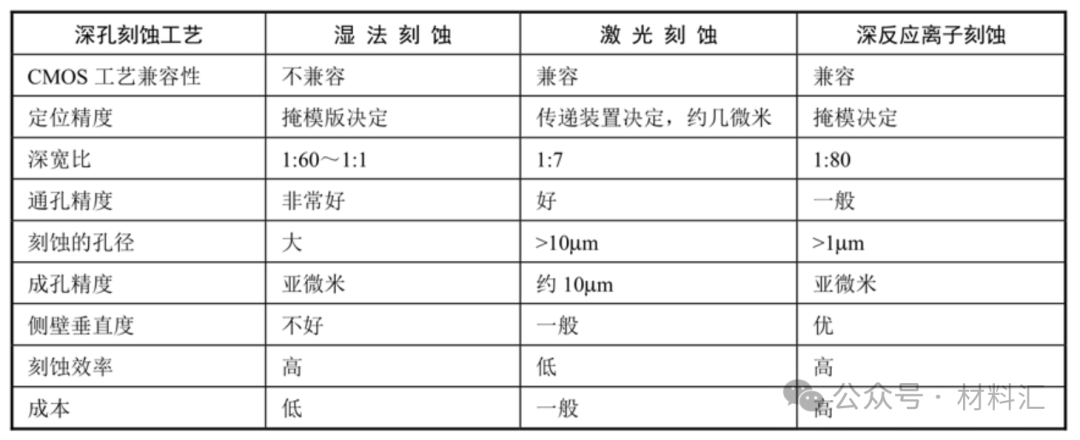

目前,制造TSV的深孔刻蚀工艺主要包括

湿法刻蚀、激光刻蚀、深反应离子刻蚀(干法刻蚀)

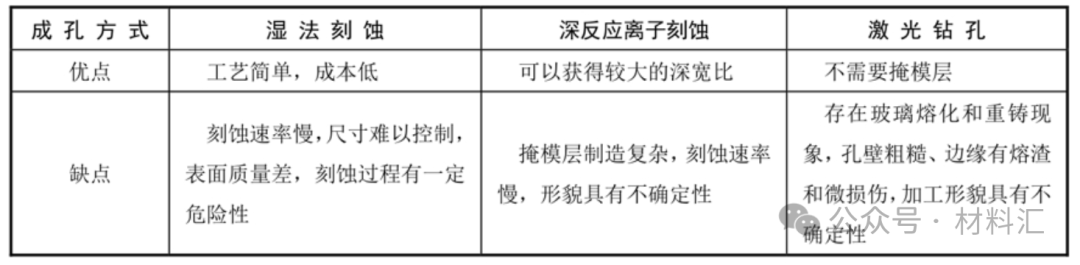

。深孔刻蚀工艺的对比如表1所示。

表1 深孔刻蚀工艺的对比

湿法刻蚀工艺采用氢氧化钾(KOH)或四甲基氢氧化铵(TMAH)对硅衬底进行化学腐蚀。

这种工艺的刻蚀温度低,制造成本低,适合于批量生产。但是,由于刻蚀出的通孔不是垂直结构的且孔径较大,因此只能用于低输出端数的封装,无法制造小孔径高密度的TSV结构。

激光刻蚀工艺依靠光子能量熔融硅而制造通孔,是一种加热熔化的物理过程

。激光刻蚀工艺不需要掩模版,工艺简单,在大规模制造中有成本优势。但是,这种工艺制造出的通孔,内壁粗糙度和热损伤较高,不利于后续绝缘层和扩散阻挡层的制造。

相对于前两种工艺,

深反应离子刻蚀(Deep Reactive Ion Etching,DRIE)

工艺更易制造高深宽比且侧壁垂直度和光滑度良好的TSV结构。深反应离子刻蚀是基于博世(Bosch)工艺原理实现的各向异性刻蚀方法,是一种刻蚀和保护交替进行的过程。图5描述了一个博世工艺刻蚀周期。

图5(a)是

钝化过程

,氟化物(C4F8)在通孔的侧壁和底部形成钝化层,阻止等离子体对底部和侧面产生刻蚀。

图5(b)是

初始刻蚀过程

,在离子能量作用下孔底部的钝化层被去除,钝化层下面的硅暴露出来,侧壁的保护层则因为轰击作用较弱而保留下来。

图5(c)是

刻蚀过程

,暴露出来的硅在等离子体(SF6)作用下被刻蚀,经过这个过程通孔的深度增加。

图5 博世工艺刻蚀周期

当每个刻蚀周期的刻蚀过程结束以后,深反应离子刻蚀设备会自动进入下一个刻蚀周期,经过多个刻蚀周期以后可以在硅上得到高深宽比(High Aspect Ratio)的孔。

深反应离子刻蚀由多次刻蚀循环叠加而成,因此制造出的TSV结构的侧壁会出现贝壳状的起伏。根据深反应离子刻蚀工作机理,降低刻蚀循环中的刻蚀时间,可以有效地降低侧壁的起伏程度,但是这样将降低刻蚀速率,提高深孔制造的成本。此外,提高等离子体密度可以降低侧壁的起伏程度。这是由于刻蚀气体氟的等离子体密度的增高将会提高硅的刻蚀速率,进而在更短的刻蚀时间内完成所需的刻蚀深度。因此,

通过优化深反应离子刻蚀的工艺参数,可以获得满足特性需求的TSV结构

。

2.TSV侧壁薄膜层制造

TSV侧壁薄膜层主要包括绝缘层、扩散阻挡层和种子层

,这几种膜层的制造方法和材料特性之前的硅通孔相关材料中有详细的说明。

硅是半导体材料,因此TSV需要在导电铜柱与硅衬底之间制造绝缘层进行绝缘,从而隔离电子,避免漏电。常用的

绝缘层材料有二氧化硅(SiO2)、氮化硅(SiN)、氮氧化硅(SiNO)等

。常用的技术手段主要有

PECVD和热氧化工艺

两种。在晶圆正面制造绝缘层时,可利用

热氧化工艺制造SiO2绝缘层

。而在晶圆背面制造绝缘层时,需要保护临时键合材料及凸点,应采用非标准工艺,可以用

PECVD在低温(200℃)下进行绝缘层的沉积

。

利用热氧化工艺制造SiO2绝缘层,反应炉中的温度很高,工艺中常用的氧化温度为1100℃,工艺时间长。热氧化工艺制造的SiO2薄膜具有均匀性高的优良特点。根据反应炉中氧化气氛的差异,热氧化工艺可分为三类:干氧氧化、水汽氧化和湿氧氧化。

干氧氧化制造的SiO2薄膜结构紧密,掩盖性好,与光刻胶有很强的黏附力,不易产生浮胶,制造时间长。水汽氧化的氧化速率快,但是由于工艺环境中含有大量的水分子,因此制造的SiO2薄膜结构疏松,表面会出现明显的缺陷,含水量高,与光刻胶的黏附力差,容易产生浮胶。湿氧氧化实际上是干氧氧化和水汽氧化的结合,兼具干氧氧化和水汽氧化的优缺点。此外,还有一种结合干氧和湿氧的氧化方式,即干氧—湿氧氧化(交替进行干氧氧化和湿氧氧化),其制造的SiO2薄膜与光刻胶的黏附力强,氧化速率介于湿氧氧化和干氧氧化之间。

在垂直的TSV内实现均匀性、连续性好的扩散阻挡层和Cu金属互连层(铜填充过程的电镀种子层)是保证电镀质量及TSV可靠性的关键技术

。薄膜制造工艺方法主要包括

物理气相沉积、化学气相沉积和化学镀沉积(Electroless Deposition,ELD)

等。

物理气相沉积是制造扩散阻挡层和种子层的主流工艺,沉积的薄膜纯度高、成本低。但物理气相沉积在高深宽比的垂直微孔内沉积薄膜时存在台阶覆盖率的问题,因此沉积的薄膜厚度在微孔内壁的分布不一致,从而会影响金属互连的可靠性。

化学气相沉积能在高深宽比微孔内壁得到厚度均匀的扩散阻挡层,工艺温度适中,制造薄膜的速率快,但是成本昂贵,并且化学气相沉积制造的铜种子层和扩散阻挡层之间的黏附力较差、电阻率偏高,从而会影响金属互连的电学性能。

化学镀沉积(ELD)能在高深宽比微孔内壁得到均匀致密的扩散阻挡层薄膜,但是薄膜与侧壁的结合力不好及化学镀液的不稳定性都会引起金属互连的可靠性问题。

此外,原子层沉积工艺利用自限制化学饱和反应(Surface Saturation Reactions)这一先天优势,可以制造低杂质浓度、低电阻率、均匀致密且具有高保形性的优质薄膜,但是原子层沉积工艺沉积速率慢,成本昂贵。

3.TSV填充技术

TSV制造的关键是实现TSV的导电填充,填充工艺及填充材料将在硅通孔电镀材料中作详细的阐述。根据TSV的孔径与应用,有多种通孔填充物,如钨、铜、多晶硅等,前沿的三维集成研究甚至采用碳纳米管等进行填充。

铜是目前常用的TSV填充材料,通常采用电镀方法实现通孔内铜的填充

。

常见的TSV电镀铜填充有两种方式,分别是

盲孔电镀和通孔电镀

。

通孔电镀的深孔覆盖能力很好,填充的铜比较致密,不容易形成孔洞和缝隙,并且硅片表面电镀的铜厚度可以控制。但是通孔电镀的工艺兼容性比较差,填充效率很低,填充后的铜与通孔侧壁的结合力很差。

盲孔电镀的工艺兼容性好,填充效率高,填充后的铜与通孔侧壁的结合力好,因此被广泛采用。盲孔电镀面临的问题是在填充过程中容易形成孔洞和缝隙。这些孔内缺陷对TSV的电学性能和机械性能都可能造成较大的影响,需要

通过优化电镀材料和电镀工艺实现无孔洞填充,如控制电镀成分、浓度、添加剂比例、样品预处理条件、电流参数等

。

4.铜化学机械抛光

TSV电镀填充金属铜之后,需要利用化学机械抛光技术去除表面的过电镀铜层和扩散阻挡层,使TSV中的铜柱具有相同的高度,实现硅基板表面的平坦化。铜化学机械抛光可以分为两种方式:

第一种是采用同一种抛光液利用化学机械抛光技术一次性去除过电镀铜层和扩散阻挡层;第二种是采用两步化学机械抛光工艺,分别去除过电镀铜层和扩散阻挡层。

目前,铜化学机械抛光的抛光液可以分为

酸性抛光液、中性抛光液、碱性抛光液

等不同体系。除基础溶液外,

抛光液的成分主要包括抛光颗粒、氧化剂、络合剂、抑制剂、光亮剂、pH调节剂等其他添加剂

。

抛光磨料可以采用Al2O3或SiO2纳米颗粒

。使用Al2O3作为抛光磨料进行化学机械抛光的抛光速率快。但是,在化学机械抛光过程中,残余的Al2O3难以去除,并且晶圆表面的粗糙度高。SiO2纳米颗粒在不同pH溶液中的悬浮性好,抛光后易去除,并且抛光后的晶圆表面粗糙度低。

氧化剂的作用是促进CuO的形成,在铜表面形成一层疏松的钝化物

。

常见的氧化剂主要有HNO3和H2O2

。HNO3与铜反应生成离子状态的铜,H2O2的氧化能力强,无污染。但是,H2O2易分解,不利于存储。

络合剂的作用是和铜反应生成水溶性络合物,目的是使铜离子易于溶解在抛光液中,便于去除

。

缓蚀剂的作用是与铜反应生成致密的钝化物

,抑制表面凹陷区的化学抛光过程,提高表面平整度。

pH调节剂主要用于改变抛光液的pH

。铜化学机械抛光的抛光液的配比、研磨盘转速、时间等都会对抛光效果产生不同的影响。

5.背面开窗工艺

背面开窗工艺指的是将硅中介转接层减薄到接近或超过TSV的高度后,去除底部介质层,从而将TSV从硅片背面暴露出来。

薄硅片的机械强度较低,需要在减薄前采用临时键合对硅片进行保护与支撑。临时键合的质量直接决定着硅片背面减薄和抛光的成功率。选择一种合适的临时键合工艺,特别是临时键合材料的选择,对于晶圆减薄、薄晶圆操作、晶圆保护等都有重要意义。

硅片的背面减薄主要是指去除硅基体,可分为粗减薄和精减薄两步

。

第一步,粗减薄,利用减薄机快速去除硅片背面多余的硅基体,粗减薄速率可以达到300μm/min,但得到的表面较为粗糙。

第二步,精减薄,利用化学机械抛光技术对硅片背面进行抛光,消除减薄后硅片背面存在的应力,并提高硅片背面的表面平整度,精减薄速率可达到60μm/min,能够得到粗糙度小于0.1μm的较光滑表面。

当硅片减薄后就可以进一步去除底部介质层,露出铜柱。TSV的背部开窗是实现垂直方向电互连的关键,可以通过不同的工艺方法和工艺顺序实现。

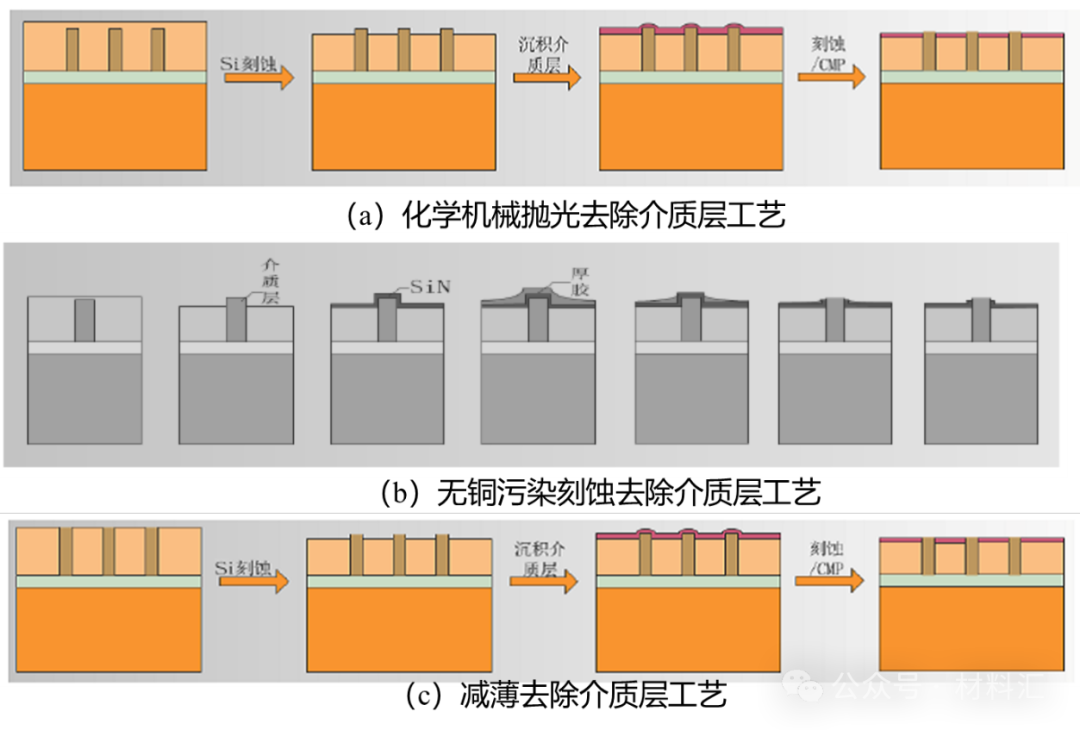

根据去除介质层的方法不同,背面开窗工艺分为三种,如图6所示。

图6 背面开窗工艺

第一种是化学机械抛光去除介质层工艺

。当圆片经过机械减薄后,首先利用刻蚀技术使TSV内部的铜柱相对于硅衬底凸出一定高度(2~10μm),然后利用低温PECVD技术沉积介质层,最后利用

化学机械抛光或刻蚀技术将TSV上方沉积的介质层去除,暴露出导电铜柱

。在这一工艺中,在铜暴露出来之前,介质层保持完整,因此铜污染相对较小。

第二种是无铜污染刻蚀去除介质层工艺

。当圆片经过机械减薄后,首先利用刻蚀技术使TSV内部的铜柱相对于硅衬底凸出一定高度(2~10μm),然后利用低温PECVD技术沉积介质层并旋涂光刻胶,并利用背部光刻技术对光刻胶进行开窗。最后利用刻蚀技术去除底部介质层,暴露出导电铜柱。在这一工艺中,始终没有铜的直接暴露,因此可以有效地避免铜的扩散污染。

第三种是减薄去除介质层工艺。

TSV底部的介质层在减薄的过程中被去除,随后利用刻蚀技术使TSV内部的铜柱相对于硅衬底凸出一定高度(2~10μm),当利用低温PECVD技术沉积介质层后,利用化学机械抛光或刻蚀技术将TSV上方沉积的介质层去除,暴露出导电铜柱。这一工艺直接将TSV抛光到同一高度,因此可以得到高度均一的铜柱。但是,在去除介质层的过程中,硅会被铜污染,导致器件失效。

在TSV背面开窗工艺中,

主要采用化学机械抛光和无铜污染刻蚀的方法去除底部介质层

。但是,由于制造深孔工艺的复杂性,孔深高度之间有一定的偏差,因此TSV高度不一致。此时,可考虑采用减薄去除介质层的方法获得高度一致性良好的TSV结构,该方法具有工艺简单、成本低的优点。

与其他基板材料相比,硅中介转接层制造技术与集成电路制造工艺兼容,具有大面积扇出能力,且工艺精度高;硅材料热膨胀系数与硅晶圆完全匹配,机械稳定性强,具有良好的应用前景。

然而,

硅中介转接层的制造是包括薄膜材料、电镀材料、化学机械抛光液材料、临时键合材料等的多种先进封装材料的综合材料制造工艺

。由于硅中介转接层制造工艺复杂、成本较高,因此目前仅用于高端三维集成封装的互连中。

硅中介转接层的一个主要问题是,硅是一种半导体材料,TSV周围的载流子在电场或磁场作用下会自由移动,对邻近的电路或信号产生影响,影响芯片性能。硅材料的介电损耗因子较大,会对高频信号传输产生不良影响。

(二)TGV关键工艺及材料

针对硅材料的缺点,提出了使用玻璃材料制造中介转接层的替代方案。玻璃是

绝缘体材料,介电损耗因子极小

,因此具有优异的电学性能。此外,在

玻璃通孔(TGV)

的制造过程中省去了绝缘层制造,从而缩短了工艺流程并降低了成本。

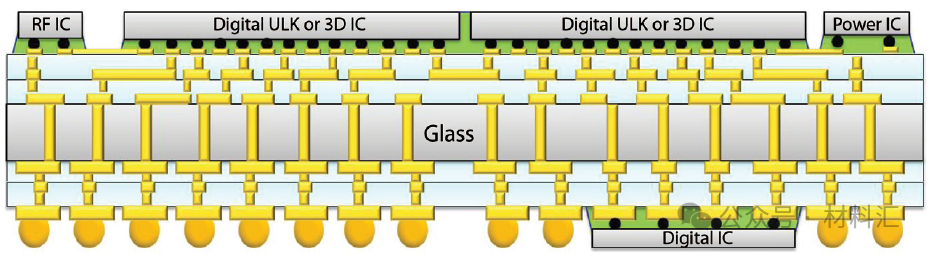

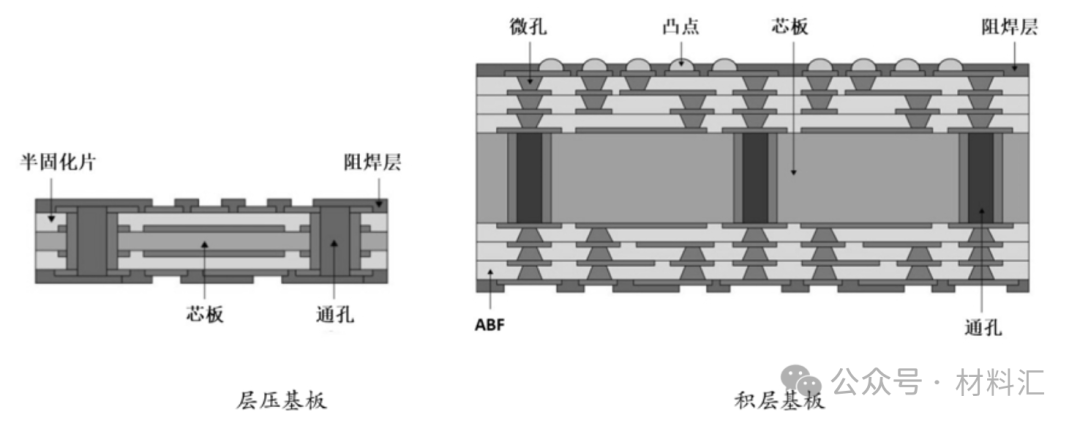

TGV互连是一种类似TSV互连的技术,图7所示为带TGV结构的系统集成示意图,其中

射频芯片(RF IC)、数字芯片(Digital ULK or 3D IC)和电源芯片(Power IC)都通过TGV技术集成在玻璃中介转接层的两侧

,实现了三维系统集成。

图7 带TGV结构的系统集成示意图

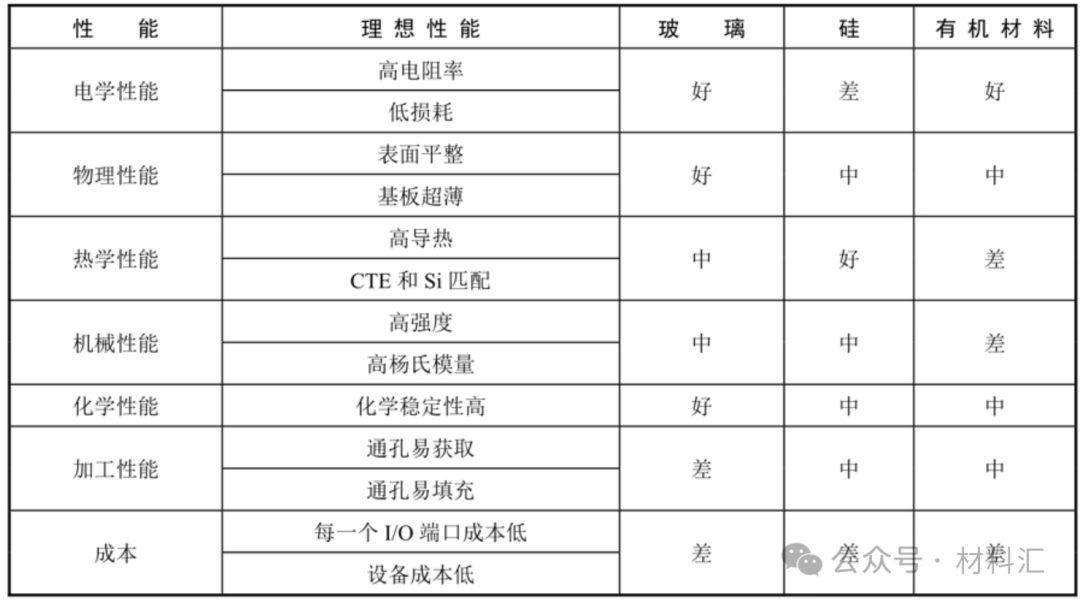

作为系统级封装中常用的基板材料之一,玻璃具有不少优于硅和有机基板的材料特性。表2对比了三种基板材料的性能,可以看出玻璃在电学性能、物理性能和化学性能方面都比较好,但其加工难度相对较大。

表2 三种基板材料性能对比

基于不同的通孔制造工艺,TGV技术主要可以分为两大类:

金属沉积制造工艺和玻璃回流制造工艺

。

金属沉积制造工艺首先在玻璃圆片上进行激光钻孔,然后在通孔中沉积金属层以实现在垂直方向上的电互连,这一工艺是目前的主流技术

。

玻璃回流制造工艺

首先将玻璃加热,在高温下施加外力或靠玻璃自身重力等使其软化,将变形的液态玻璃流入预制的硅模具中,实现热成型;然后要结合腐蚀、减薄、平坦化等一系列操作,制成具有特定形貌的TGV结构;最后将电极嵌入玻璃中实现在垂直方向上的电互连。这一工艺的

缺点是TGV的厚度和深宽比不能过大

,否则封装机械强度不高,且加工工艺的兼容性和操作性不好。

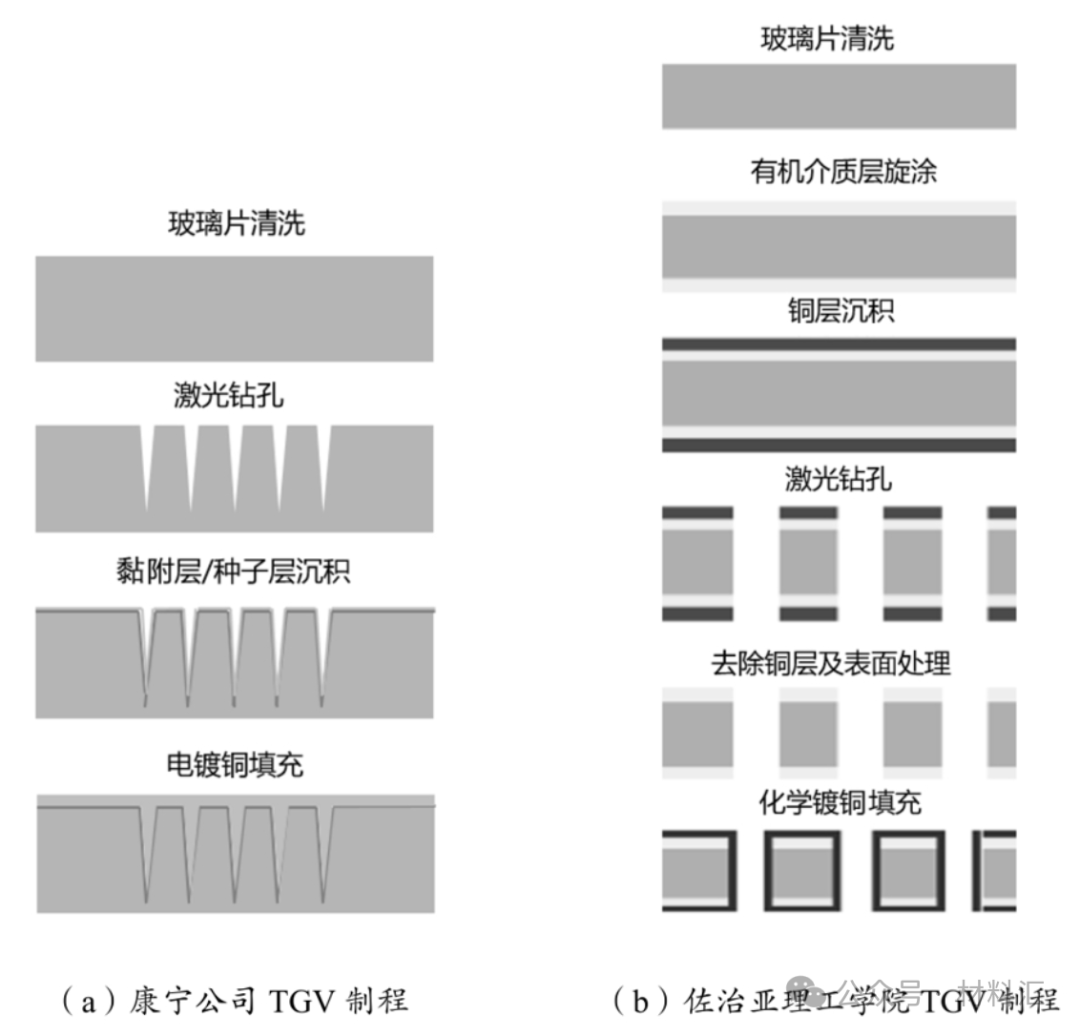

主流的TGV技术是金属沉积制造工艺

,其制程方式主要分为两种,以康宁公司的电镀和佐治亚理工学院的化学镀为代表。

图8(a)所示为康宁公司TGV制程,主要包括

玻璃片清洗、激光钻孔、黏附层/种子层沉积、电镀铜填充

四个步骤。

图8(b)所示为佐治亚理工学院TGV制程,主要包括

玻璃片清洗、有机介质层旋涂、铜层沉积、激光钻孔、去除铜层及表面处理、化学镀铜填充

六个步骤。

图8 TGV制造工艺流程图

两种制程各有优缺点:康宁公司的电镀可靠性好于佐治亚理工学院的化学镀,康宁公司采用激光的方式加工盲孔,结合盲孔电镀的方式对TGV进行填充,这对深孔TGV电镀提出了更大的挑战。佐治亚理工学院采用化学镀,其成本较低,然而制程比康宁公司的制程繁琐,工艺步骤更多,且化学铜和玻璃的结合力差。

1.TGV成孔技术

TGV成孔技术是玻璃中介转接层发展面临的重要挑战之一。在玻璃上钻孔的方法有很多,包括

湿法刻蚀、深反应离子刻蚀、激光钻孔、超声钻孔、机械钻孔、放电钻孔、电化学放电及激光诱导深度刻蚀等方法

,还包括多种方法的综合使用。不同方法有各自的优缺点,针对不同的应用环境,可以选择相应的方法。

湿法刻蚀是指利用化学试剂(包括HF、HCl、IPA等)与玻璃的反应来对玻璃进行刻蚀。湿法刻蚀是各向同性的刻蚀方法,刻蚀结构的尺寸较大、深宽比较小。

深反应离子刻蚀是指通过反应离子体(包括SF6、C4F8、CHF3、SF6/Ar、C3F7I、C3F8等气体)和玻璃进行反应,达到刻蚀的目的。深反应离子刻蚀是一种各向异性的刻蚀方法,适合进行高深宽比的刻蚀。但是,其面临的关键问题是没有类似硅的博世(Bosch)深孔刻蚀工艺,刻蚀速率慢(约为1μm/min),当刻蚀的深度过大时,时间较长,效率相对较低,并且对掩模层的厚度和性能有较高的要求,同时含氟的刻蚀气体对环境有污染。

激光钻孔技术是制造TGV的主流技术

,通过激光束对物体的照射,被照射的物体吸收激光的能量,达到对物体加工的目的。

玻璃等透明材料必须在激光能量密度高于其本身的损伤阈值时,才能实现对激光能量的非线性吸收

。激光钻孔不需要在玻璃表面制造掩模层,十分便捷、高效。然而,大部分激光器在对玻璃加工的同时伴随玻璃本身的熔化和重铸,这会导致通孔的侧壁粗糙,边缘存在熔渣和崩边现象,侧壁可能产生潜在裂纹。这些问题可能导致沉积的种子层覆盖不连续,从而增大后续金属化工艺的难度,也可能带来可靠性问题。表3对比了几种常用TGV成孔技术的优缺点。

表3 常用TGV成孔技术对比

2.TGV填充技术

与TSV相似,

TGV填充的主流技术也是电镀,电镀又分为盲孔电镀(大马士革电镀)和通孔电镀(自底向上电镀)

,两种工艺各有优缺点,其中盲孔电镀的工艺兼容性好且结合力高,所以应用更为广泛。

化学镀是佐治亚理工学院采用的填充方法,虽然成本较低,但是这种方法存在填充效率较低的问题,并且电阻很大,导电性不好。若对TGV进行无孔洞的填充,则需要采用化学镀和电镀结合的方法。此外,还有一些低成本的填充方法,如中国科学院微电子研究所研发的在玻璃孔内填充聚合物,再插入钨丝实现电互连;日本Asahi Glass公司用铜膏进行玻璃孔的填充;泰库尼斯科公司和NEC Shott开发的直插钨丝和用硅填充的TGV互连结构等。

然而,以上低成本填孔技术存在孔径受限、工艺兼容性不佳、效率低、导电性不好等问题,因此没有得到广泛应用。

三、有机基板材料类别和材料特性

(一)刚性有机基板

刚性有机基板具有优异的热稳定性、力学性能和介电性能,这些性能主要取决于其基础材料,即芯板(Core)。

芯板由多层材料压合而成,应用广泛的芯板是覆铜箔层压板(Copper Clad Laminate,CCL)或称为覆铜板

。覆铜板是以玻纤布等为增强材料,浸以绝缘的有机树脂,并在双面覆盖铜箔,经热压形成三明治式的多层结构。

常用的有机树脂材料包括BT、FR-4、PI等

,其中BT覆铜板具有较高的玻璃化温度、优异的介电性能、低热膨胀系数、良好的力学性能等优点,是目前封装基板中主流的芯板,

市场上的BT覆铜板以日本三菱瓦斯化学公司的产品为主导

。

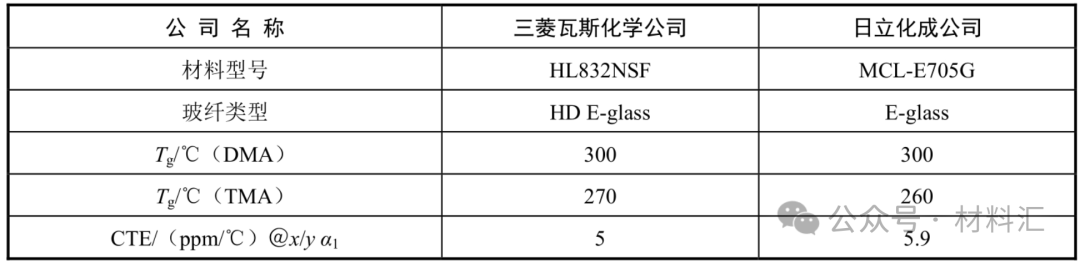

为了提高芯板材料的热力学特性,日本的三菱瓦斯化学和日立化成公司分别开发了NS系列BT覆铜板和E-7××G系列FR4覆铜板两类具有高玻璃化温度、低热膨胀系数的绿色环保型覆铜板,表4列出了典型芯板材料特性参数。

表4 典型芯板材料特性参数

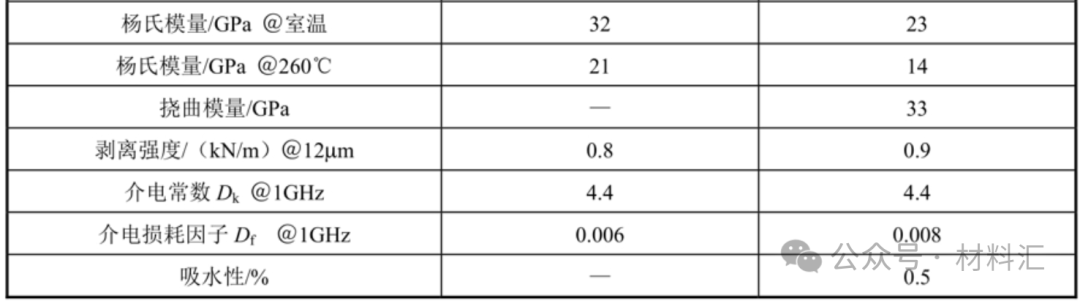

按照制板工艺分类,刚性有机基板可分为

层压(Lamination)基板和积层(Build-up)基板

两大类(见图9)。

图9 刚性有机基板

层压基板的制造工艺和传统印制电路板制造工艺相似,

其在芯板两侧将铜层和作为绝缘层的半固化片(Prepreg,PP)一层一层地交替放置,进行热压使其压合在一起,形成多层基板

。这种基板层与层之间的电气连接主要是通过电镀通孔(Plating Through Hole,PTH)实现的,即首先在多层基板上进行机械钻孔,然后在孔壁上电镀铜,各层电路在与孔壁的交汇处形成电气连接。这种基板制造工艺成熟,一般采用

两层(2L)、四层(4L)和六层(6L)金属层

的电路结构。为提高基板加工效率,同时提高后续封装效率并降低封装成本,这种基板多采用条带(Strip)形式(条带尺寸一般为16英寸×20英寸或20英寸×24英寸)开展大规模量产。PBGA封装是较早采用条带形式的封装,为了进一步降低成本,开发出了基板与芯片尺寸非常接近的芯片级封装。近年来,一部分I/O密度较低的倒装芯片封装产品(如FC-CSP)因为采用了条带形式的层压基板而具有很大的成本优势。

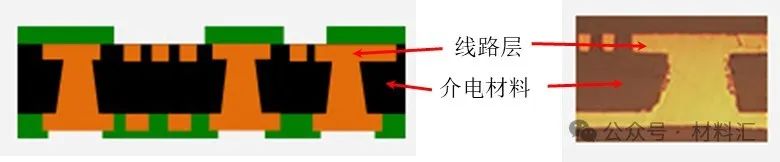

I/O端口数较多的高密度封装器件需要采用积层基板,其关键工艺是微孔技术

。首先,

在芯板的两侧对称地制造一层绝缘层

,该绝缘层材料可以采用BT或FR-4等与芯板材料相同的材料,

目前主流的绝缘层材料是由日本味之素精细化学公司生产的ABF(Ajinomoto Build-up Film)

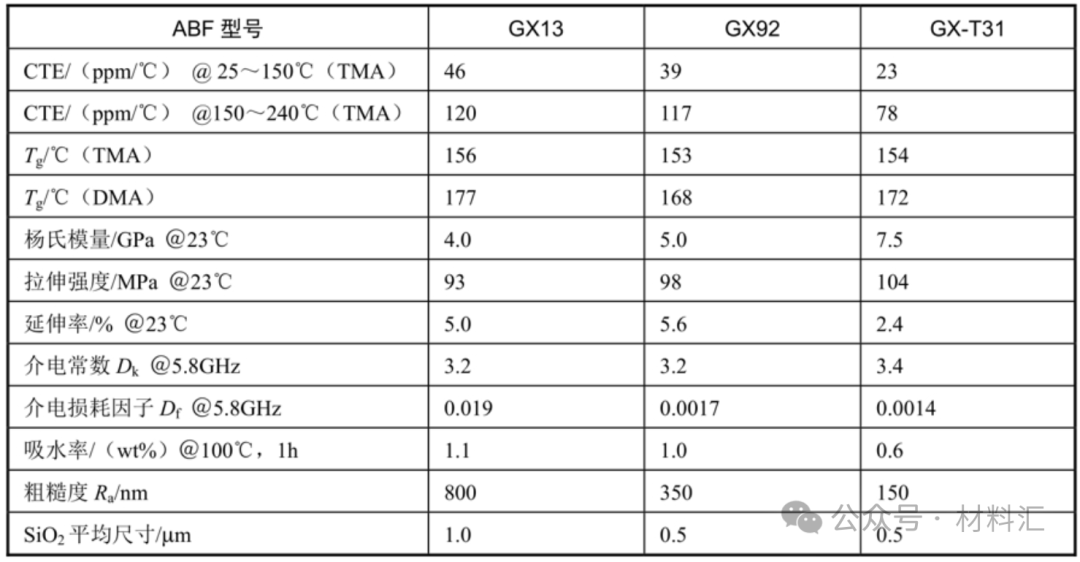

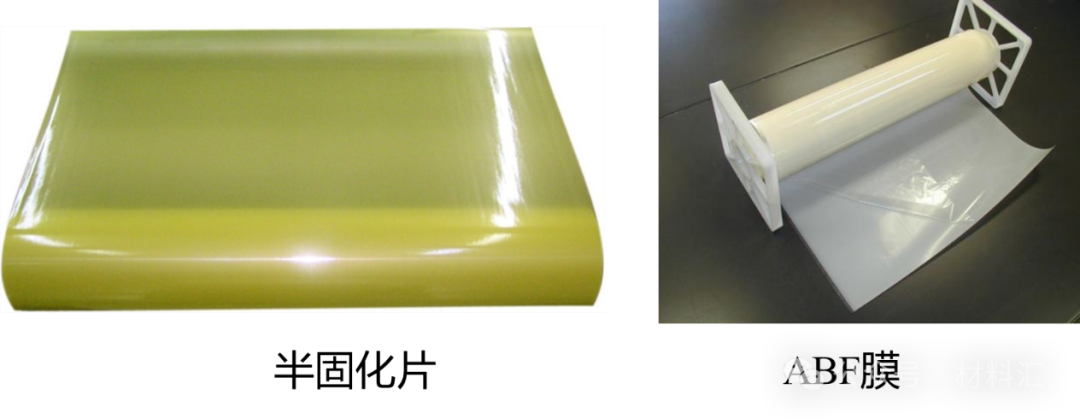

,ABF主要由树脂组成,典型ABF材料特性参数如表5所示。

表5 典型ABF材料特性参数

封装基板绝缘层材料如图10所示。然后,采用

光刻或激光钻孔的方法在绝缘层上形成微孔

,微孔的孔径目前可达到50μm左右,小于采用机械钻孔形成的PTH通孔孔径(最小约为100μm)。接着,

镀铜填充微孔,并在绝缘层表面形成电路图形

。重复以上的积层步骤可制造多积层板,如常见的1+2+1、2+2+2、n+2+n等结构。采用积层技术制造的积层基板也被称为高密度互连基板(High-density Interconnect Substrate,HDIS),这种多应用于FC-BGA等先进封装的基板和HDI印制电路板是完全不同的,高性能的积层基板出于对成品率的考虑,都采用单个(Unit)形式进行生产。

图10封装基板绝缘层材料

(二)柔性有机基板

柔性有机基板的优点主要包括挠性卷曲和折叠特性好、结构轻薄且灵活性高、互连密度高等。近年来市场对柔性有机基板的需求不断增加,其在基板产品市场中的占比迅速提高。

柔性有机基板的核心材料是聚酰亚胺(PI)。

PI是一种非常稳定的有机高分子材料,相较于聚酯(PET)、聚萘酯(PEN)等其他绝缘材料,其耐热性高,分解温度在400℃以上。PI具有优异的电学性能,玻璃化温度高、介电常数低、低密度的薄膜特性使其特别适用于高密度窄节距的轻型便携式产品,PI还具有良好的散热性,以及机械支撑性、柔软性和阻燃性等特性。然而,PI材料存在一些缺点,如易吸湿产生卷曲现象,影响器件可靠性;界面结合力较弱,不适用于多层结构;价格较高等。

传统的柔性覆铜板采用有胶型三层结构(见图11a),中间层是黏接剂,材料多选用B阶改性环氧(Epoxy)或丙烯酸(Acrylic)等。这种覆铜板的耐热性、尺寸稳定性和可靠性较差,且黏接剂中含有离子性杂质,会降低线路间的绝缘电阻,因此不能满足柔性有机基板要求的高精密度。

因此,业界逐渐转向使用二层法制造的

无胶型二层结构覆铜板的开发与应用

(见图11b)。

无胶型二层结构覆铜板仅包括PI膜和铜箔两层结构

,去除黏接剂中间层后,其耐热性、尺寸稳定性、耐腐蚀性、绝缘稳定性及长期可靠性等得到了大幅提升,不仅满足了技术需求,还可以使产品更加轻薄。

目前,无胶型二层结构覆铜板的制造方法主要分为以下三种。

(1)

浇铸法:

在铜箔表面涂覆液态的聚酰亚胺酸(PAA),经过固化形成PI膜。

(2)

镀铜法:

首先在PI膜上溅射或化学镀金属层,然后电镀铜层。

(3)

层压法:

将未硬化的PI膜与铜箔进行热压。

在以上方法中,浇铸法的工艺比较简单,产品黏接强度稳定性高,所以最为常用。

图11 柔性覆铜基材结构示意图

软板上芯片(Chip On Flex或Chip On Film,COF)柔性基板是目前主流的柔性有机基板类型。COF柔性基板具有易折叠/弯曲/扭转的特性,且布线密度高、结构轻薄,是一种新型基板,属于印制电路板中的高端产品,适于应用在先进封装技术中。

COF技术又称为芯片软膜构装技术

,其借鉴了COG(Chip On Glass)技术和TAB(Tape Automatic Bond)技术的思路,可以不通过任何封装,将

芯片直接安装到柔性基板上

。与COG技术相比,COF技术封装的芯片不需要占据面板上的区域,因此在相同尺寸的面板上可以得到更大的分辨力。与TAB技术相比,COF技术不需要制造悬空的引线从而不会产生引线变形和折断的问题,因此更易实现高密度精细布线。

与常规的印制电路板相比,CO

F柔性基板在导电及绝缘可靠性、耐热性、耐湿性及厚度均匀性等方面的性能更高。与其他形式的柔性基板相比,

COF柔性基板的主要优势包括

:

(1)体积小、厚度薄、质量轻。

(2)芯片正面朝下放置,线宽/线距更精细、性能更稳定、可靠性更高。

(3)可进行区域性回流焊。

(4)弯折强度高、形状灵活度高。

(5)可增加被动组件。

先进集成电路产品尤其是消费类电子产品,如液晶显示器、液晶电视、智能手机、数码相机、数码摄像机等,其发展方向大都是轻、薄、短、小。这要求新一代封装技术必须有体积小、集成度高、灵活性高等特点。COF技术正是可以满足这些需求的封装技术,因此得到了飞速发展。COF封装成为液晶显示器的驱动IC的一种主要封装形式,COF柔性基板成为这些显示模组的重要组成部分。

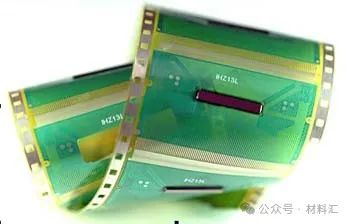

目前,

COF技术已经被广泛应用于液晶显示、PDP等平板显示模组中,并成为显示器驱动IC的主流封装技术

。三星液晶驱动IC封装如图12所示。

图12 三星液晶驱动IC封装

(三)有机基板的材料特性

随着封装技术的迅速发展,

集成电路所要实现的小型化、多功能化、高频高速、高性能及低成本等需求

,越来越多地由作为先进封装关键材料的封装基板来分担。为了解决先进封装所面临的工艺能力、电磁兼容、散热和应力等方面的问题,对有机基板材料的性能提出了更高的要求.

1、高密度化

基板的高密度首先体现为布线密度的增加,普通PBGA基板产品的线宽/线距(L/S)由传统的50μm/50μm,发展到40μm/40μm,进而发展到20μm/20μm;FC基板产品的L/S从18μm/18μm,发展到15μm/15μm,进一步发展到12μm/12μm、7μm/7μm,甚至5μm/5μm。

微互连材料的优化可以进一步提高基板密度,采用SOP焊盘结合焊料凸点的FC基板的节距可达到130μm,采用铜柱凸点(Cu Pillar)工艺则可将焊盘节距进一步减小至几十微米,从而增加I/O端口数。

基板的薄型化是其向高密度化发展的一个趋势

。芯板材料厚度不断降低,目前已有大量的40μm厚度的芯板应用于基板制造,30μm厚度的芯板已得到小批量应用。同时,铜导电层、绝缘层和阻焊层厚度不断降低,对于一个双面FC-CSP基板,其成品板厚度约为130μm,未来将不断发展到110μm、80μm,甚至60μm的厚度。

无芯基板技术是进一步满足封装基板薄型化要求的一项重要先进技术

。

2、更优良的物理性能

由于封装和基板厚度的降低,因此要求基板材料具有

更好的平整性、尺寸稳定性和物理强度

等性能。

(1)更高的玻璃化温度。

高Tg的基板具有高耐热性,可以提高封装对高温回流焊的适用性、稳定性和反复性等。高Tg的基板还可以提高通孔的可靠性,使通孔在引线键合等具有热冲击、超声波作用的工艺中保持稳定的物理特性(如平整度、尺寸稳定性、弹性模量和硬度稳定性等)。

(2)更低的热膨胀系数。

降低基板的热膨胀系数,使其接近芯片的热膨胀系数,可以减小二者在互连过程中产生的热失配,从而降低封装翘曲及热应力。这是保证基板尺寸稳定性和微细线路封装精度并提高焊点可靠性的关键因素。

(3)高弹性模量。

提高基板在高温下的硬度和弹性模量,可以减小基板在引线键合或回流焊等高温工艺过程中的形变,保证焊接可靠性。对于薄型封装,更需要高弹性模量的基板,从而实现良好的微组装工艺性和可操作性。

(4)高耐吸湿性。

由于有机基板中的极性有机分子易吸附水分子,因此相较于陶瓷基板,有机基板在高湿条件下会吸收更多水分,严重时造成基板与芯片的界面剥离。因此,提高基板材料的耐吸湿性不仅可以改善封装的可靠性,还有利于增强基板耐金属离子迁移的性能。

(5)更优的电学性能。

有机基板的介电常数和介电损耗因子较陶瓷基板更低,因此有机基板更适合用于高频高速电路信号传输。为了保证封装器件优良的电源完整性和信号完整性,基板内的导体线路应具有更精确的线宽和间距控制,并采用低表面粗糙度的绝缘层和光滑的铜箔使导体具有更高的平整度。

此外,

柔性有机基板还应具有高挠曲性、无卤阻燃化等特性。化学稳定性、高散热性和环保“绿色”材料也是有机基板材料的发展方向

。

四、有机基板新技术与材料发展

近年来,为满足先进封装产品的要求,各种基板新工艺层出不穷。基板供应商围绕

提高材料性能、降低材料成本的方向,不断探索实现封装基板小型化、薄型化、高密度布线、高频高速信号传输

的解决方案。

以下,从有机基板关键制造工艺和新型基板技术方面进行介绍。

(一)有机基板关键制造工艺

1.金属线路制造工艺

随着焊盘节距的减小和I/O端口数的增加,对精细线路图形制造工艺的要求不断提高。

线宽/线距(L/S)是衡量封装基板制造领域技术能力的一项关键指标,基板产业研发的中长期目标是实现5μm/5μm的线宽/线距

,这给基板材料供应商带来了巨大的技术挑战。在这种发展趋势下,

选择合理的制造工艺来实现超低线宽/线距的目标,成为基板供应商的研发重点

。目前金属线路制造工艺主要包括以下几种,其工艺能力对比如图13所示。

图13 金属线路制造工艺的工艺能力对比

1)减成工艺

常规的封装基板加工采用减成工艺(Subtractive Process或Tenting Process),

减成工艺是在覆铜基材上贴一层感光抗蚀干膜(简称干膜)或涂覆一层液态感光抗蚀剂(简称湿膜),通过曝光、显影、刻蚀、脱模等一系列工艺,选择性地刻蚀掉非线路区域,最后形成导电图形的工艺

,其流程图如图14所示。减成工艺制造成本低,工艺成熟、稳定、可靠,适用于

大规模生产对线宽/线距要求不高(50μm/50μm以上)

的基板产品,目前应用十分广泛。

图14 减成工艺流程图

感光抗蚀层的分辨力

直接影响采用减成工艺所能实现的最小线宽/线距,分辨力和感光抗蚀层厚度密切相关。当光线通过感光抗蚀层时,会发生散射现象,感光抗蚀层厚度越大,散射现象越严重,通过感光形成的线路会存在更多误差。因此感光抗蚀层厚度越小,越容易感光实现精细布线。制造厚度低于20μm的干膜比较困难,而采用湿膜工艺虽然可以制造出5μm的膜厚,但湿膜过薄会有针孔、气泡、划伤等问题产生,此外湿膜的厚度均匀性不佳,短期内无法取代干膜。

减成工艺中的侧蚀现象是精细线路制造中难以解决的问题

。根据减成工艺中的光致刻蚀剂、曝光显影、刻蚀压力和刻蚀流体力学等因素的研究,以及采用真空刻蚀设备等方法,可以改善侧蚀问题。

然而,应用减成工艺制造的基板的线宽/线距

很难逾越20μm/20μm这一极限

。目前应用于SiP、叠层封装的基板的线宽/线距已经达到20μm/20μm以下,而应用于中央处理器、图形处理器、游戏处理器芯片封装的基板的线宽/线距则达到10μm/10μm,这些精细线路完全超出了传统减成工艺的加工能力。

2)加成工艺

加成(Additive Process)工艺完全不同于传统的减成工艺,其

采用没有覆铜箔的有机基材,通过化学镀工艺在绝缘基材上形成电路图形

。由于线路是最后在基材表面生成的,所以这种工艺被称为加成工艺,其流程图如图15所示。

加成工艺适用于超精细线路(线宽/线距可以达到3μm/3μm)的制造

,其特点是工艺步骤少、无须刻蚀铜箔、加工简单。化学镀得到的铜层分散能力较好,适于制造具有多层结构、孔径小的高密度基板。

图15 加成工艺流程图

但加成工艺对基材有特殊要求,与传统减成工艺在设备和制造成本上有很大差别,且化学镀铜的速率过慢,目前工艺成熟度还不高,可靠性水平也需要进一步提升,因此加成工艺在基板制造中仍没有得到广泛的应用。

3)半加成工艺

半加成工艺(Semi-Additive Process,SAP)是处在减成工艺和加成工艺之间的线路制造技术。半加成工艺引入了很多新思路,如无须布置导线即可进行图形电镀、采用差分法刻蚀等,其基本的工艺流程如图16(a)所示。

目前,半加成工艺已经发展得比较成熟,精细布线程度及可靠性水平都达到了高端基板产品的要求。在批量生产中,采用

半加成工艺制造线宽/线距在10μm/10μm~50μm/50μm之间的图形线路

,并通过控制电镀时间等参数灵活调节线路的厚度,对于高要求的阻抗线制造来说,是一种较好的工艺选择。

在半加成工艺(SAP)的基础上,出现了改进型半加成工艺(Modified Semiadditive Process,MSAP),MSAP的工艺流程如图16(b)所示。

图16 SAP与MSAP工艺流程图

SAP首先在绝缘基材表面上直接化学镀铜(厚度通常为0.5~1.0μm),以形成线路及孔内的导通层(种子层),然后用负像图形保护非线路区,并电镀出所需厚度的精细线路及通孔,最后将非线路区的化学镀铜层刻蚀去除

。

在采用SAP时,光线的散射不会对线路图形造成不良影响,感光抗蚀层厚度不需要过薄。由于SAP所需要刻蚀的金属层厚度很薄,通过快速刻蚀即可将基材上底层金属去除而基本不存在侧蚀问题,因此

SAP非常适合制造精细线路

。

在SAP中,线路往往与盲/通孔共镀,通常利用电镀实心铜柱进行填孔,这样可以避免孔洞问题,提高互连可靠性,并且非常适合叠孔和焊盘上的导通孔工艺,可以明显提升布线密度,减少信号盲区,因此

SAP被认为是制造先进封装有机基板的主流工艺

。目前,国际上高端基板制造厂商均采用SAP制造用于中央处理器、图形处理器、游戏处理器芯片封装的基板。

SAP工艺难点

主要如下。

(1)铜线条与低粗糙度树脂的表面结合力。

(2)盲孔内部化学镀铜覆盖的均匀性。

(3)叠孔之间的良好的连通性。

(4)导线之间的绝缘性等。

SAP与普通减成工艺具有较大的不同,需要选用特定的低粗糙度介质材料,并通过控制树脂表面的粗化、化学镀铜等来满足工艺要求。

MSAP采用2~3μm超薄铜箔作为种子层,再进行图形电镀,当电镀完成后将超薄铜箔刻蚀掉,形成细线路

。MSAP对覆铜基材上铜箔的厚度提出了较高要求。如果铜箔过厚,则需要大量减薄,可能导致面铜厚度不均;而薄铜箔的生产成本高,且其压板制造困难,容易在层压时产生褶皱。

MSAP可以保证线路与绝缘层的结合力,但是超薄铜箔的材质致密,其刻蚀速率比化学镀铜和电镀铜的刻蚀速率都低得多,在将薄铜箔刻蚀干净的同时图形电镀形成的线路会被刻蚀掉,线路精度变差。因此,在高精度线路尺寸控制方面,SAP仍优于MSAP。

SAP受材料限制较大,已商业化并

被广泛应用于半加成工艺的绝缘基材主要为ABF

。

ABF是一种在环氧树脂中加入玻璃微粉压合制成的片状半固化材料,其中不含玻纤

,用这种材料制造外层线路的绝缘层可以很好地实现SAP,ABF目前已经在高端基板制造中广泛应用。然而ABF是日本味之素精细化学公司的专利产品,其成本和售价都很高。

针对这一情况,

日本三菱瓦斯化学公司开发了PCF+BT(覆树脂铜箔与BT基半固化片连用)材料替代ABF

,采用这种材料的半加成工艺被称为PCF-SAP工艺。PCF是一种在低粗糙度铜箔表面涂覆一层树脂并固化后形成的带有固化树脂层的铜箔。在加工过程中首先将铜箔全部去除,使铜箔表面的粗糙度转移到树脂表面,由于树脂是特殊成分制成的,因此直接进行化学镀铜就可以得到很好的铜层结合力。PCF的使用可以大大降低SAP的材料成本。

4)埋线路工艺

埋线路工艺(Embedded Trace Substrate,ETS或Embedded Pattern Process,EPP)是一种制造精细线路的新方法,

适用线宽/线距小于12μm/12μm的线路,目前可达到5μm/5μm

。

首先在覆铜基材上使用很薄的光阻材料通过光刻、电镀制造精细线路,然后与半固化片压合,并进行激光钻孔和化学镀铜,接着通过光刻、电镀形成盲孔及第二层布线层,依次完成所有布线层制造后去除覆铜基材。

覆铜基材的选择具有多样性,可以在其两侧同时制造布线结构,提高生产效率。采用ETS制造的有机基板省去了芯板,更薄更轻;线路层埋入介电材料中使表面更平整;无须增加成本即可形成精细线路。由于这些优点,近年来ETS得到了各基板厂商的广泛应用,ETS基板结构如图17所示。

图17 ETS基板结构

表6对有机基板的几种主流线路制造工艺的优缺点进行了对比。

表6 主流线路制造工艺对比

2.图形转移技术

传统的图形转移技术使用照相底片对图形进行曝光转移,其技术成熟、设备价格低、厂商多,生产低密度基板效率较高,应用普遍。然而,照相底片尺寸受温度、湿度的影响很大,图像对位偏差较大,加之其他误差,因此传统图形转移技术的成像合格率低,加工流程长,已不能满足精细线路的制造要求。

激光直接成像(Laser Direct Image,LDI)技术

是一种常用的非接触式成像技术。其采用波长在350~410nm之间的UV光源所产生的激光束直接在光致抗蚀剂(干膜)上成像,然后通过显影等后续工艺实现线路的图形转移。LDI技术的优点如下。

1)对位精度高

传统图形转移技术存在底片涨缩导致的对位偏差问题,而LDI技术克服了这一缺陷。一方面,LDI技术采用激光定位实现基板中的层间对位,可以使对位精度和重复精度得到显著提升,从而提高产品质量与合格率;另一方面,LDI设备可以针对不同的板材调整不同预放比例,自动调整涨缩尺寸,因此图形的对位偏差可以控制在±5μm以内。

2)加工流程短

传统图形转移技术工艺复杂,需要八个以上的工艺步骤才能完成图形转移,而LDI技术工艺仅包括数据转移、激光扫描、显影、刻蚀四个步骤,大幅简化了加工流程,提升了效率。

3)成本低廉

LDI技术不需要照相底片、重氮片等耗材,不仅节省了材料费,还减少了对材料进行维护及保存的费用。

基于以上原因,

采用LDI技术实现电路图形的转移成为高密度精细线路制造的主要方法

。

3.微孔制造工艺