文章链接:https://pubs.acs.org/doi/10.1021/acs.nanolett.4c02586

摘要

实现稳健的电接触对将单层二维半导体(如半导体过渡金属二硫族化合物,s-TMDs)在电子学中的应用潜力变为现实至关重要。尽管近期取得了突破性进展,金属与s-TMDs接触的实验与理论理解之间仍存在差距。本研究探索了与单层MoSe2接触的铋半金属,采用了一个将实验不确定性降至最低的平台;我们结合了接触前端和接触末端的测量,测量了诸如比电阻(ρc)和转移长度(Lt)等关键参数。我们发现,由于电荷转移的影响,MoSe2在接触区域下的电阻率增加,这可以通过自洽方法进行建模。相反,基于第一性原理的层间电荷转移率计算与测得的ρc值不一致,这凸显了新的理论方法的必要性。

研究背景和主要内容

半导体过渡金属二硫属化物 (s-TMD) 已成为电子和光电子领域极具前景的材料并且由于卓越的静电栅极控制和改进的迁移率,在超薄极限下可能胜过硅。然而,实现单层 s-TMD 的低电阻接触仍然是一个重大挑战。最近的突破是采用了 Bi 和 Sb 等半金属,它们的低蒸发温度可以形成无损伤的范德华 (vdW) 界面,低态密度可以抑制金属诱导间隙态的形成。Bi 和 Sb 与 CVD 生长的 MoS2接触分别实现了 123 Ω·μm 和 42 Ω·μm 的 n 型接触电阻。然而,对接触的理论理解和实验之间仍然存在差距,并且其预测的性能极限尚未实现。

s-TMD 接触建模几乎完全考虑了金属接触应用于完美结晶的本征 s-TMD 层的理想情况。然而,实验已经在缺陷密度的系统中进行了源自底层 s-TMD(CVD 生长膜和合成晶体)的点缺陷密度通常在 10 13 cm –2 ) 以及金属蒸发造成的损坏。这些缺陷强烈改变了平面传输并引入了导致费米能级钉扎的间隙态,从而增加了接触电阻和传输长度。另一方面,带电缺陷可以引入掺杂,改善平面内和平面外的传输,从而改善接触电阻。因此,报告的接触电阻表现出很大的变化。由于接触会强烈扰动下方的 2D 半导体层,用于块体半导体的测量技术可能不适合表征金属–s-TMD 接触。这些因素使得很难“闭合”理论预测和实验验证之间的循环,从而揭示这些接触中内在的底层物理特性。

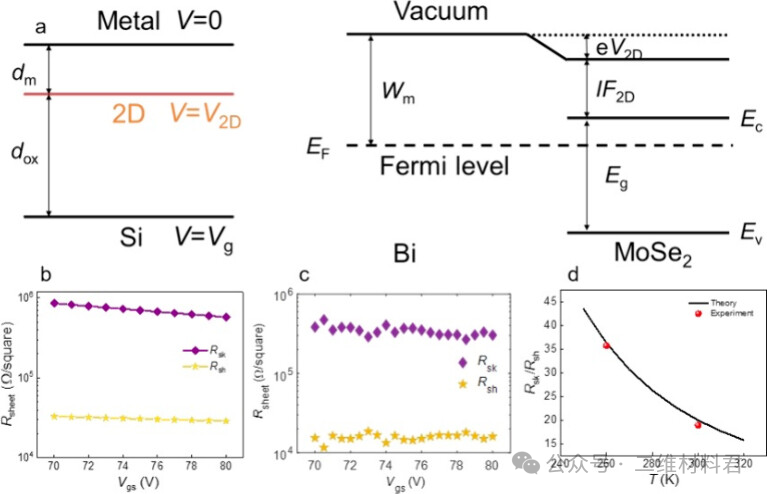

作为迈向“闭环”理解的第一步,我们在此结合先进的材料合成和设备组装,以创建能够最大程度减少上述无序和不确定性来源的设备。我们利用从高纯度块状晶体中剥离的单层 MoSe2,封装在六方氮化硼 (hBN) 薄片中以最大限度地减少外部无序,并使用温和工艺蒸发铋触点。我们使用扫描隧道显微镜 (STM) 验证低缺陷密度,并使用扫描透射电子显微镜 (STEM) 确认 Bi-MoSe2界面无损伤和无应变。我们使用多端测量表征 Bi-MoSe2接触,发现接触电阻率 ρc = (4-5) × 10 –6 Ω cm –2和传输长度L t ≈ 40 nm;后者通过研究接触长度缩放得到独立证实。接下来,我们寻求从理论上理解这些接触的两个关键方面。首先,接触下方的 MoSe2薄层电阻大约大 20 倍;这种增加及其随温度的变化可以用自洽电荷转移模型准确描述。其次,我们使用密度泛函理论计算跨结的电荷传输速率,并发现与测量的 ρ c值不一致的值。因此,我们可以得出结论,传统模型可以准确描述金属-s-TMD 接触中的电荷传输和能带排列,但不能准确描述电荷传输速率。

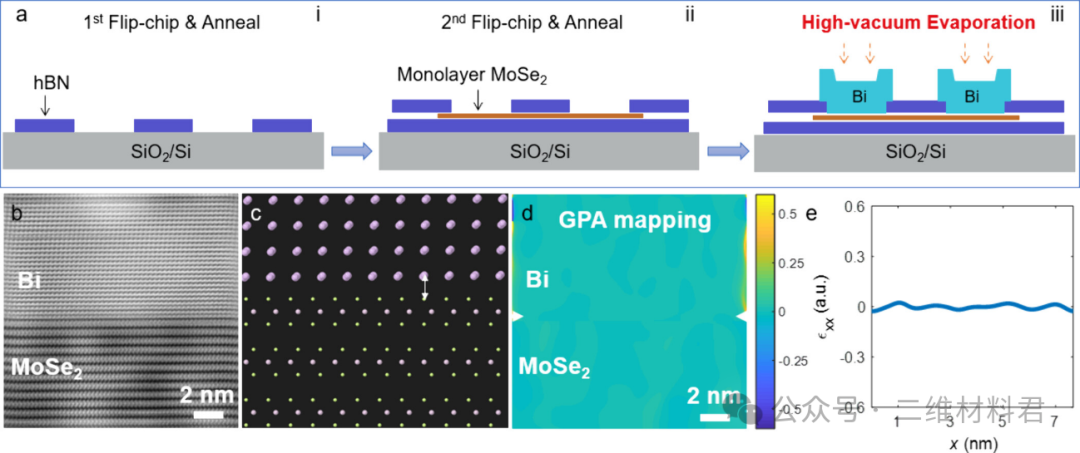

图 1. Bi-MoSe2界面的制造流程、原子分辨率成像和几何相分析。a 、Bi 接触图案化 hBN/单层MoSe2/hBN 的制造流程。b 、多层MoSe

2上 Bi 的原子分辨率图像。c 、模拟的 Bi–MoSe2异质结构。d 、b中所示横截面图像的几何相分析 (GPA) 映射。e 、沿 Bi–MoSe2界面的应变分布。

我们采用了“倒装芯片”工艺来组装异质结构。首先,我们确定了合适的(厚度约为 40 nm)顶部 hBN 薄片,并使用电子束光刻 (EBL) 和反应离子蚀刻 (RIE) 在薄片上蚀刻出所需宽度的狭缝。为了将原始底部表面向上暴露,我们“翻转”了图案化的 hBN,方法是使用聚合物拾取它,反转聚合物-hBN 堆叠,然后在高真空下退火以去除聚合物(图 1 ai)。接下来,我们使用第二片 hBN 拾取单层 MoSe2和蚀刻的 hBN;然后将组装的异质结构“翻转”并进行第二次退火(图 1 aii)。原子力显微镜 (AFM) 成像(补充图 2e)证实,缝隙宽度可以在纳米范围内变化,沿x和y方向具有高度均匀性,并且 MoSe2的表面在倒装芯片退火后是干净、无污染的表面。除了提供干净的界面之外,这种堆叠策略还通过将金属触点限制在 hBN 缝隙内来稳定金属触点;如果没有限制,窄的 Bi 触点在处理过程中很容易滑动(补充图 2f)。最后,我们使用 EBL 和高真空(10 –8 Torr)热蒸发来对 Bi 触点进行图案化(图 1 aiii)。制造细节在方法和补充图 2a-d中提供。

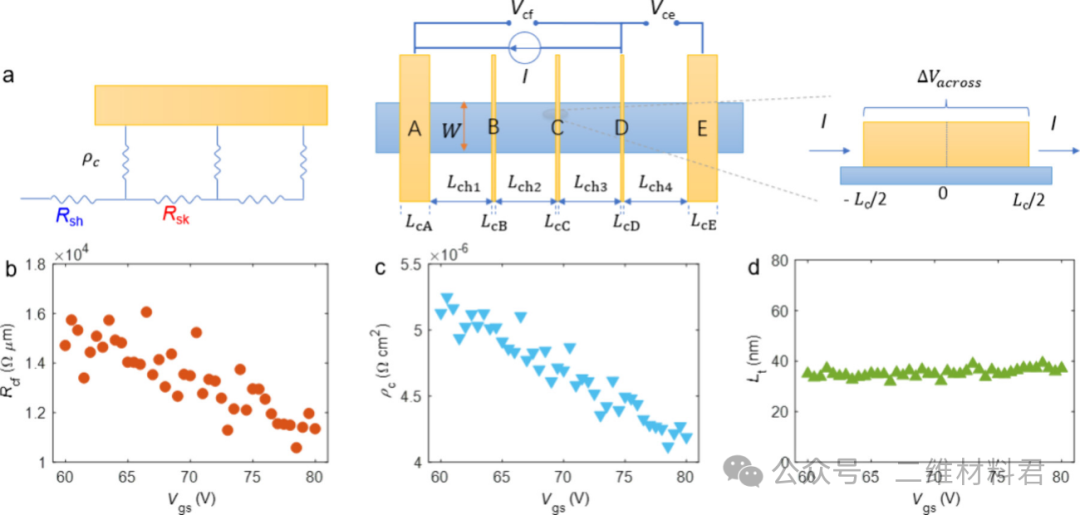

图 2. Bi–MoSe2触点的电气特性。a 、由触点前端和触点末端方法组成的测量配置示意图。左图显示触点的传输线模型,其中我们区分了触点下方和沟道内部的薄层电阻。中间图是特定的测量配置和特定的参数指定。触点 B 和 C 用作四探针电压测量引线。右图是电压探针 B 和 C 之间电压分布的横截面示意图。b – d 、触点前端电阻 ( R cf )、触点电阻率 (ρ c ) 和传输长度 ( L t ) 与V gs的关系。

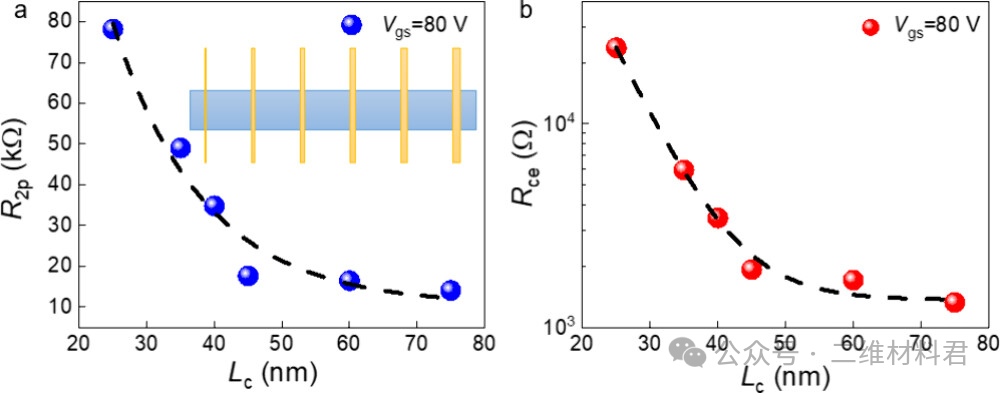

图 3。vdW 接触的长度缩放。a 、b、R 2p ( a ) 和R ce ( b )在V gs = 80 V时对Lc的依赖性。