文章链接:https://pubs.acs.org/doi/10.1021/acsnano.4c13295

亮点:

1.优化极性门设计:通过引入WSe2/MoS2异质结,实现了可重构n型和p型FET阈值电压匹配的突破。

2.锚定阈值电压:有效稳定阈值电压,降低了电路中不必要的功耗波动。

3.增强亚阈摆幅:减小亚阈区摆幅,实现了更敏锐的开关特性。

4.高性能反相器:设计并展示了具有优异噪声裕度和高增益的反相器,证明了其实际可行性。

5.多功能逻辑门:实现了多种逻辑门的可重构功能,包括NOR/NAND和XOR/XNOR,突显其多样性与灵活性。

摘要

可重构场效应晶体管(FET)的出现,为实现高效的可重构电路提供了一种创新方法,显著降低了硬件开销并提升了电路灵活性。然而,这些器件通常面临非对称传输曲线的问题,影响了逻辑门的性能和可靠性。本研究探讨了范德华结场效应晶体管(JFET)在可重构电路中的应用。通过WSe2/MoS2范德华集成异质结和优化的极性门设计,我们成功解决了n型和p型FET之间的阈值电压不匹配问题,同时实现了阈值电压的锚定和亚阈摆幅的降低。我们展示了具有该设计的可重构JFET互补反相器,其开关特性优异,转移曲线对称,功耗显著降低,噪声裕度达到96.3%,增益高达153.82。此外,研究还成功构建了具有对称曲线和尖锐切换特性的可重构NOR/NAND和XOR/XNOR逻辑门,突显了该方法的多功能性和有效性。这些成果表明,基于WSe2/MoS2的JFET在低功耗、高性能、可重构电子电路的发展中具有巨大潜力,特别是在CMOS框架内的应用。

研究背景和主要内容

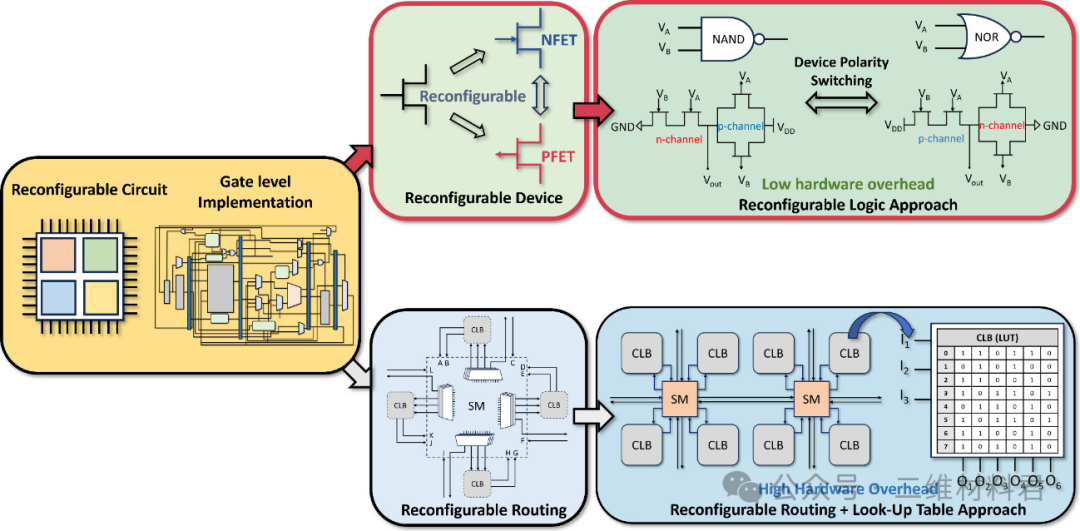

可重构电路在要求高通用性和频繁调制的系统中起着关键作用。这些电路已广泛应用于机器人、神经网络,识别系统,和安全。实现可重构电路的传统方法依赖于可重构路由与查找表(LUT)结合来模拟可编程逻辑结果。这种方法虽然有效,但硬件开销很大。可重构场效应晶体管 (RFET) 的出现为可重构电路的实现开辟了另一条道路。这一突破还促进了该领域的重大进步,例如二进制/三进制逻辑转换,硬件安全,和神经形态电路。利用极性可控器件,可以在器件级进行重构,并轻松实现可编程逻辑门。与传统的可重构布线方法相比,可重构设备方法的硬件开销明显更低,且具有更强的多功能性,如图1所示。

图 1. 可重构电路的重要性和可能的方法。可重构电路的传统实现利用交换矩阵作为可重构路由和查找表来实现可编程逻辑。使用可重构设备,可以轻松实现可编程逻辑门。与可重构路由方法相比,可重构设备方法的硬件开销明显更低,通用性更强。

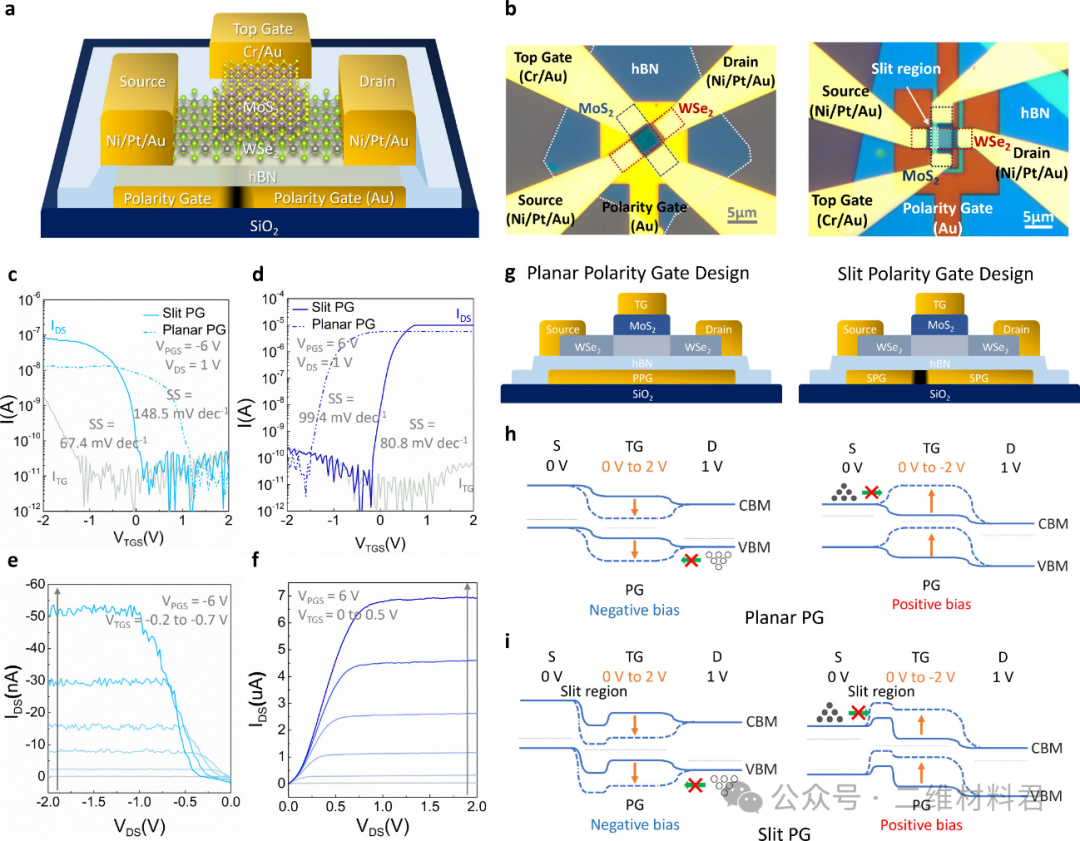

图 2. 可重构 WSe2 /MoS2 JFET 及其I

– V特性。 (a) WSe2 /MoS2 JFET的 3D 横截面示意图和 (b) 光学图像。 (c) WSe2 /MoS2 JFET 在 p 沟道模式和 (d) n 沟道模式下的I DS - V TGS传输特性。 (e) WSe2/MoS2 JFET 在 p 沟道模式和 (f) n 沟道模式下的I DS - V DS输出特性。 (g) 横截面示意图,说明两种极性栅极设计之间的差异。 (h) WSe2 /MoS2 JFET 在平面极性栅极设计和 (i) 狭缝极性栅极设计下的预期能带图。

通常,JFET 是耗尽型器件,在零V TG时导电。为了降低功耗,我们在 WSe 2通道和 MoS 2 TG 的重叠区域下方引入了一个狭缝区域,这会在 WSe2沟道中产生不受控制的本征区域。图2g 说明了本研究中研究的不同 PG 设计。图2c、d 中的虚线和实线显示了 PPG 设计与 SPG 设计之间的传输特性差异。通过引入狭缝区域,可以在不影响导通电流的情况下调整器件的Vth。图 2i说明了 SPG 器件的功能。当V PGS负偏置时,WSe2沟道变为 p 掺杂,但狭缝区域除外,它保持本征。当V TGS = +2 V 时,与 PPG 配置类似,反向偏置的 p-n 结会耗尽通道,从而有效关闭器件。当V TGS = 0 V时,在 PPG 设计中,V DS产生的横向电场会诱导空穴从漏极流向源极。然而,在 SPG 设计中,沟道中的本征区在价带中产生了额外的势垒,阻止空穴通过。因此, I DS受到狭缝区域中低载流子密度的限制,即使沟道未完全耗尽也保持在低水平,从而形成自然“关闭”的器件。当V TGS从 0 V 转变为 −2 V 时,沟道本征区和 p 掺杂区的电位都会升高,从而消除了势垒而不会影响导通电流。同样,n 沟道模式器件也受益于额外的势垒,导致V th锚定在 0 V 附近同时保持高导通电流。此外,通过使用 SPG,p 沟道器件的 SS 从 148.5 mV/dec 提高到 67.4 mV/dec,而 n 沟道器件的 SS 从 99.4 mV/dec 提高到 80.8 mV/dec。这种改善归因于本征区域载流子浓度可调性的增强。对 SPG 器件进行了开尔文探针力显微镜 (KPFM) 测量,结果如图S4所示。测量证实了 WSe 2通道中的额外势垒,狭缝区域的电位明显增加。而 MoS 2尽管可以掩盖 SPG 对沟道电位的部分影响,但数据仍然可以更清楚地了解能带分布。表 1总结了我们的 JFET 的关键参数,并与以前关于基于 vdW 结的晶体管的报道进行了比较。所提出的器件显示出出色的开关性能,并且 vdW p-JFET 的 SS 创下了历史新低。此外,两个器件的V th均保持在 0 V,这相对于以前的研究来说是一个重大进步。图2e 和图2f 分别显示了在 p 沟道和 n 沟道模式下工作的WSe2 /MoS2 JFET 的I DS - V DS输出特性。该器件表现出典型的 FET 特性,由于沟道夹断,在较大的V DS下会发生电流饱和。

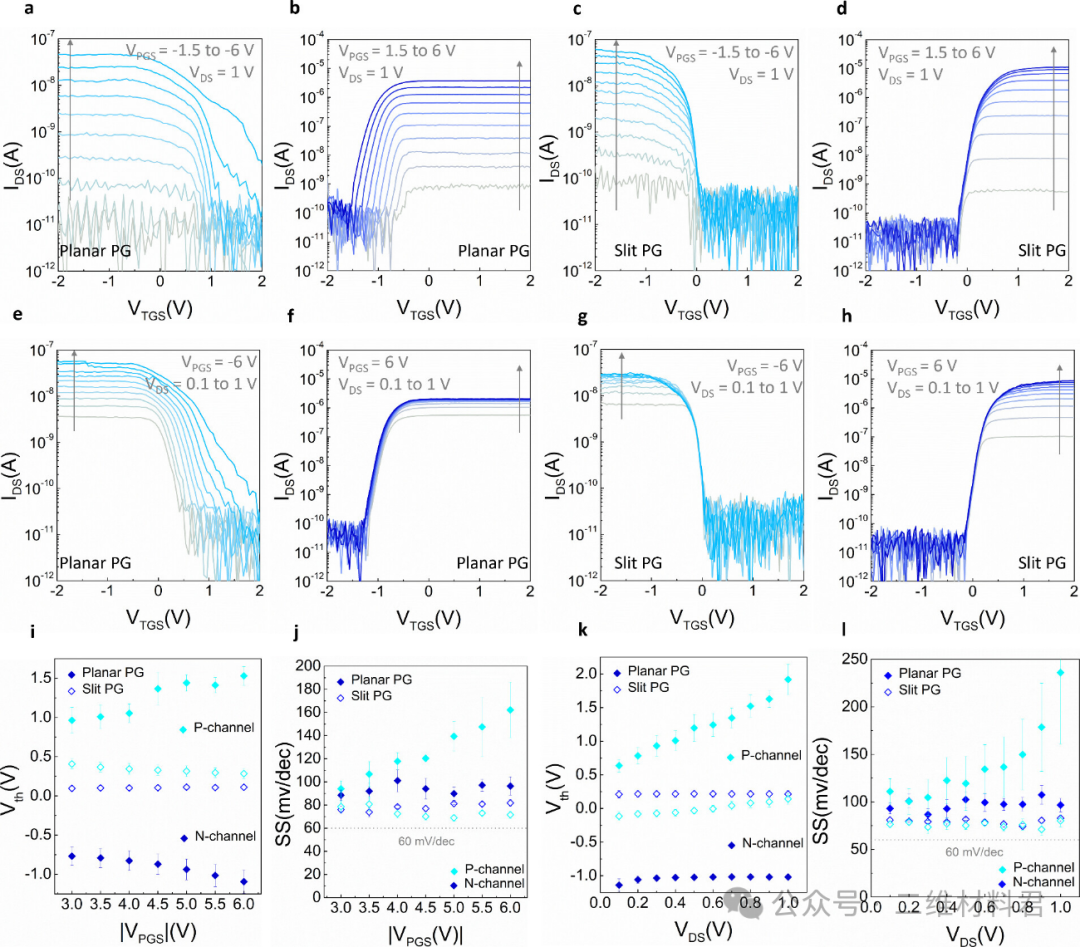

图 3. PPG- 和 SPG-WSe2/MoS2 JFET 的性能比较。 (a)在 p 沟道模式和 (b) n 沟道模式下,采用平面极性栅极设计且偏置于不同 VPGS 的 IDS - VTGS 转移特性。( c )在p沟道模式和 (d) n 沟道模式下,采用狭缝极性栅极设计且偏置于不同