来源:本文由半导体行业观察翻译

,谢谢。

凭借FD-SOI的特性,对于广泛的市场领域,半导体生态系统的主要参与者对该技术越来越感兴趣。

全耗尽型绝缘层上硅(FD-SOI)是将CMOS晶体管的两个实质特性汇集在一起的独特技术:2D平面晶体管结构和全耗尽型工作特点。它依赖于独特的基板,该基板的层厚度受到原子尺度的控制。

FD-SOI具有卓越的晶体管性能,具有先进CMOS技术中的最佳功率、性能、面积和成本折衷。此外,FD-SOI还有许多其他独特的优势,包括后向偏置(负偏压)能力,良好的晶体管匹配,临近阈值供应能力,超低的辐射灵敏度和非常高的本征晶体管速度,允许其处理毫米波(mmWave)频率。

所有这些关键特性正逐渐驱动FD-SOI从理论上走向实际的应用,包括智能手机的入门级应用处理器,用于自动驾驶和IoT的片上系统(SoC)设备,以及所有毫米波应用,如5G收发器和汽车电子雷达系统。

多个代工厂和IDM为FD-SOI技术提供支持,现在,全面技术产品已经可用于28nm和22nm节点,并且在65nm和12nm节点开始出现。随着FD-SOI全球生态系统的发展成熟,该技术可以为多元化市场的应用开发做好准备。

FD-SOI衬底有几个显著特点,使其具有独特的优势。本文总结了支持FD-SOI广泛实施的全球生态系统建设的最新进展和各种要素,以及最受益的应用。

FD-SOI技术的核心

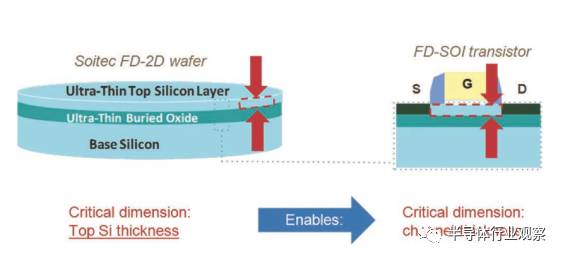

FD-SOI技术中的一切都以基板为基础,如图1所示,基板直接决定了晶体管结构。晶体管要想达到完全耗尽的工作状态,器件沟道的顶部硅层的厚度是真正的挑战,其厚度目标通常为大约60埃或11个原子层。考虑到在器件制造过程中硅材料的消耗,铸造厂通常需要120埃的顶级硅。均匀性是保持晶体管具有尽可能低的可变性的另一项非常具有挑战性的规范。通常认为+/- 5埃或1个原子层的均匀性是至关重要的。 氧化埋层(BOx)厚度也必须非常薄,大约20nm,以使晶体管沟道中的静电控制由于接地平面效应而最大化。

图1:晶体管沟道厚度直接与顶层硅SOI层定义相关

制造一种300mm的晶体硅,要求厚度规格低至10-12个原子层,这虽然困难但还是可以理解。10年前,这听起来是不可实现的,因此人们研究其他途径以便使能完全耗尽的晶体管。但现在这是有可能实现的。

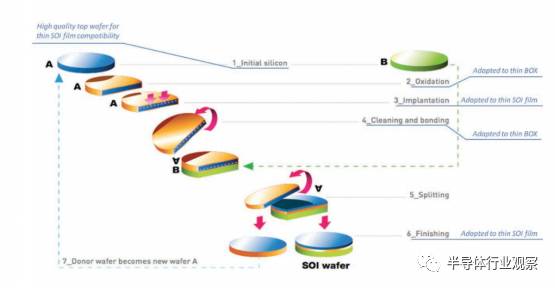

半导体的制造依赖于众所周知的智能切割(Smart Cut)工艺(如图2)。晶圆A首先进行氧化,然后进行大剂量离子注入,从而在表面下方产生弱化层。在仔细的清洁步骤之后,晶圆A通过分子键合技术与晶圆B结合,然后在晶圆A的弱化区域的精确位置处诱导分裂。

最后,对所形成的SOI晶圆进行其他平滑处理以达到目标厚度规格。值得注意的是,高质量的晶圆A可以回收,以便进一步重用,这使得Smart Cut成为SOI制造最具成本效益的解决方案。

图2:Smart Cut工艺及其在FD-SOI技术中的适用性

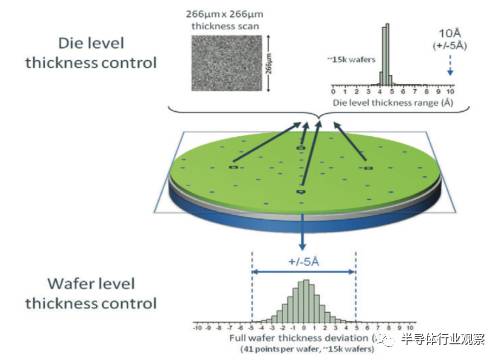

FD-SOI基板制造工艺现已完全成熟。特别地,如图3所示,从晶体管到晶圆的所有级别的厚度均匀性都得到了非常好的控制,这确保了晶体管可变性维持在非常低的水平。

图3:FD-SOI制程中从die到晶圆的全部级别的厚度得到了很好的控制

少即是多

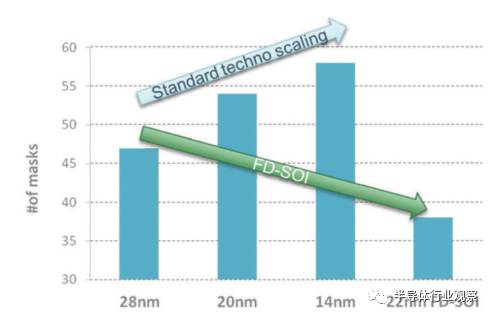

在28nm节点以下的硅中获得更多性能的方式增加了制造过程的复杂性。因此,如图4所示,节点越小,越需要掩模更多来创建芯片。这增加了制造成本以及其他非循环的工程成本,包括设计流程、设计验证、掩模套件等。

图4:每个技术节点所需的掩模数量

另一方面,从制程的角度看,FD-SOI是一种简单的技术。事实上,它在提供更多的性能的同时,降低了制造过程的复杂性。大多数沟道工程实际上都是直接在衬底上完成的,正如许多代工厂所报道的那样,FD-SOI比bulk silicon更容易实现。

下一级别的晶体管性能

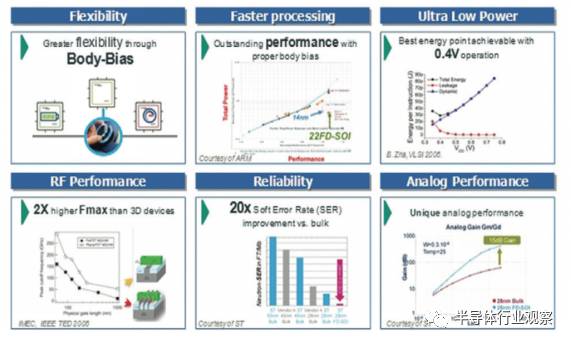

除了制程简单之外,FD-SOI还具有其他显著的优点,如图5所示。

图5:使用FD-SOI技术的优势

1、body-bias所带来的更好的设计灵活性

FD-SOI的薄氧化埋层(BOx)不仅增强了沟道的静电控制,而且还可以通过负偏压获得对阈值电压的完全调节。FD-SOI晶体管无需沟道掺杂,也就避免了复杂的电压调整技术。它还可以通过背栅极极化简单地实现低、中、高电压控制。薄BOx的行为就像一个真正的第二个门,最重要的是它可以动态使用。

这意味着相同的功能块可以根据需要在高功率或低功率下工作。后向偏置(负偏压)的电位非常大:关键路径改进的选择性body bias,过程变化补偿和可靠性漂移补偿。全反向偏置是一个非常独特的功能,它只能在薄BOx技术上实现SOI。

2、功率—性能—面积—成本的折衷:所有平面技术中最佳的PPAC(power-performance-area-cost)方案。

由于FD-SOI制程更为简单,能够更好地控制随机失配,最小化结漏电和寄生电容,通过完全耗尽的晶体管操作增强静电控制和调节体偏置(body bias)的可能性,FD-SOI技术呈现出最佳的PPAC。

3、近阈值电源电压带来的超低功耗

几乎所有的CMOS技术都能实现最佳的能源效率——即实现每个功能的最低能量,而不管频率如何——在大约0.4 V电源电压下,通常被称为Vdd 。 在这种电源电压下,可变性的管理是一个真正的挑战。

由于body bias和其固有的低可变性特性,FD-SOI可以实现非常低的电源电压。通常来说,降低电源电压(尽管不一定低至0.4V)的能力对于许多应用来说是很困难的,在这些应用中,与性能相比,功耗是更大的挑战。 考虑到动态功率随着Vdd2的增长而增长,像FD-SOI这样的技术能够通过显著降低电源电压从而大大节省功率,这是一个独特的优势。

4、最佳RF-CMOS技术,几乎2倍于3D设备的最大频率

由于成本和功耗的原因,将尽可能多的模拟/ RF功能集成到单个RF-CMOS硅平台中,这在许多市场中成为日益重要的问题。然而,RF-CMOS平台的一个限制是增加频率的能力有限,特别是在毫米波频谱(30 GHz及以上)中。

这对于诸如FinFET这样的3D器件来说是更大的问题,由于3D结构,它们必须承载非常强的寄生电容。因此,SiGe-双极平台通常用于该频率范围。FD-SOI是一种平面技术,因此不受3D器件特性的限制。325-350 GHz范围内的Ft / Fmax 已经有所报道,这使得全面使用高达100 GHz的毫米波频谱成为可能,并在许多应用中为FD-SOI、RF-CMOS平台带来光明的未来。

5、可靠性增强

通常,随着技术的缩减,模拟设计师必须使他们的设计能够与越来越多的退化晶体管一起工作。同时满足速度、噪音、功率、泄漏和可变性要求是一项越来越具有挑战性的任务。FD-SOI技术提供具有改进的匹配、增益和寄生的晶体管,可以大大简化器件设计。此外,其负偏压特性在许多新模拟结构的设计方面有巨大潜力。

代工厂中FD-SOI的使用正在增长

FD-SOI最先进的一些工作已经在全球半导体代工厂完成。

意法半导体(STMicroelectronics)在2012年就已经采用了FD-SOI技术,并启动了几个项目。 该公司在28nm FD-SOI技术上展示了基于ARM的3 GHz 以上工作频率的智能手机应用处理器。该技术现在在意法半导体用于多元化市场。

2014年,三星宣布采用FD-SOI技术进行多项试产,到2016年达到大规模产量化,最近他们公布了第一个产品。

在2015年,GLOBALFOUNDRIES(格罗方德)开发了一种名为22FDX的22nm FD-SOI技术,其定位是能够提供最佳性能/成本比。这种FD-SOI技术平台的性能接近16nm / 14nm FinFET,成本接近28nm bulk silicon工艺。

2017年2月,GLOBALFOUNDRIES和Dream Chip Technologies发布了第一个商业产品。 GLOBALFOUNDRIES的技术现在几乎完全合格,预计今年产量将有大幅增长。

在亚洲,中国代工厂华利(Huali)公司已经宣布欲将22nm FD-SOI技术纳入其fab2计划中,为中国市场提供更多的FD-SOI技术。

在日本,Renesas在FD-SOI方面的经验主要是一项功耗非常低的FD-SOI技术,称为薄氧化埋层上覆硅(SOTB)技术,面向低功率MCU市场。该技术得到了LEAP((Low-Power Electronics Association and Project)计划的支持,在65nm范围已经可以使用了。据Renesas报道称,这个平台的功耗非常低,相当于使用bulk silicon技术的十分之一。

IP / CAD状态和路线图

设计生态系统已经为28nm FD-SOI建立了完整的数据库和基础IP,同时,22nm技术也快速成长。EDA公司正在着手于将IP移植到FD-SOI的开发中。

2016年9月,GLOBALFOUNDRIES宣布推出新的合作伙伴计划,称为FDX celerator,以提供22FDX SoC设计并缩短上市时间,包括Synopsys,Cadence,INVECAS,VeriSilicon,CEA-Leti,Dream Chip和Encore Semi。2016年12月,该公司宣布增加八个新合作伙伴,其日益增长的FDXcelerator计划包括Advanced Semiconductor Engineering(ASE Group),Amkor Technology,Infosys,Mentor Graphics,Rambus,Sasken,Sonics和Quick Logic

对于技术路线图,FD-SOI可用于65nm至12nm的技术节点,可见度可低至7nm。基于其22FDX产品的成功,2016年,GLOBALFOUNDRIES推出了新的12nm FD-SOI半导体技术,称为“12FDX”。保持完全耗尽的平面处理技术允许代工厂利用低的寄生电容,避免等效3D晶体管所需的复杂光刻步骤,并利用负偏压来提升晶体管性能,特别是在低电源电压条件下。客户产品预计将于2017年底开始销售。

15年前FD-SOI技术的先驱Leti与GLOBALFOUNDRIES在22FDX和12FDX平台上合作。该组织最近开发了10nm FD-SOI技术的测试设备,并基于FD-SOI生产了10nm和7nm的模型。 Leti坚信FD-SOI可以缩小到7nm。

三星和GLOBALFOUNDRIES计划在2018年之前将非易失性存储器集成到其FD-SOI技术平台中。

由于FD-SOI生态系统的日益成熟,众多应用通过FD-SOI看到强大的差异化可能性。这些应用包括入门级移动通信的单芯片解决方案,通用应用处理器,图像信号处理器,机顶盒SoC,嵌入式计算机视觉,微控制器,混合信号应用如收发器,GPS /卫星接收机, WiFi / BT组合和毫米波雷达系统。

所有这些应用的功率预算通常非常有限,因此必须做好功耗与性能目标的权衡。这样的例子可以在诸如ADAS这样的嵌入式计算应用中找到,设计人员必须不断地权衡,找到妥协点,从而以非常有限的功率预算(通常约3W)实现所需的性能。对于所有嵌入式计算应用,FD-SOI及其在非常低的电源电压下运行的能力正在成为参考技术的动力

此外,RF /模拟集成通常是这些应用的关键。在同一硅芯片(die)上提供最佳的RF-CMOS技术是FD-SOI的独特优势。它为覆盖广泛功能的单芯片解决方案开辟了可能性。这在入门级市场中尤其有利,例如低端移动市场,价格压力如此之大,因此集成度必须推向极限,或者在包括雷达和5G收发器在内的毫米波应用中,其中的毫米波 RF功能可以集成在与计算功能相同的芯片(die)上。

新一批的突破性产品

基于FD-SOI技术的产品名单以非常快的速度增长,在过去几个月内有多个产品发布了公告。

2016年9月,Huami(小米的一个合作伙伴)推出了一款新的健身智能手表,其中包括基于FD-SOI的全球定位系统(GPS)芯片,图6演示了节能记录。该芯片允许手表在GPS打开的情况下达到35小时的电池寿命,比现在类似设备高出两到五倍,这么长的工作时间在业内可以说是无出其右的。该芯片于2016年2月在旧金山国际固态电路会议(International Solid- State Circuits Conference ,ISSCC)上发布,大大降低了电力使用量,为智能手表、智能手机、无人机和IoT的大量设备打开了永远在线的GPS应用的大门。

另外在2016年,Mobileye在其网站上公布,其下一代专门用于3级自动驾驶的EyeQ4产品系列也将基于FD-SOI技术,如图7。

图6:Huami Amazfit智能手表,内置基于FD-SOI的GPS

图7:专用于ADAS自动3级应的Mobileye EyeQ4芯片

2017年3月,NXP发布了基于三星28FDS FD-SOI技术的两个通用处理器系列(i.MX7ULP和i.M8X),用于超低功耗和丰富的图形的电池供电应用中(参见NXP路线图8)。针对i.MX7ULP产品,NXP报告称只需15μW或更低的深度睡眠暂停功耗,与以前的低功耗散装器件(bulk devices)相比降低了17倍,而动态功率效率提高了50%。这种高性能、低功耗的解决方案为开发IoT、家庭控制、可穿戴和其他应用程序的客户进行了优化,这些应用程序在待机模式下花费大量时间,并且需要特殊图形处理的短暂的性能强烈的活动。

图8:i.MX处理器路线图(由NXP提供)

2017年3月,Eutelsat Communications和意法半导体宣布推出新一代交互式应用SoC,降低了互通卫星终端的总体成本,同时降低了功耗。

在22nm方面,Dream Chip宣布推出业界首款用于汽车计算机视觉应用的ADAS SoC的22nm FD-SOI产品。SoC设备(如图9)提供了高性能的图像采集和处理能力,并支持卷积神经网络(CNN)视觉工作负载,以满足对复杂汽车对象检测和处理的需求。

图9:Dream Chip技术的第一代专用于ADAS的22nm FD-SOI产品

随着技术的不断发展,22nm FD-SOI产品系列预计将在明年迎来大幅度增长。

建造更多晶圆厂以满足FD-SOI的整体需求

面对FD-SOI日益增长的利润,特别是在中国,代工厂正在努力扩大足够的生产能力。2017年2月,GLOBALFOUNDRIES宣布计划到2020年将其位于Dresden的Fab 1工厂的产能扩大40%。Dresden将继续成为FDX技术开发的中心。

在中国,GLOBALFOUNDRIES和成都已宣布合资建造晶圆厂。他们计划建造一个300mm晶圆厂,一方面支持中国半导体市场的发展,同时满足全球客户对22FDX的需求。该晶圆厂将于2018年开始生产主流工艺技术,然后专注于制造GLOBALFOUNDRIES的商业化的22FDX工艺技术,预计将从2019年开始量产。

有了这两个公告,GLOBALFOUNDRIES每年将拥有超过200万个FD-SOI晶圆的产能。

关于FD-SOI基板的制造能力,Soitec在法国拥有一个300mm晶圆厂,在新加坡拥有另一个晶圆厂(目前处于待机模式),每年的全球产能为150万片(用于制造FD-SOI和其他新兴SOI产品)。该公司计划超越此范围,以满足客户的更多需求。

结论

业界对FD-SOI日益增长的兴趣,反映了今天半导体技术的新范式。客户的需求是以大幅度降低的功耗获得更强的计算能力,而这需要通过增强的模拟/RF集成来实现。凭借FD-SOI的特性,对于广泛的市场,特别是嵌入式计算应用市场,半导体生态系统主要参与者对FD-SOI越来越感兴趣。FD-SOI现在是主流技术,设备设计者正在利用主要的竞争优势。

致谢

作者衷心感谢Soitec团队(Christophe Maleville,Bich-Yen Nguyen,Thomas Piliszczuk,Alexandra Givert和Camille Dufour)的宝贵贡献和建设性的讨论。

今天是《半导体行业观察》为您分享的第1294期内容,欢迎关注。

关注微信公众号

半导体行业观察

,后台回复关键词获取更多内容

回复

科普

,看《第三代半导体科普,国产任重道远》

回复

争霸

,看《晶圆代工争霸战四部曲(了解各晶圆厂的前世今生,非常详细!建议收藏!) 》

回复

指南

,看《半导体专业留学海外指南(1): 专业方向选择》

回复

财报

,看《18家半导体企业财报汇总,几家欢喜几家愁》

回复

国产手机

,看《谨以此文献给国产手机背后的劳动者》

回复

指纹

,看《面板厂将指纹识别芯片革命到底 》

回复

OLED

,看《一文看懂我国OLED全产业链,除了京东方还有啥值得骄傲的?》

回复

缺货

,看《半导体行业缺货危机重现 这10大领域面临洗牌?》

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“半导体行业观察icbank”微信公众号。谢谢合作!

【关于征稿】:欢迎半导体精英投稿(包括翻译、整理),一经录用将署名刊登,红包重谢!签约成为专栏专家更有千元稿费!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号 MooreRen001或发邮件到 [email protected]

【关于征稿】:欢迎半导体精英投稿(包括翻译、整理),一经录用将署名刊登,红包重谢!签约成为专栏专家更有千元稿费!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号 MooreRen001或发邮件到 [email protected]

点击阅读原文加入摩尔精英