版权声明:本文来自《新电子》和《digitimes》

,

如您觉得不合适,请与我们联系,谢谢。

研究机构

YoleDeveloppement

发表最新研究报告指出,由于终端应用对芯片功能整合的需求持续增加,

SiP

封装将越来越受到欢迎,进而威胁

Fan-In

封装未来的发展前景。该机构已经将

2015

~

2021

年

Fan-In

封装出货量的复合年增率

(CAGR)

预估由

9%

下修到

6%

。

Yole

进一步分析,目前

Fan-In

封装仍是最低成本、最适合用来实现封装微型化的技术选择,因此广获智慧型手机、平板电脑等行动装置芯片采用。截至目前为止,约九成的

Fan-In

芯片都是应用在手机和平板装置上。然而,随着终端应用制造商更青睐在单一封装内整合更多功能的元件,未来有许多原本独立封装的元件都会改用

SiP

封装,

Fan-In

封装的发展前景势必会受到影响。其中,电源管理、射频元件改用

SiP

封装的趋势将最为明显。

苹果支持的

SIP

封装

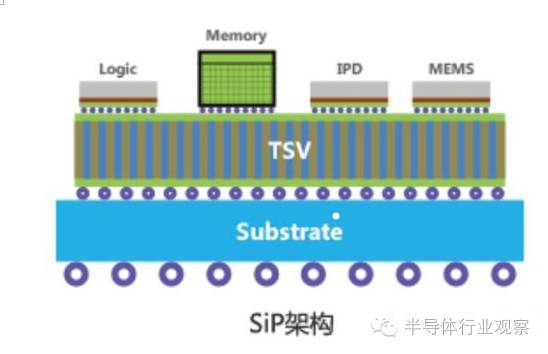

根据国际半导体路线组织(

ITRS

)的定义:

SiP

为将多个具有不同功能的有源电子元件与可选无源器件,以及诸如

MEMS

或者光学器件等其他器件优先组装到一起,实现一定功能的单个标准封装件,形成一个系统或者子系统。

从架构上来讲,

SiP

是将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能。与

SOC

(片上系统)相对应。不同的是系统级封装是采用不同芯片进行并排或叠加的封装方式,而

SOC

则是高度集成的芯片产品。

近年来,消费者对产品设计、外观美学要求提升,却同时也要求产品的附加功能设计越来越多,要达到不增加产品体积同时兼具相同的功能与设计,对产品开发人员来说并不件容易的事情,这时透过集成电路系统封装水准整合的

SiP(System in Package)

系统封装技术,正可将不同用途的集成电路芯片以集成电路封装手段进行整合,不仅可以将原有的电子电路减少

70%~80%

以上,整体硬件平台的运行功耗也会因为

PCB

电路板缩小而减少,而在产品整体功耗表现、体积等条件获得改善,甚至达到较前代产品更优异的设计成果。

近年来,消费者对产品设计、外观美学要求提升,却同时也要求产品的附加功能设计越来越多,要达到不增加产品体积同时兼具相同的功能与设计,对产品开发人员来说并不件容易的事情,这时透过集成电路系统封装水准整合的

SiP(System in Package)

系统封装技术,正可将不同用途的集成电路芯片以集成电路封装手段进行整合,不仅可以将原有的电子电路减少

70%~80%

以上,整体硬件平台的运行功耗也会因为

PCB

电路板缩小而减少,而在产品整体功耗表现、体积等条件获得改善,甚至达到较前代产品更优异的设计成果。

系统封装

(SiP)

技术在现有集成电路工程并非高困难度的制程,因为各种功能芯片利用集成电路封装技术整合,除考量封装体的散热处理外,功能芯片组构可以将原本离散的功能设计或元件,整合在单一芯片,不仅可以避免设计方案被抄袭复制,也能透过多功能芯片整合的优势让最终产品更具市场竞争力,尤其在产品的体积、功耗与成本上都能因为

SiP

技术而获得改善。

SiP

元器件若设计规划得当,已可相当于一系统载板的相关功能芯片、电路的总和,而依据不同的功能芯片进行系统封装,可以采简单的

Side by Side

芯片布局,也可利用相对更复杂的多芯片模组

MCM(Multi-chip Module)

技术、多芯片封装

MCP(Multi-chip Package)

技术、芯片堆叠

(Stack Die)

、

PoP(Packageon Package)

、

PiP(Package in Package)

等不同难度与制作方式进行系统组构。也就是说,在单一个封装体内不只可运用多个芯片进行系统功能建构,甚至还可将包含前述不同类型器件、被动元件、电路芯片、功能模组封装进行堆叠,透过内部连线或是更复杂的

3D IC

技术整合,构建成更为复杂的、完整的

SiP

系统功能。

而在

SiP

整合封装中,关键的技术就在于

SiP

封装体中的芯片或功能模组的芯片内互连技术

(Interconnection)

,在一般简单形式或是对芯片体积要求不高的方案中,运用打线接合

(Wire Bonding)

即可满足多数需求,而打线接合形式芯片多用

Side by Side

并列布局为主,当功能芯片数量多时,芯片的占位面积就会增加,而若要达到

SiP

封装体再积极微缩设计,就可改用技术层次更高的覆晶技术

(Flip Chip)

或是

Flip Chip

再搭配打线接合与

IC

载板

(Substrate)

之间进行互连。

基本上堆叠芯片

(Stack Die)

的作法在上层的芯片或模块仍然需要透过打线接合进行连接,但若碰到

SiP

的整合芯片、功能模块数量较多时,即堆叠的芯片、功能模组数量增加,这会导致越是设于

SiP

结构上层的芯片、模块所需要的打线连接电子线路长度将因此增长,传输线路拉长对于高时脉运作的功能模块会产生线路杂讯或是影响了整体系统效能;至于

SiP

在结构上为了预留

Wire Bonding

的打线空间,对芯片与芯片或是功能模块与功能模块间插入的

Interposer

处理,也会因为这些必要程序导致

SiP

最终封装成品的厚度增加。

随着

IC

集成电路制造、封装技术不断演进,芯片或功能模块的裸晶本身制程,已从微米制程升级至奈米等级,这代表单一个功能芯片或功能模块可以越做越小,也代表

SiP

的功能可因而得到倍数的成长,甚至还能游刃有余地维持相同的封装体尺寸。

也是拜半导体科技进步之赐,单一芯片功能在效能、体积、功耗表现的持续优化,也同时提升了芯片的

SoC(System on Chip)

整合能力。但

SoC

在面对微缩、异质核心

(Heterogeneous)

整合、产品快速更迭版本/功能等要求越来越高下,也让制程相对单纯、更利于多芯片整合的

SiP

制程技术抬头,让

SiP

在更多发展场域有其发展优势与条件。

晶圆级封装的另一条路:

Fan-In

大家都知道,今年苹果

A10

上用了台积电的晶圆级封装

(WaferLevel Package, WLP)

技术

Fan-Out

,并让这个技术成为行业关注的热点。其实还有另一个方向

Fan-In

。

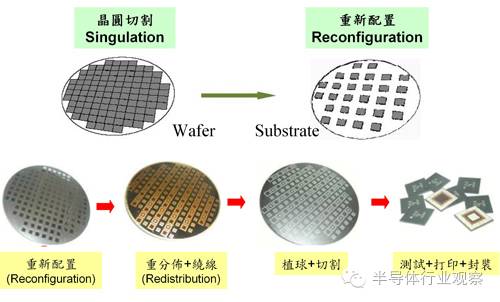

理论上,传统的

WLP

多采用

Fan-in

型态,应用于低接脚

(Pin)

数的

IC

。但伴随

IC

讯号输出接脚数目增加,对锡球间距

(Ball Pitch)

的要求趋于严格,加上印刷电路板

(PCB)

构装对于

IC

封装后尺寸以及讯号输出接脚位置的调整需求,因此变化衍生出扩散型

(Fan-out)

与

Fan-in

加

Fan-out

等各式新型

WLP

封装型态,其制程甚至跳脱传统

WLP

封装概念,如英飞凌于

2006

年

SEMICON Europe

即提出新型态的

Fan-out WLP

封装技术

(

下图

)

。

英飞凌扩散型晶圆级封装制造流程

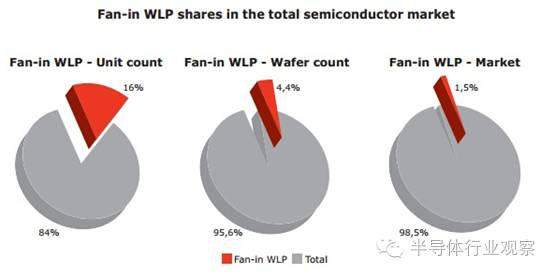

扇入型晶圆级封装(

Fan-in WaferLevel Packaging, FIWLP

)是一项非常重要的封装技术,在成本和尺寸方面具有无法比拟的优势。如下图所示,

FIWLP

占整个封装出货量的

16%

、晶圆出货量的

4.4%

,而在整个半导体市场营收中仅占

1.5%

。

扇入型晶圆级封装在整个半导体市场中的份额

扇入型晶圆级封装在整个半导体市场中的份额

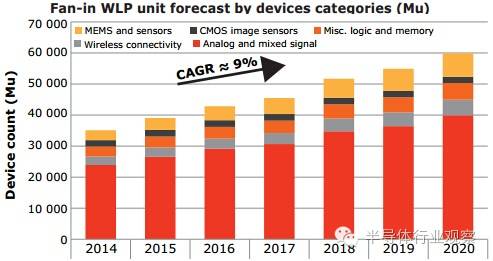

预计

FIWLP

将继续稳定增长,

2014

年

FIWLP

市场规模为

53

亿美元,

2014-2020

年复合年增长率为

7%

;等效

300mm

晶圆数量将达到

400

万片,复合年增长率为

8%

;而封装器件出货量为

360

亿颗,复合年增长率为

9%

,如下图所示。过去几年中,相比模拟、混合信号和数字

IC

,

MEMS

和

CMOS

图像传感器逐步占据更多的市场份额。

FIWLP

出货量预测(根据不同器件分类)

在模拟

/

混合信号

/

数字领域,主要的晶圆级应用需求是

BT + WiFi + FM

组合芯片、

RF

收发器、音频

/

视频解码器、直流

/

交流转换器、

ESD/EMI IPD

。在

MEMS

器件领域,主要应用需求来自电子罗盘、

RF

滤波器、加速度计和陀螺仪。另外,

CMOS

图像传感器也有强烈的应用需求。本报告深入分析了

FIWLP

的

41

个应用及其技术演进,覆盖

MEMS

、

CMOS

图像传感器、模拟

/

混合信号

/

数字等领域。

尽管存在超过十年,但是

FIWLP

仍然在不断演进,并吸引新的应用。当前市场数据表明

FIWLP

制造产能是充足的,并且越来越多的需求在

200mm

和

300mm

晶圆。此外,物联网将为