文章链接:https://pubs.acs.org/doi/10.1021/acs.nanolett.4c05884

这篇文章来自湖南大学刘渊教授团队,通过将三维金(Au)印章层压到单层二硫化钼(MoS2)上,然后剥离,实现对MoS2的选择性去除。近期的另一篇论文则是转移MoS2,见2025,Nature Electronics——百万阵列无损转移:二维材料技术新里程碑。后者优势更多,感兴趣的小伙伴可以对比下两种技术。

当然,还可以重温下这篇公众号2025,ACS Nano——从钻石表面拾取:突破性电极转移技术提升2D电子性能,这篇是利用弱相互作用,实现电极无损转移。

亮点

1.创新性干法图案化技术

提出了一种无聚合物、干法图案化的技术,通过使用三维金(Au)模具与单层MoS₂的层间剥离实现无损图案化,避免了湿法工艺的污染与高能刻蚀带来的退化。

2.提高器件性能与一致性

制备的MoS₂晶体管表现出:

o100%的器件成品率。

o显著提高的载流子迁移率。

o显著降低的器件间性能差异,提升器件一致性和可靠性。

3.全干法、简单快速

该技术摆脱了光刻工艺对聚合物和湿法刻蚀的依赖,提供了一种快速、高效的2D材料图案化方法,适合晶圆级规模化制备。

4.促进实验室到工业化的过渡

提供了一种适用于大规模生产的清洁、环保的2D半导体图案化策略,为2D电子器件的工业化应用铺平道路。

摘要

二维(2D)半导体因其作为未来晶体管通道材料的潜力而备受关注。将连续单层分离为独立单元的图案化技术是其中的关键。然而,当前基于光刻和高能等离子体/RIE刻蚀的图案化工艺存在不可避免的残留问题,降低了器件一致性,成为2D电子学实际应用的关键挑战。本文提出了一种无聚合物、干法图案化的技术,通过将三维金模具层压到单层MoS₂并剥离接触区域,实现快速、高效、无污染的图案化。相比传统湿法图案化工艺,该方法制备的MoS₂晶体管表现出100%的器件成品率、更高的载流子迁移率,以及显著降低的器件性能差异。这项工作为2D材料的实验室到工业化转化提供了一种简洁快速的干法图案化技术。

研究背景和主要内容

二维(2D)半导体作为未来晶体管的沟道材料引起了人们的广泛兴趣。由于具有无悬垂键表面,二维晶体管在最终减小体厚度方面具有巨大潜力,这对于削弱短沟道效应和相关的功耗至关重要。经过十年的深入研究,二维晶体管在单器件性能方面取得了快速进步。例如,单层 MoS2晶体管已实现 >1.23 mA/μm 的高驱动电流、42 Ω μm 的低接触电阻,超小型栅极长度低至 0.34 纳米(参考

(8)),以及小于 1 nm 的低 EOT (等效氧化物厚度),满足了IRDS(国际器件与系统路线图)未来晶体管的目标。迄今为止,成功实现从实验室到工厂转型的一个主要挑战是在晶圆规模上实现具有高器件一致性的这些概念验证器件。

尤其是图案化工艺,即将连续的二维单层分离成独立的功能单元,这对于电隔离二维半导体并进一步将其连接成复杂的集成电路至关重要。然而,目前的二维图案化技术很大程度上继承自硅基方法,即使用光刻作为掩模,然后使用等离子体(或反应离子)蚀刻不需要的二维材料。在此过程中,光刻胶去除后,不可避免的光刻胶残留物会残留在二维表面上,导致本征二维沟道内器件与器件之间的差异很大。更重要的是,随机分布的聚合物残留物也存在于金属接触区域下方,导致不均匀的接触电阻和接触屏障,进一步放大器件与器件之间的差异并降低其性能。我们注意到,此类光刻胶残留物也可能存在于传统的硅器件中,但由于两个原因,其影响要弱得多(与 2D 器件相比)。首先,硅上的聚合物残留物可以通过等离子/化学清洗或高温退火进一步去除,但这些侵蚀性工艺与 2D 电子产品不兼容,因为它们会损坏甚至完全破坏脆弱的单层晶格。其次,由于单层厚度,2D 晶体管本质上是一种“全表面器件”,其整体器件性能不仅由其固有特性决定,而且更多地受其表面条件的影响。因此,即使是少量的聚合物残留物(在图案化过程中)也会充当散射或掺杂的中心,从而降低晶圆级器件的均匀性和产量。

为了避免传统图案化工艺中的聚合物残留问题,并提高其均匀性,人们投入了大量精力来开发干法图案化工艺。例如,人们已经使用微尺度探针直接将二维薄膜刮成所需的图案。在此过程中,二维单层通过纯机械力或热机械压痕进行图案化(或切割),图案化区域不与任何聚合物直接接触,因此呈现出无残留的原子级洁净表面。同样,激光也已应用于通过简单的局部加热效应直接去除不需要的二维材料,从而实现无光刻工艺和无残留的二维表面。然而,这些方法都是基于探针尖端或激光点的缓慢移动,这很耗时,而且不可扩展。此外,激光切割过程可能涉及局部温度升高,因此边缘可能出现氧化状态。因此,开发一种无聚合物的晶圆级 2D 半导体图案化技术对于其实际应用至关重要。

在这里,我们开发了一种无聚合物干法图案化技术,该技术可以快速图案化晶圆级二维半导体,而无需使用任何聚合物。将三维 (3D) Au 印章层压到单层 MoS2上,然后将其剥离,由于 Au-MoS2之间的强相互作用,Au 接触的 MoS2区域将被有效去除,而非接触区域则留在其生长的基底上,从而实现成功的干法图案化工艺。作为我们方法的一部分,晶圆级图案化仅基于物理接触和剥离过程,因此可以在几分钟内完成,与以前基于探针刮擦或激光切割的不可扩展图案化工艺相比,可实现高通量设备。更重要的是,图案化区域不与任何聚合物或溶液接触,确保其设备间高度均匀性。已经进行了详细的应用原子力显微镜 (AFM)、拉曼和光致发光 (PL) 表征,验证了图案化 MoS 2的原子级清洁表面和固有特性。此外,我们还基于干法图案化和干法层压工艺制造了晶圆级 MoS2晶体管,与使用传统基于光刻的图案化技术的对照样品相比,其器件成品率达到 100%,载流子迁移率提高了 2 倍,器件变化大大减少。我们的工作提供了一种简单快速的技术来图案化具有固有属性和高均匀性的大规模二维材料,这对于二维电子产品的实际应用及其从实验室到工厂的转变非常重要。它还可能对相关的范德华异质结构和单片三维堆叠电路产生许多影响,其中聚合物残留物的影响可能会随着堆叠层数的增加而呈指数级增长。

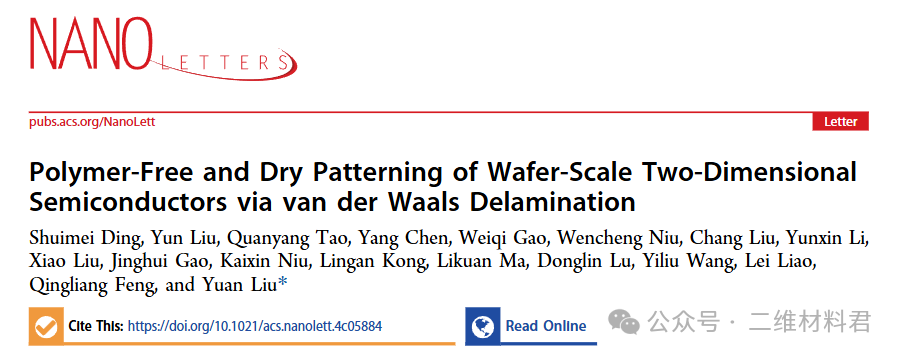

图 1. 单层 MoS2干法图案化工艺示意图和图像。干法图案化工艺示意图,包括三个步骤:(a) 制作 3D Au 印章,(b) 合成连续单层 MoS2,(c) 使用 3D Au 印章图案化单层 MoS2。 (d–f) 面板 a–c 中各步骤对应的光学图像。比例尺为 20 μm。(g–i) 2 英寸比例干法图案化工艺的对应照片。

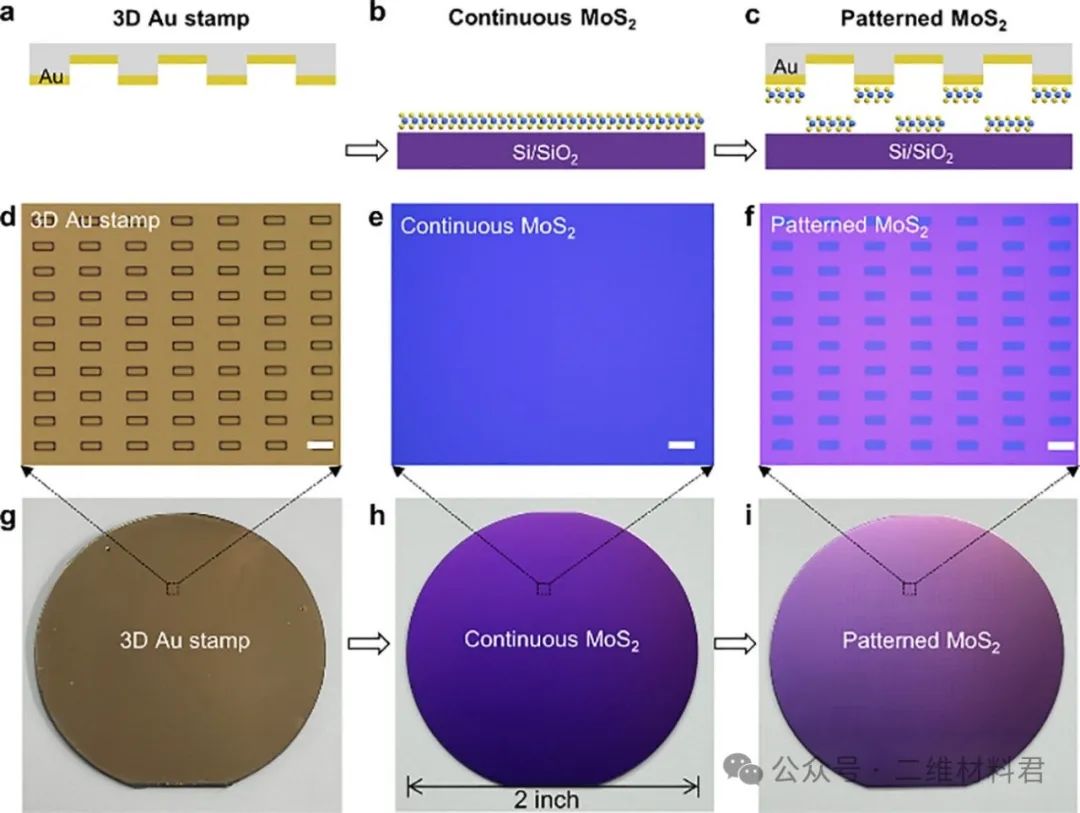

图 2. 干法图案化 2D 单层膜的特性。(a 和 b) 干法图案化样品的示意图和 AFM 图像,显示原子级平坦表面,粗糙度低至 0.28 nm。比例尺为 2 μm。(c 和 d) 传统“湿法图案化”样品的示意图和 AFM 图像,显示清晰的聚合物残留物和较大的表面粗糙度。比例尺为 2 μm。不同 MoS 2图案阵列的光学图像:(e) 圆形、(f) 正方形、(g) 三角形和 (h) 字母字符。比例尺为 20 μm。(i) 单层 MoS 2的拉曼光谱和 (j) PL 光谱,显示原生样品(黑线)和干法图案化样品(红线)的峰位置一致。(k 和 l)分别为干法图案化 MoS 2单层的拉曼和 PL 映射,显示了图案化单层的高度均匀性。比例尺为 10 μm。

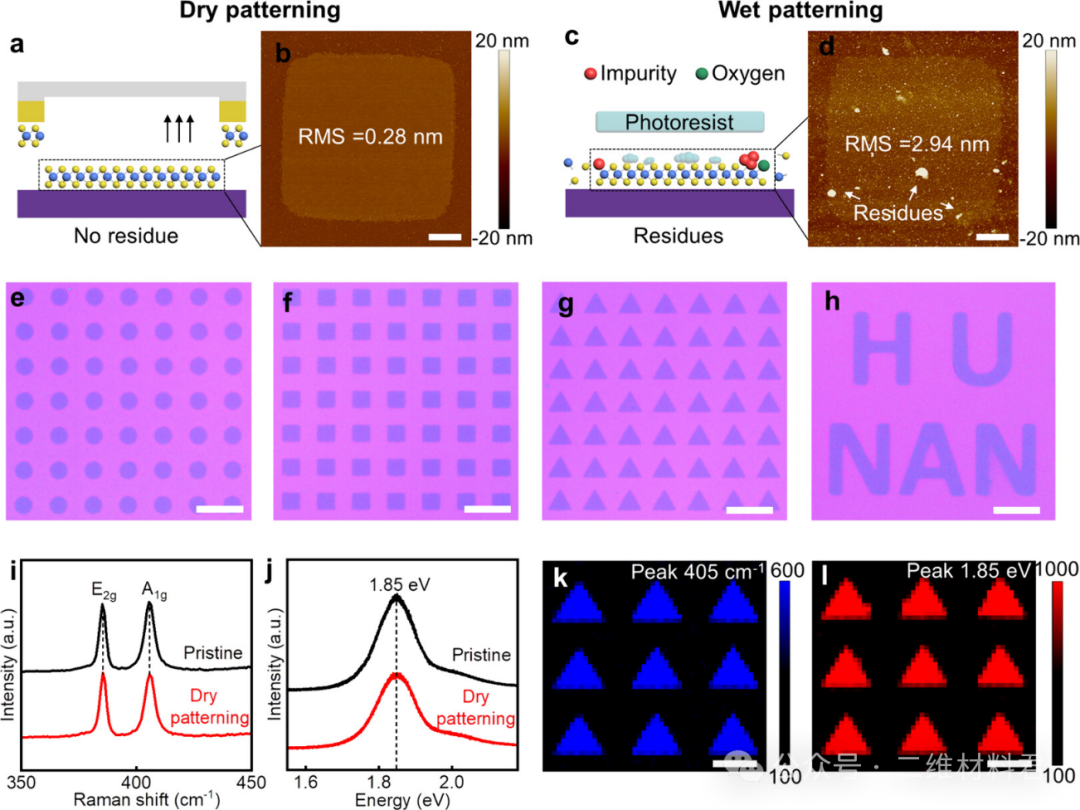

图 3. 全干法制备的 MoS2 FET 的电气性能。(a 和 b) 分别为单层 MoS2 FET的示意图和光学图像。比例尺为 10 μm。(c) 100 个全干法制备 MoS2晶体管的Ids – Vgs转移曲线,其中所有器件均正常工作,成品率 100%。(d) 100 个湿法图案化 MoS2晶体管的Ids – Vgs传输曲线。五个器件失效。(e) 干法图案化和湿法图案化器件的导通电流 ( Ion ) 和关断电流 ( Ioff ) 的散点图。(f) 干法图案化样品(红色)和湿法图案化样品(黑色)的载流子迁移率直方图。提取的 2 英寸晶圆上器件的(g)开/关比、(h) V th和(i)迁移率的彩色图。

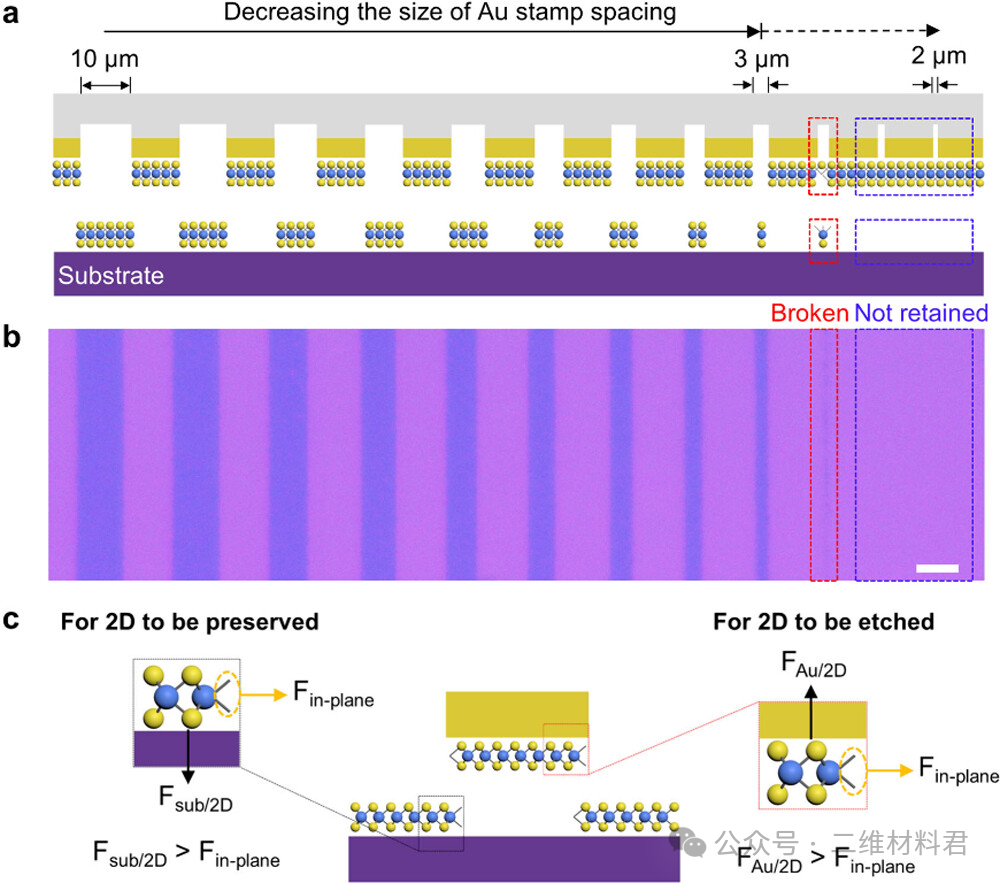

图 4. 研究干法图案化工艺的临界尺寸。(a 和 b) 分别为具有不同间距的 3D 凸块金(非接触区域的长度不同)的图案化工艺示意图和光学图像。当金间距大于临界尺寸时,可以观察到清晰的干法图案化。当金间距太小时,所有 MoS2单层都将被去除。比例尺为 10 μm。(c) 图案化机制分析,其中需要满足F