其主要工作职责有:

➤ 芯片物理结构分析

➤ 逻辑分析

➤ 建立后端设计流程

➤ 版图布局布线

➤ 版图编辑

➤ 版图物理验证

➤ 联络代工厂并提交生产数据

作为连接设计与制造的桥梁,合格的版图设计人员既要懂得IC设计、版图设计方面的专业知识,还要熟悉制程厂的工作流程、制程原理等相关知识。

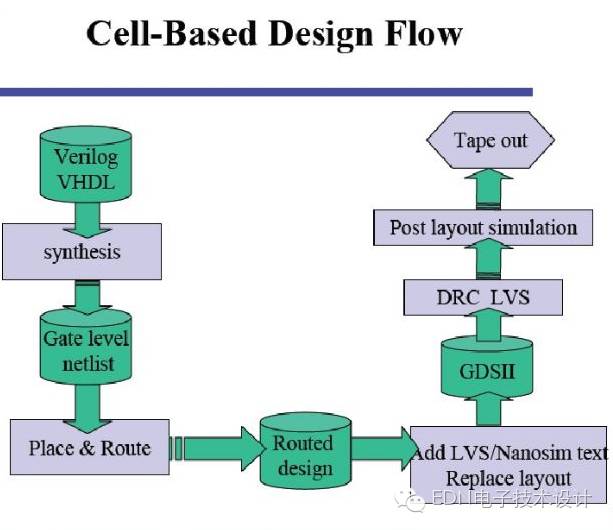

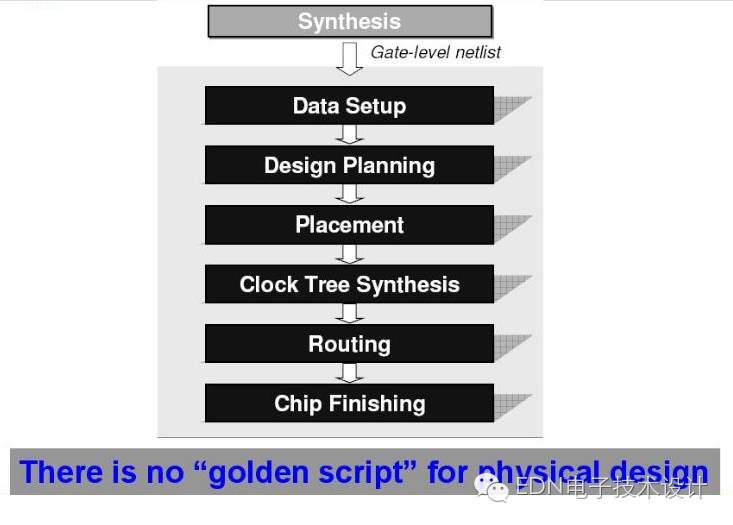

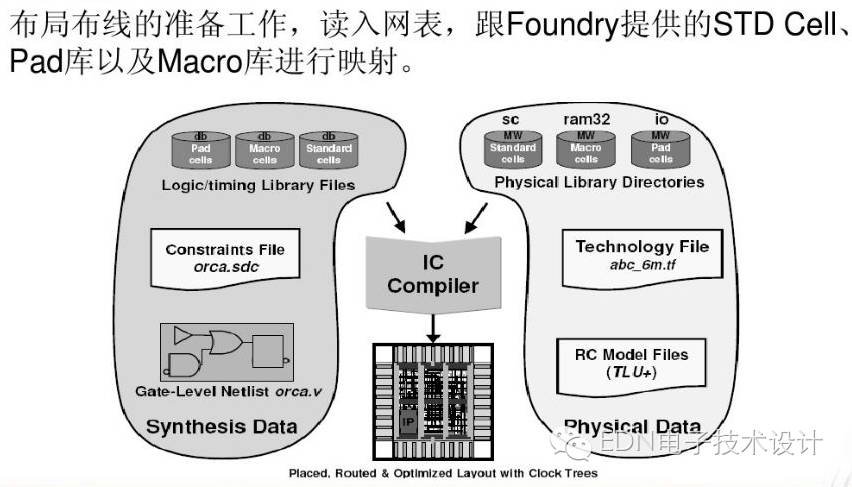

IC后端设计流程——总体流程

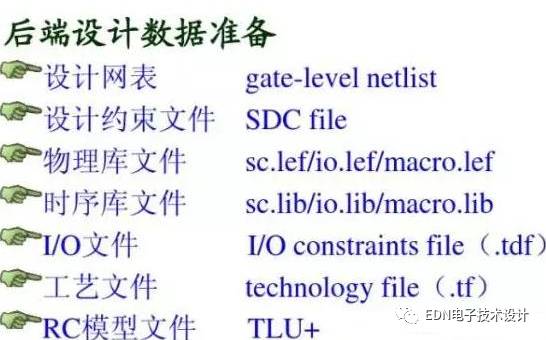

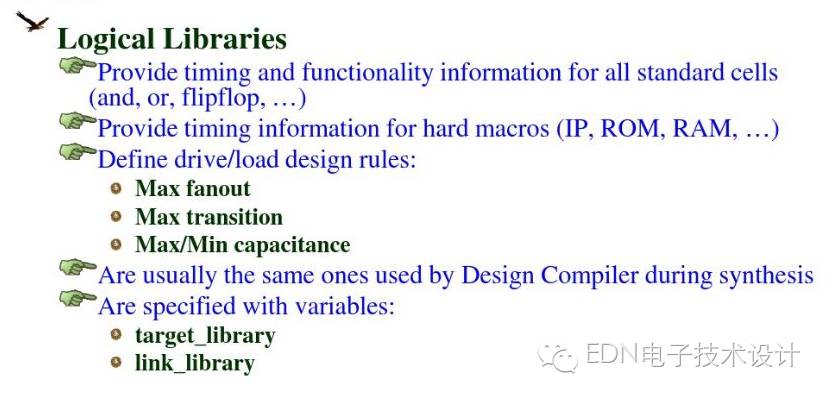

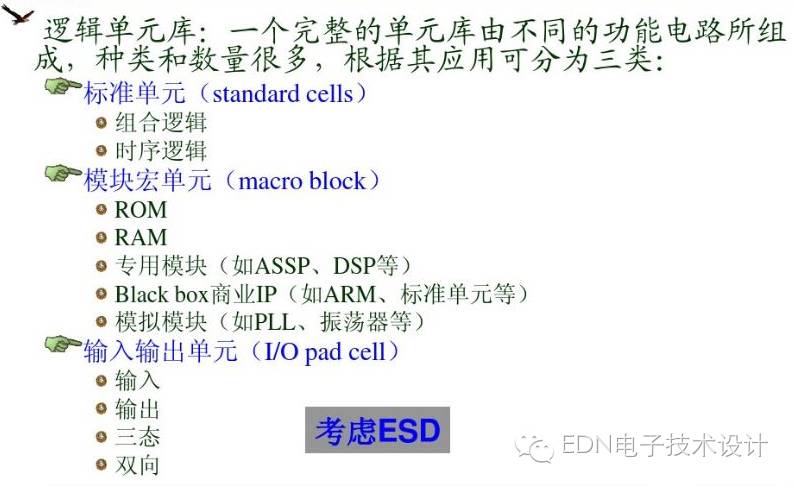

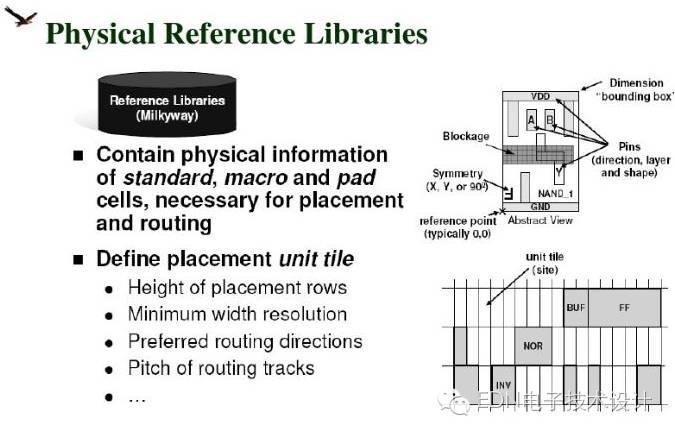

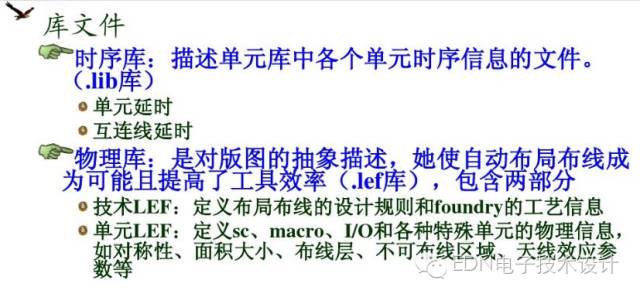

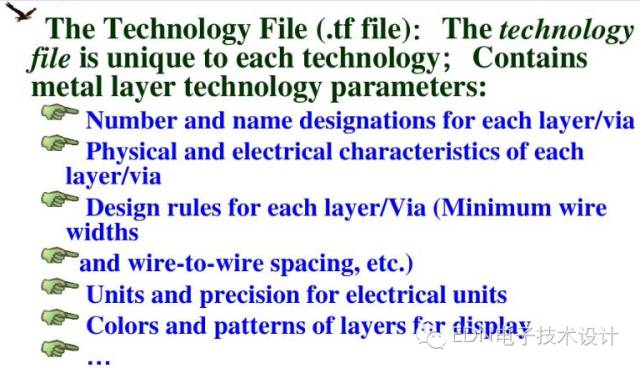

对于 CDN 的 Silicon Ensemble而言后端设计所需的数据主要有是Foundry厂提供的标准单元、宏单元和I/O Pad的库文件,它包括物理库、时序库及网表库,分别以.lef、.tlf和.v的形式给出。前端的芯片设计经过综合后生成的门级网表,具有时序约束和时钟定义的脚本文件和由此产生的.gcf约束文件以及定义电源Pad的DEF(DesignExchange Format)文件。(对synopsys 的Astro 而言,经过综合后生成的门级网表,时序约束文件 SDC是一样的,Pad的定义文件--tdf , .tf 文件 --technology file, Foundry厂提供的标准单元、宏单元和I/OPad的库文件就与FRAM, CELL view, LM view 形式给出(Milkway 参考库 and DB, LIB file)

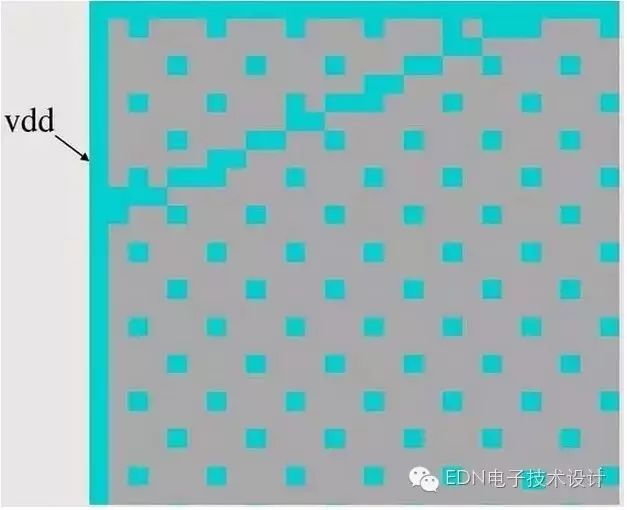

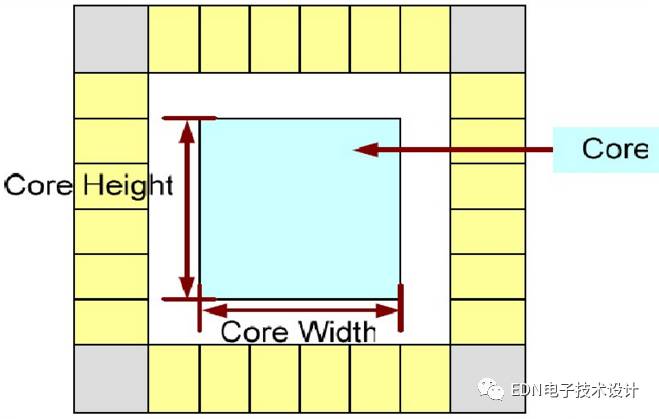

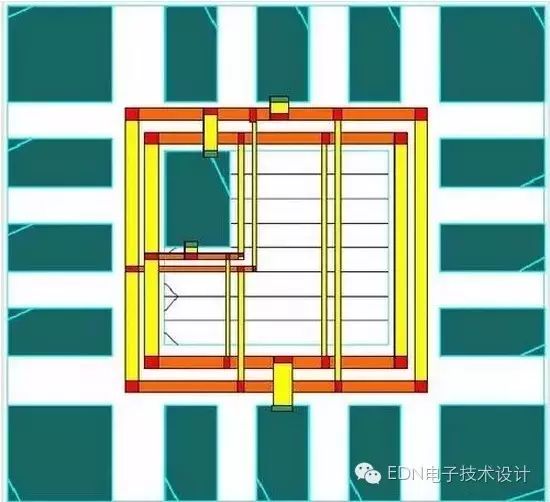

主要是标准单元、I/O Pad和宏单元的布局。I/OPad预先给出了位置,而宏单元则根据时序要求进行摆放,标准单元则是给出了一定的区域由工具自动摆放。布局规划后,芯片的大小,Core的面积,Row的形式、电源及地线的Ring和Strip都确定下来了。如果必要在自动放置标准单元和宏单元之后,可以先做一次PNA(power network analysis)--IR drop and EM .

●Placement -自动放置标准单元

布局规划后,宏单元、I/O Pad的位置和放置标准单元的区域都已确定,这些信息SE(SiliconEnsemble)会通过DEF文件传递给PC(PhysicalCompiler),PC根据由综合给出的.DB文件获得网表和时序约束信息进行自动放置标准单元,同时进行时序检查和单元放置优化。如果我们用的是PC+Astro,那可用write_milkway, read_milkway 传递数据。

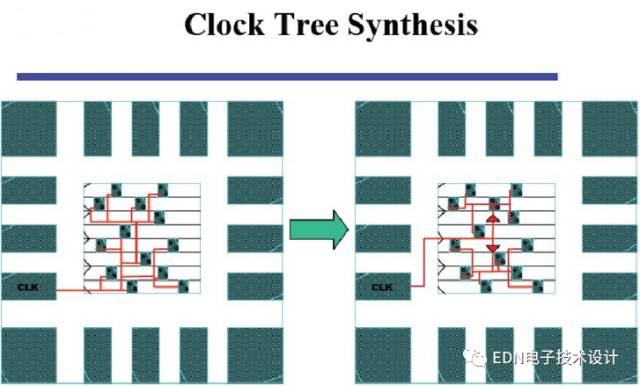

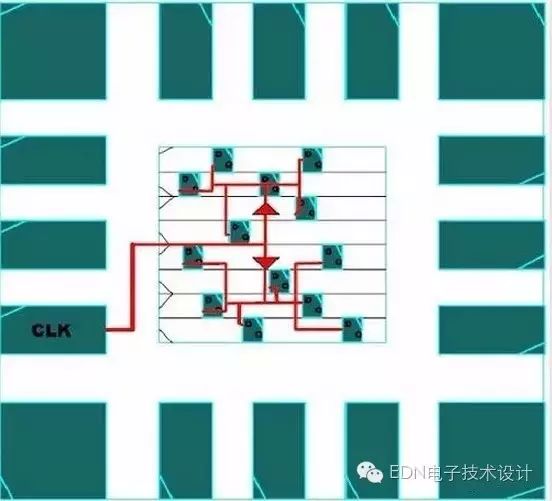

●时钟树生成(CTS Clock tree synthesis)

芯片中的时钟网络要驱动电路中所有的时序单元,所以时钟源端门单元带载很多,其负载延时很大并且不平衡,需要插入缓冲器减小负载和平衡延时。时钟网络及其上的缓冲器构成了时钟树。一般要反复几次才可以做出一个比较理想的时钟树。

时钟树插入后,每个单元的位置都确定下来了,工具可以提出GlobalRoute形式的连线寄生参数,此时对延时参数的提取就比较准确了。SE把.V和.SDF文件传递给PrimeTime做静态时序分析。确认没有时序违规后,将这来两个文件传递给前端人员做后仿真。对Astro 而言,在detail routing 之后,用starRC XT 参数提取,生成的E.V和.SDF文件传递给PrimeTime做静态时序分析,那将会更准确。

●ECO(Engineering Change Order)

对静态时序分析和后仿真中出现的问题,对电路和单元布局进行小范围的改动。

●Filler的插入(pad fliier, cell filler)

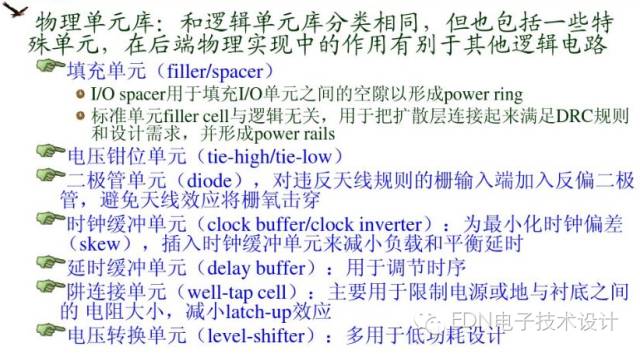

Filler指的是标准单元库和I/O Pad库中定义的与逻辑无关的填充物,用来填充标准单元和标准单元之间,I/O Pad和I/O Pad之间的间隙,它主要是把扩散层连接起来,满足DRC规则和设计需要。

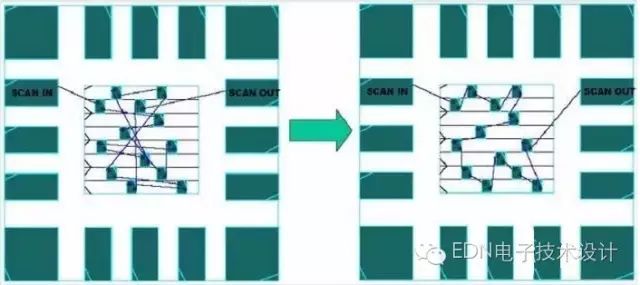

Global route-- Track assign --Detail routing--Routing optimization布线是指在满足工艺规则和布线层数限制、线宽、线间距限制和各线网可靠绝缘的电性能约束的条件下,根据电路的连接关系将各单元和I/OPad用互连线连接起来,这些是在时序驱动(Timing driven )的条件下进行的,保证关键时序路径上的连线长度能够最小。