首先做个广告,分享一个优秀的旅行及历史的共众号

Lightheartedness

,欢迎关注。

分享旅行攻略,世界历史

微信公众号:Lightheartedness

ID:Eastjunwei

大数据文摘编辑部出品

来源:

venturebeat

之前文摘菌报道了一家

印度初创公司

打着AI的旗号,干的却是人工的活,还拿到了2950万美元的融资。

但是大部分AI公司拿到融资还是真正去做AI的,比如这家名叫Cerebras的公司,在2016年也获得2500万美元的投资用于开发深度学习硬件设备。

如今,研究终于出了成果。

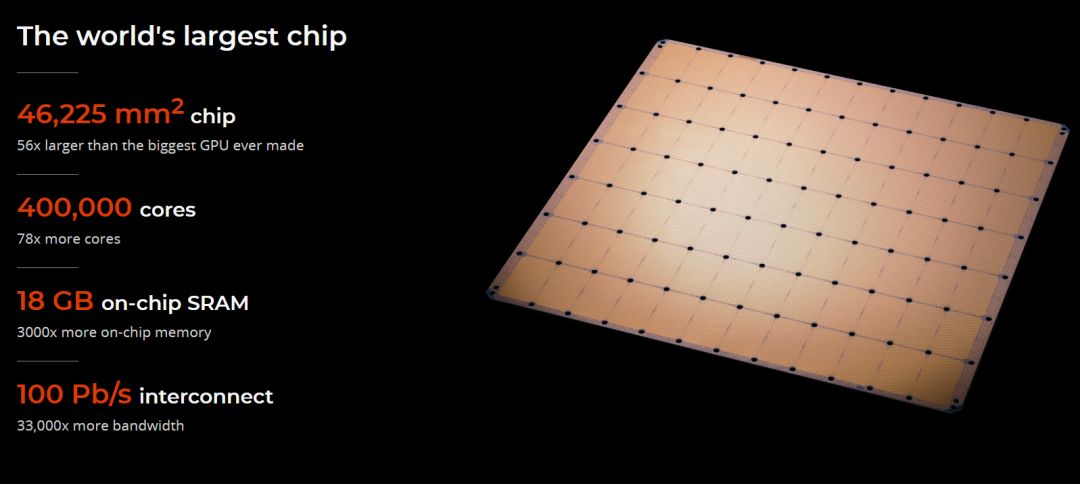

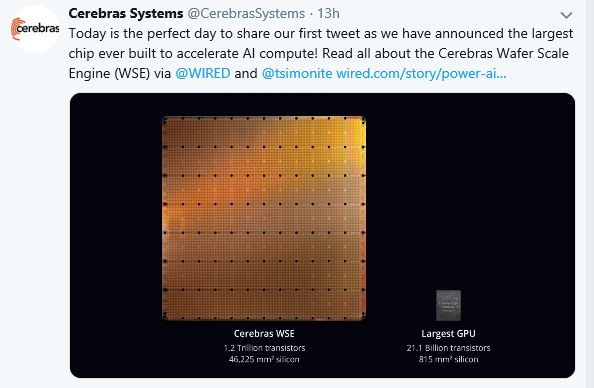

据ventruebeat报道,Cerebras推出了拥有1.2万亿晶体管的史上最大半导体芯片。

看来投资人可以松口气了。

1971年英特尔首款4004处理器拥有2,300个晶体管,最近的Advanced Micro Devices处理器拥有320亿个晶体管。

而这款史上最大的芯片Cerebras Wafer Scale Engine拥有1.2万亿个晶体管。

大多数芯片是在12英寸硅晶片上创建芯片集合,并在芯片工厂中批量处理。

但Cerebras Systems芯片是在单个晶圆上互连的单芯片。

这些互连设计使其全部保持高速运行的状态,因此1.2万亿个晶体管全部一起工作。

通过这种方式,Cerebras Wafer Scale Engine是有史以来最大的处理器,它专门设计用于处理人工智能应用程序。

该公司本周正在加利福尼亚州帕洛阿尔托的斯坦福大学举行的Hot Chips会议上讨论这项设计。

此前三星已经制造了一个很大的闪存芯片,即eUFS,拥有2万亿个晶体管。

但Cerebras芯片专为流程加工而设计,拥有400,000个内核,42,225平方毫米。

它比最大的Nvidia GPU大 56.7倍。

WSE还包含3,000倍的高速片上存储器和10,000倍的存储器带宽。

WSE包含400,000个AI优化的计算内核(compute cores)。

被称为SLAC(Sparse Linear Algebra Cores),计算内核灵活,支持编程,并针对支持所有神经网络计算的稀疏线性代数进行了优化。

SLAC的可编程性确保内核可以在日新月异的机器学习领域中运行所有神经网络算法。

由于稀疏线性代数内核针对神经网络计算进行了优化,因此它们可实现业界最佳资源利用率——通常是图形处理单元的三倍或四倍。

此外,WSE内核包括Cerebras发明的稀疏性收集技术,以及加速稀疏工作负载(包括0的工作负载)的计算性能,如深度学习。

0在深度学习计算中很普遍。

通常,要相乘的向量和矩阵中的大多数元素都是0。

然而,乘以零是浪费资源,功率和时间的行为。

因为GPU和CPU是密集的执行引擎——引擎的设计是永不遇到0——它们即使在遇到0时也会进行计算。

当50%-98%的数据为零时,比如深度学习中的情况,大多数乘法都没有意义。

而Cerebras稀疏线性代数内核不会乘以零,所有零数据都会被过滤,直接在硬件中跳过,从而可以释放资源完成其他有用的工作。

内存是计算机体系结构的关键部分。

更接近计算的内存意味着计算速度更快、更低的延迟和更好的数据移动效率。

高性能深度学习需要大量计算,并且频繁访问数据。

这需要计算内核和存储器之间的紧密接近,这在GPU中并非如此。

Cerebras Wafer Scale Engine则包含更多内核,具有比迄今为止任何芯片都有更多的本地内存,并且在一个时钟周期内可以通过其内核访问18GB的片上内存。

WSE上的内核本地内存集合可提供每秒9PB的内存带宽——比领先的GPU多3,000倍的片上内存和10,000倍的内存带宽。

Swarm通信结构是WSE上使用的处理器间通信结构,它以传统通信技术的功耗的一小部分实现突破性带宽和低延迟。

Swarm提供低延迟,高带宽的2D网格,可连接WSE上的所有400,000个核,每秒带宽为100 petabits。

Swarm支持单字活动消息,可以直接通过接收内核来处理。

路由、可靠的通信和同步在硬件中处理。

消息会自动激活每个到达消息的应用程序处理程序Swarm为每个神经网络提供独特的优化通信路径。

软件根据正在运行的特定用户定义的神经网络的结构,配置通过400,000个内核的最佳通信路径以连接处理器。

一个Cerebras WSE的总带宽为每秒100petabits,不需要诸如TCP/IP和MPI之类的通信协议。

并且该架构中的通信能量成本远低于1焦耳每比特,这比GPU低近两个数量级。

通过结合大的带宽和极低的延迟,Swarm通信结构使Cerebras WSE能够比任何当前可用的解决方案进行更快地学习。

承担计算任务的芯片尺寸在AI应用中非常重要,因为更大的芯片可以更快地处理信息,在更短的时间内得出结果。

训练时间的减少,可以使研究人员能够进行更多测试,使用更多数据并解决新的问题。

谷歌、Facebook、OpenAI、腾讯、百度都认为,今天人工智能的基本限制是训练模型需要很长时间。

因此,训练时间是整个AI行业进步的主要瓶颈。

当然,一般芯片制造商不会生产这么大的芯片是有原因的。

在单个晶圆片上,在制造过程中通常会出现一些杂质。

如果一个杂质可以导致芯片的故障,那么晶圆片上的多个杂质就会击穿几片芯片。

从而导致实际的效益只是实际工作的芯片的一部分。

如果晶圆片上只有一个晶片,那么它含有杂质的可能性是100%,杂质会使晶片失效。

但是Cerebras芯片是设计成冗余的,所以一个杂质不会使整个芯片失效。

“而设计的人工智能工作,Cerebras WSE包含基本的创新,解决了几十年以来限制芯片尺寸的技术挑战,如cross-reticle的连接性、产量、功率输出和包装,”Cerebras的创始人兼CEO Feldman在一份声明中说,“每一个架构决策都是为了优化人工智能工作的性能,其结果是,Cerebras WSE在功耗和空间很小的情况下,根据工作负载提供了现有解决方案数百或数千倍的性能。

”

Linley Group首席分析师Linley Gwennap在一份声明中表示:

“Cerebras在晶片规模的技术上取得了巨大进步,在一块硅片上实现的处理性能超出想象。

”为了实现这一壮举,该公司已经解决了困扰该行业数十年的一系列工程挑战,包括实现高速模对模通信、解决制造缺陷、封装如此大的芯片、提供高密度电源和冷却。

通过将不同学科的顶尖工程师聚集在一起,Cerebras创造了新技术,并在短短几年内交付了一个产品,这是一个令人印象深刻的成就。

”