为了方便各位同学交流学习,解决讨论问题,我们建立了一些微信群,作为互助交流的平台。

2.告知:姓名-课题组-研究方向,由编辑审核后邀请至对应交流群(生长,物性,器件);

欢迎投稿欢迎课题组投递中文宣传稿,免费宣传成果,发布招聘广告,具体联系人:13162018291(微信同号)

【研究背景】

摩尔定律时代以硅(Si)集成电路的微缩为特征,带来了计算能力和微型化的卓越进展。然而,随着基于硅的器件逐渐接近物理极限,短沟道效应增强、功耗增加、热耗散以及量子隧穿等问题相继出现,这些挑战了摩尔定律的持续性。一个值得注意的策略是将二维材料与硅集成电路相结合,以克服硅的固有局限,潜在地提升电子设备的性能并推进摩尔定律。除硅混合集成方法之外,基于二维材料的集成电子学正引起广泛关注。该策略旨在通过利用二维材料来继续遵循摩尔定律的缩放原则,从而推进互补金属氧化物半导体(CMOS)技术。关于二维材料基器件结构、沟道材料和高介电常数绝缘体的创新研究至关重要。更为重要的是,“超摩尔”(More-than-Moore)时代设想通过单片三维(M3D)集成来实现高器件密度和多功能性。这种综合方法满足了感知、光电、物联网和人工智能等应用领域不断增长的期望和需求。

CMOS技术通过结合p型和n型晶体管,凭其高效的功耗、低静态功率耗散和高抗噪性,成为现代电子学的基石。在二维材料领域,如二硫化钼(MoS

2

)等n型半导体取得了显著进展,展现出高电子迁移率和稳定性。然而,二维p型半导体的发展步伐相对缓慢。稳定的、高空穴迁移率且具有良好开关比的p型材料仍然匮乏。此外,将p型二维晶体管整合到M3D架构中仍处于早期阶段。

将M3D CMOS系统与基于二维材料的n型和p型晶体管集成是一个复杂的过程,需要谨慎选择材料并采用先进的制造技术。实现高性能M3D CMOS集成还需要高质量的二维p型半导体、完善的合成方法、精确的界面工程以及有效的缺陷控制。材料合成、器件架构和界面工程方面的进步,使得高性能、低功耗电子设备的生产成为可能。

【成果介绍】

鉴于此,浦项科技大学的Yong-Young Noh教授,邹涛隅博士和电子科技大学的刘奥教授发表了题为“Monolithic three-dimensional integration with 2D material-based p-type transistors”的综述论文在Materials Science and Engineering: R: Reports期刊(IF=31.6)上。该论文对基于二维材料p型晶体管的M3D集成的最新进展和持续挑战进行了全面分析。论文首先总结二维p型半导体的现状,重点关注过渡金属二硫族化合物(TMDs)、单元素和复合半导体等关键材料。随后概述了对生产高质量二维p型材料至关重要的合成技术,详细阐述了针对不同二维p型半导体的具体方法。接着,探索了将这些材料整合到M3D架构中的集成策略,讨论了材料选择、器件性能优化和制造工艺的复杂性。此外,本文还讨论了平面集成、三维堆叠互补场效应晶体管(CFETs)以及M3D集成。最后,文章还对基于M3D集成的二维p型晶体管的潜在应用提供了见解,强调了它们提升器件性能和集成密度的能力。

【图文导读】

(仅展示Fig. 1~5)

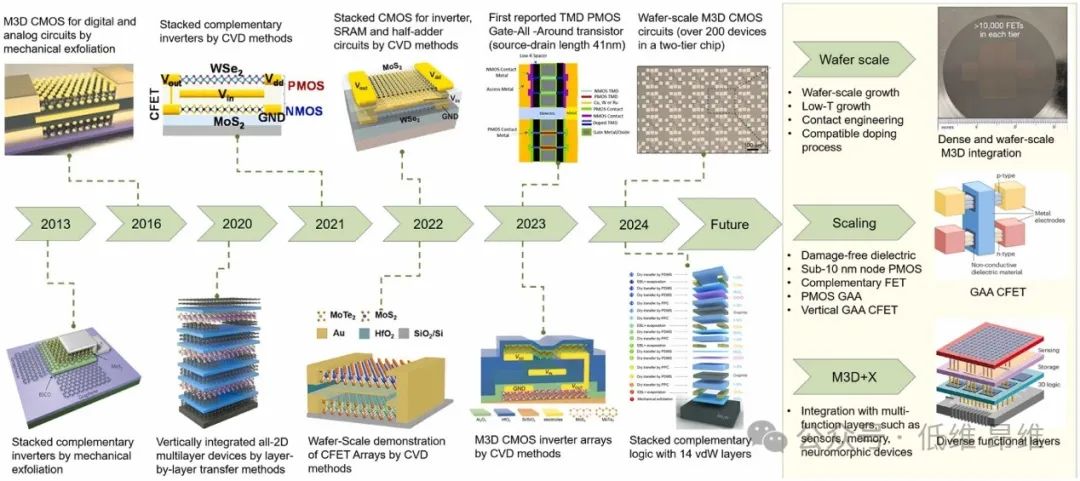

图 1. M3D与p型2D晶体管集成的发展及其未来发展前景。

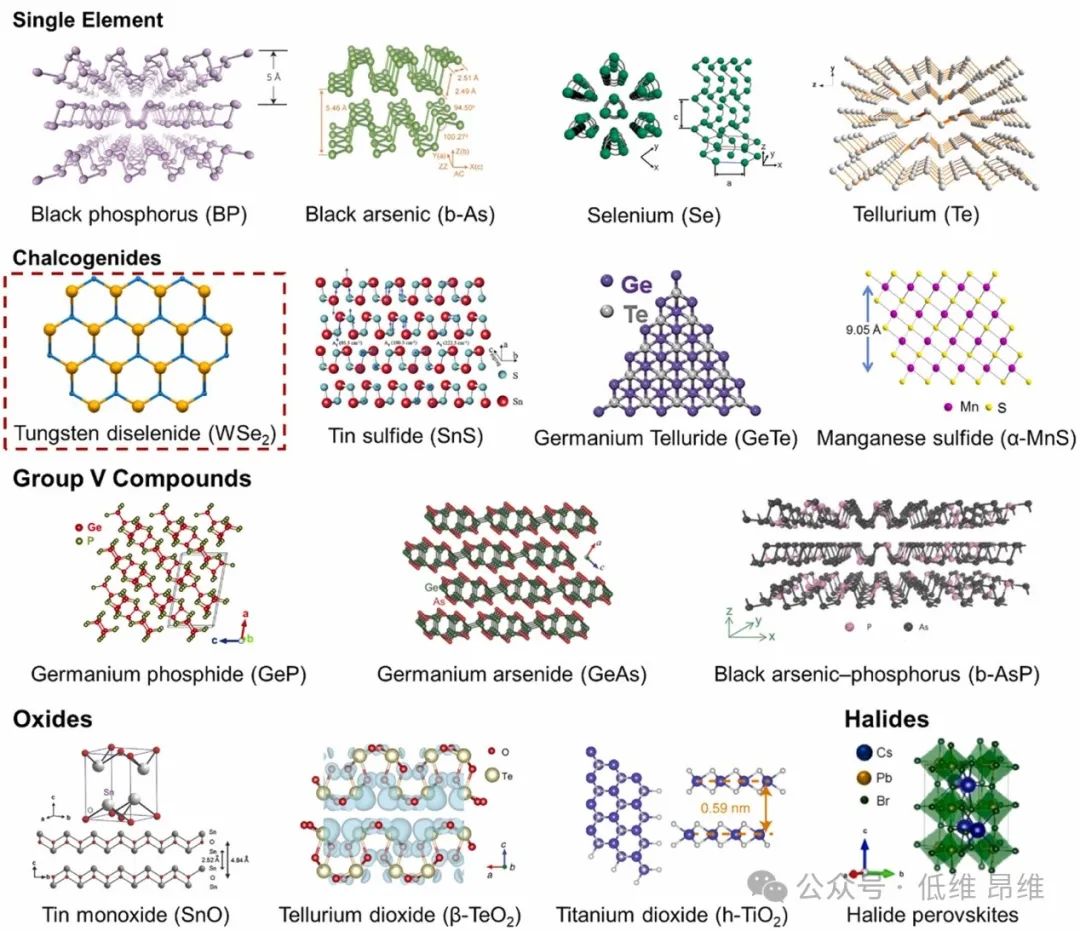

图 2. 代表性p型2D半导体的结构,其中WSe

2

突出显示为M3D集成的主要p型半导体。

图 16. (a) TSV-3D、传统 M3D 和提出的 2D-M3D 的估计层厚度和集成密度。 (b) 通过逐层范德华组装的垂直集成多层功能设备,包括存储器、逻辑和传感器。 (c) 通过多次循环层压的 MoS2 通道和电路层集成的 10 层 M3D 系统的示意图。 (d) 对应的 10 层 M3D 系统的光学图像。

图 17. (a) 共享栅极 M3D CMOS 结构的 HRTEM 图像。MoS2 和 WSe2 区域的 EDS 映射。 (b) 模拟电路底层和顶层的光学图像。 (c) 平面 CMOS 和堆叠 CFET 技术在常见电路单元的面积比较。 (d) 基于 2D CFET 的反相器的静态功耗的箱形图和比较。 (e) CFET 4T SRAM 的布局图像和功能。刻度尺:10 微米。 (f) 基于 CFET 设计的半加器的电路原理图、布局图像和功能。

图 18. (a) 带有垂直可逆极化场效应晶体管的未来 M3D 集成电路的展望。 (b) 在“更多摩尔”和“超越摩尔”技术中 2D FETs 3D 集成的潜力示意图。 (c) 三层芯片的光学图像。插图为其中一个三层 3D 设备堆叠的顶视图伪彩色扫描电子显微镜(SEM)图像。

【总结展望】

总之,解决当前二维p型晶体管面临的问题对推进M3D集成至关重要。这将使得二维p型半导体与现有半导体的集成更为顺畅,提高器件密度和功能,并保持与现有制造方法的兼容性。顺利利用这些材料对未来电子学至关重要,其可以提供更优异的性能、更低的功耗以及新颖的功能特性。

【文献信息】

Taoyu Zou, Youjin Reo, Seongmin Heo, Haksoon Jung, Soonhyo Kim, Ao Liu, Yong-Young Noh. Monolithic three-dimensional integration with 2D material-based p-type transistors. Materials Science and Engineering: R: Reports. 2025, 163, 100893.

文献链接:https://doi.org/10.1016/j.mser.2024.100893.

上

海

昂

维

科

技

有

限

公

司

现

提

供

二

维

材

料

单

晶

和

薄

膜

等

耗

材

,

器