该文章介绍了一种运行时电可重构的二维电荷俘获晶体管(CTTs),该器件基于介电工程化的二维半导体晶体管,具有多种功能模式,包括逻辑开关、非易失存储、人工突触和三值内容可寻址存储器(TCAM)。这项研究展示了面向未来功能灵活、高效的存内计算硬件的潜力。文章还提供了图文导读和文献信息。

随着数据驱动的应用在人工智能、物联网等领域的快速发展,半导体电子面临越来越高的计算平台需求。存内计算是一种有前景的架构,旨在增强半导体电子在新一代数据驱动信息处理中的能力。这种架构设计面临操作算法和硬件协同优化、底层材料、器件和工作物理创新等挑战。

为了应对存内计算架构设计的需求,开发运行时功能可重构的电子器件是一个新兴CMOS扩展解决方案。这种器件将存内计算的关键功能集成到一个单元中,简化电路、改进性能、降低制造复杂性和成本,并提高功能灵活性。

西安电子科技大学罗拯东教授、刘艳教授和西北工业大学甘雪涛教授合作发表了题为“Reconfigurable Logic and in-Memory Computing Based on Electrically Controlled Charge Trapping in Dielectric Engineered 2片尾半导体Transistors”的论文。该论文展示了一种运行时电可重构的二维电荷俘获晶体管(CTTs),具有多种功能模式,包括逻辑开关、非易失存储、人工突触和TCAM。这种器件概念基于简单的CMOS晶体管结构,通过电荷俘获/释放效应实现功能模式的转换。

该工作展示了面向未来功能灵活、高效的存内计算硬件的潜力。通过与CMOS兼容的混合介电栅极堆叠结构,可以实现各种功能模式。此外,该研究工作还体现了紧凑的双晶体管架构,并能够在系统级别实现卷积神经网络的模拟仿真。这些成果对于设计适用于强大存内计算系统的CMOS兼容构建模块具有前景。

为了方便各位同学交流学习,解决讨论问题,我们建立了一些微信群,作为互助交流的平台。

2.告知:姓名-课题组-研究方向,由编辑审核后邀请至对应交流群(生长,物性,器件);

欢迎投稿欢迎课题组投递中文宣传稿,免费宣传成果,发布招聘广告,具体联系人:13162018291(微信同号)

【研究背景】

数据驱动的应用在人工智能(AI)、物联网(IoT)、边缘和云计算等领域快速发展,已成为信息技术产业变革的主要推动力。作为信息技术的基础支柱,半导体电子面临着越来越高的计算平台需求,这些需求体现在系统的运行方式、功能和性能上。因此,业界普遍认为未来信息处理需要在整个系统堆栈中进行创新。最近,人们发现存内计算是一种有前景的架构,旨在增强半导体电子在新一代数据驱动信息处理中的能力。这种架构设计勾勒出一个在存储单元内执行计算任务的新计算概念,有望解决传统冯·诺依曼计算平台面临的突出信息处理效率和功能挑战。这场架构革命需要对操作算法和硬件进行系统性的协同优化,推动底层材料、器件和工作物理的创新,以实现系统功能增强的目标。因此,存内计算的设计对主流硅基互补金属氧化物半导体(CMOS)技术提出了新的挑战,需要探索能够提供创新物理原理和增强性能指标的功能材料和器件结构,以满足存内计算的严格要求。

在架构设计层面确定存内计算系统的运行原则时,一个新兴的CMOS扩展解决方案是开发运行时功能可重构的电子器件,将存内计算的关键功能集成到一个单元中。根据这一设计原则,存内计算电路的逻辑、存储、突触和其他所需功能单元最终可以基于相同的功能材料、器件结构和制造工艺来实现。这种策略被认为能够创建一个具有简化电路、改进性能、降低制造复杂性和成本以及高度功能灵活性的可重构平台。受这种可重构技术的启发,人们对基于硅系统的可重构CMOS晶体管进行了大量研究;然而,这种方法遇到了源于硅材料物理属性和CMOS晶体管工作原理的巨大约束。因此,要释放可重构电子器件在存内计算中的全部潜力,迫切需要能够利用创新材料系统和操作物理优势的器件概念。二维半导体具有与CMOS工艺兼容的制造、原子级薄的载流子传输体、卓越的静电控制、两极性开关以及与各种物理刺激相互作用的潜力,通过创建高性能、超小规模和多功能的可重构晶体管,可以在CMOS扩展领域实现理想的功能。大多数已展示的可重构器件需要重新设计传统

金属-氧化物-半导

体场效应晶体管(MOSFET)的结构和/或操作方法,需要额外的控制变量,如多个控制栅极,使用光作为编程参数等,而不是采用传统MOSFET的简单单控制栅极结构。总的来说,使用二维可重构晶体管的新一代存内计算架构的成功,将极大地取决于发现一种器件概念,该概念需要紧凑的器件结构、高效的操作方案、可靠的工作机制、简单且可扩展的制造方法以及理想的材料系统。

【成果介绍】

鉴于此,

西安电子科技大学罗拯东教授、刘艳教授和西北工业大学甘雪涛教授合作发表了题为“Reconfigurable Logic and in-Memory Computing Based on Electrically Controlled Charge Trapping in Dielectric Engineered 2D Semiconductor Transistors”的论文在Advanced Functional Materials期刊上。该工作展示了一种运行时电可重构的二维电荷俘获晶体管(CTT),它利用界面电荷俘获和瞬态场调制效应使能的多功能静电的协同集成,成功实现了从阈值电压可调逻辑开关、非易失存储、人工突触到复杂的三值内容可寻址存储器(TCAM)的器件功能模式。本工作的新器件概念基于在二维MoS

2

半导体沟道附近耦合的电荷存储界面的简单介电工程,保持了简单的CMOS晶体管结构,使电荷俘获/释放诱导的可调静电成为可能。通过精细的紫外臭氧处理,在与CMOS兼容的AlN介电层顶部创建了超薄AlO

x

层,该层在MOSFET结构的二维可重构CTT中充当电荷俘获功能层。仅仅利用电荷俘获/释放机制,包括高性能非易失存储和模拟突触晶体管在内的器件功能模式可以在运行时通过电学方式编程。通过进一步在不同预设电荷俘获阶段下进行瞬态栅极电压调制,可以实现阈值电压(V

th

)可调的逻辑开关。基于这种器件工作模式,通过以面积高效的单片方式集成可重构的二维CTT,已经构建了高性能逻辑反相器和具有卓越电阻比的非易失三值内容可寻址存储器。凭借所展示的丰富的存内计算器件功能,本文的研究结果表明,经过介电工程的二维可重构晶体管可为未来存内计算架构设计提供功能灵活且高性能的器件概念。

【图文导读】

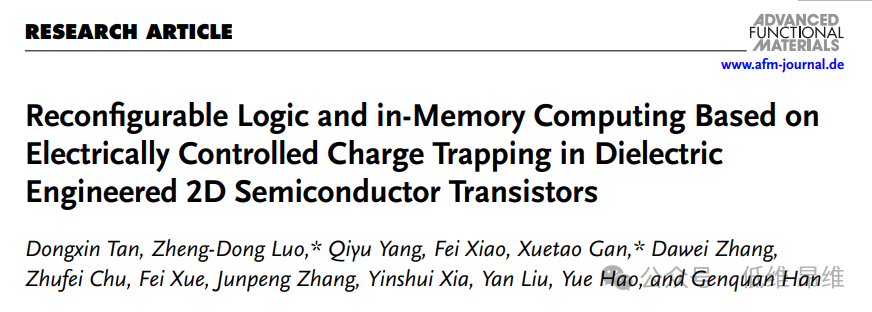

图 1. 可电控的二维电荷俘获晶体管(CTTs)的器件结构和总体概念。二维CTT的示意图说明了电控的电荷俘获和释放效应可以调制二维传输沟道的半导体状态。

图 2. 非易失存储模式下器件的特性。a)二维CTT的示意图。b)器件中MoS

2

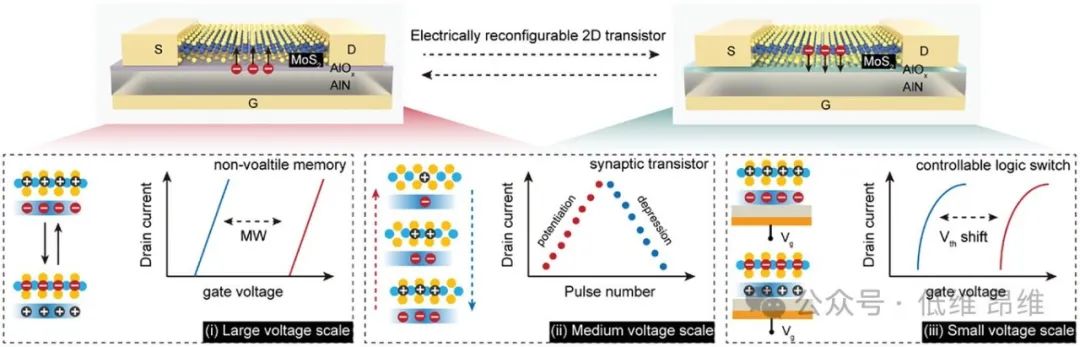

层的拉曼光谱。c)栅极电压幅值从3到8 V(步长为1 V)的二维CTT典型双向扫描传输特性。d)分别在编程和擦除状态下的不同输出曲线。e)通过不同编程栅极电压脉冲设置的器件在各个电导水平上的时间依赖性。f)编程和擦除操作的工作机制示意。

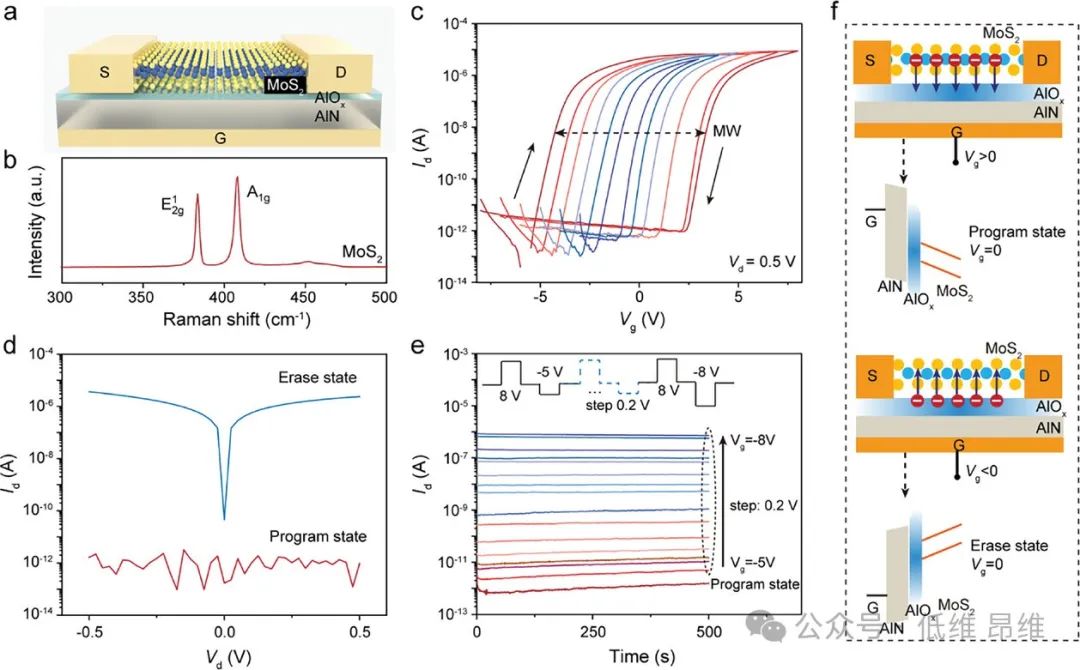

图 3. 阈值电压可调逻辑晶体管和反相器的器件几何结构和电学行为。a)通过电学配置二维CTT实现增强型和耗尽型逻辑晶体管状态的示意图。b)单片集成的二维CTTs的光学图像。c)和d)分别是T1和T2的典型传输特性和阈值电压分布直方图。e)反相器的示意图和电学特性。

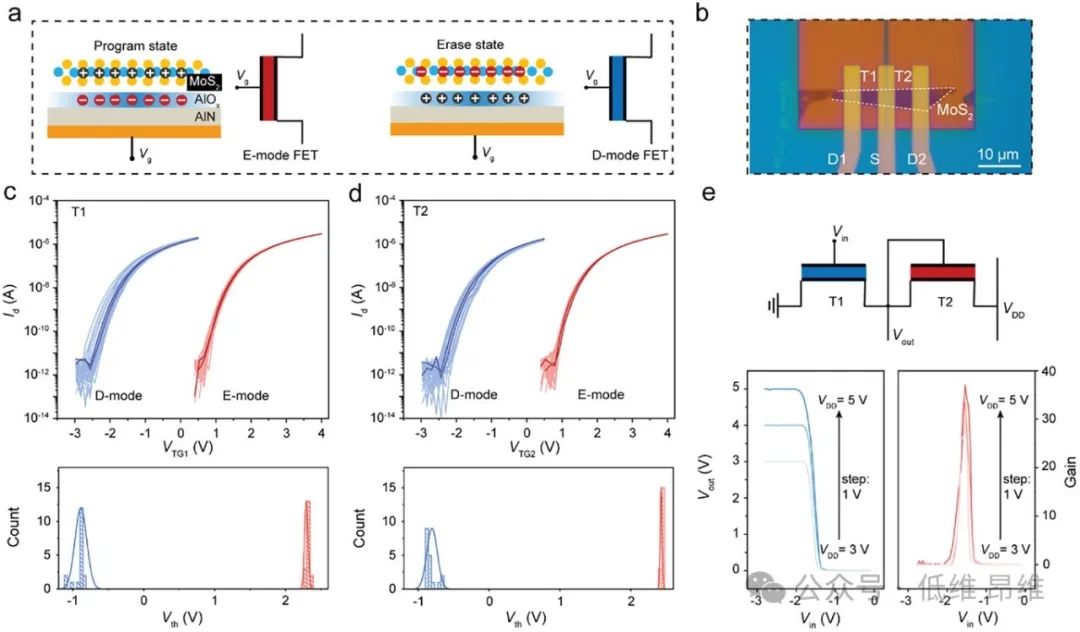

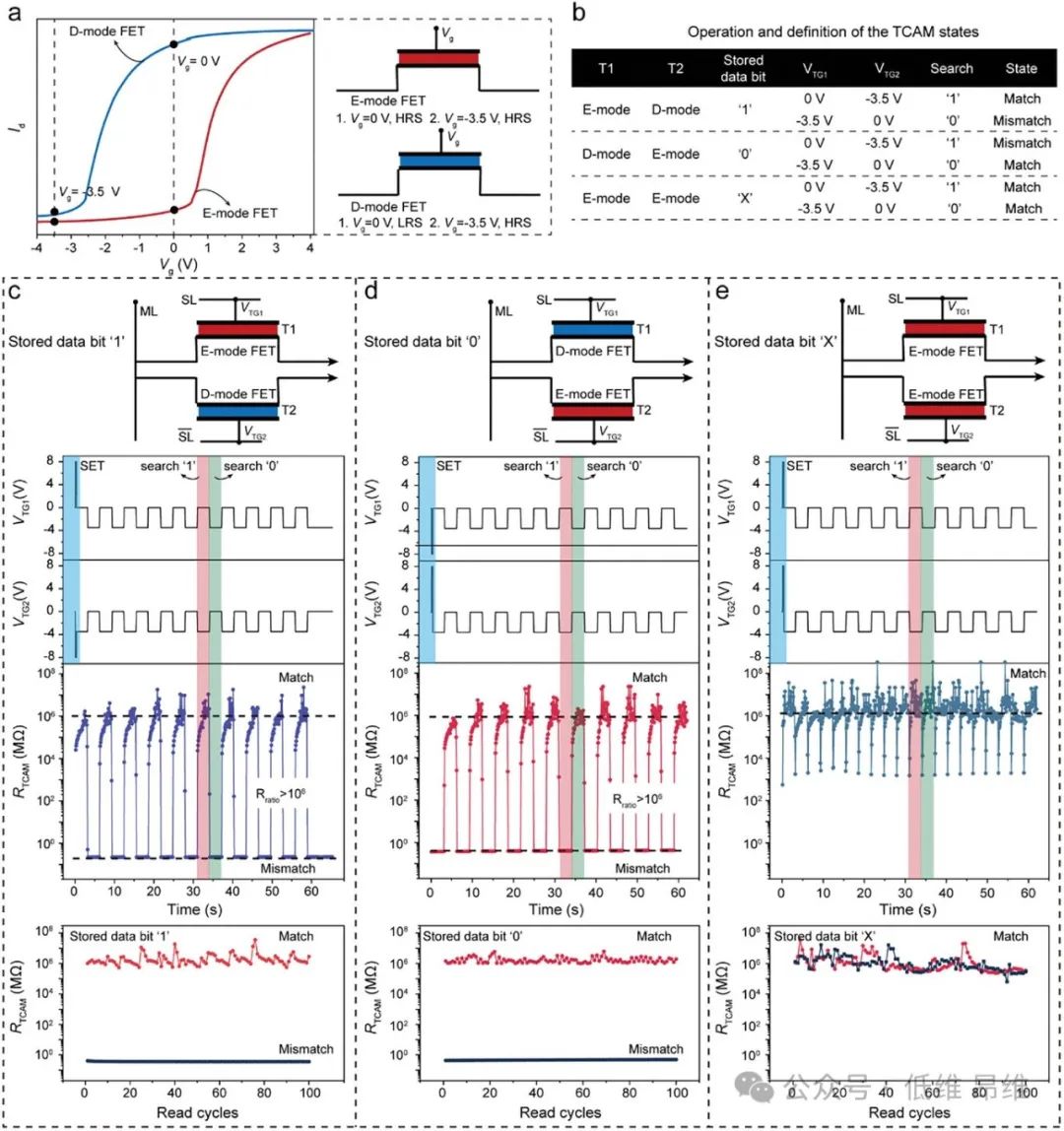

图 4. 用于单片集成非易失三值内容可寻址存储器(TCAM)的可重构二维CTT。a)非易失TCAM的器件概念。b)使用可编程晶体管特性的TCAM状态操作和定义。存储数据位为"1"(c)、"0"(d)和"X"(e)时的TCAM配置和操作。

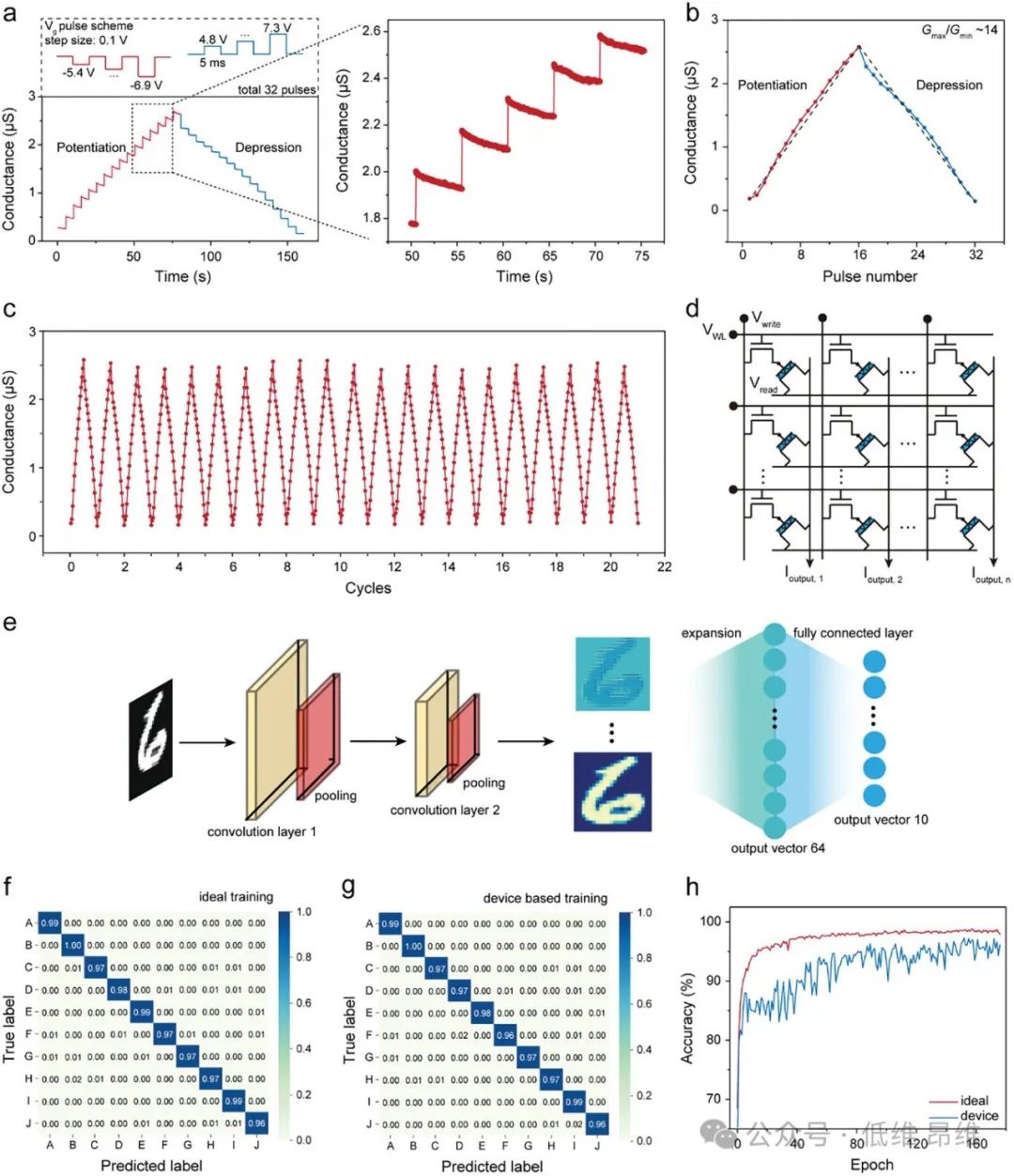

图 5. 可重构二维CTT作为突触器件的性能。a)通过编程栅极电压脉冲控制的突触晶体管的增强和抑制过程。b)作为脉冲数函数的长时程增强(LTP)和长时程抑制(LTD)动力学。c)21个周期的LTP/LTD耐久性测试,对应672个编程电压脉冲。d)使用二维CTT形成的交叉开关阵列的电路图。使用理想机器(e)和基于器件结果(f)的模拟训练混淆矩阵。h)理想机器和基于二维CTT的仿真的训练轮次下的识别准确率演变。

【总结展望】

总之,本工作独特设计的介电工程化二维电荷俘获晶体管(CTTs)展示了面向未来功能灵活、高效的存内计算硬件的运行时电可重构逻辑、非易失存储和人工突触特性。通过与CMOS兼容的混合介电栅极堆叠结构,可以利用电荷俘获/释放效应在二维CTTs中实现各种功能模式。基于动态电荷俘获水平,可以实现阈值电压可调的逻辑开关,从而产生增强型和耗尽型逻辑晶体管以及高性能反相器。通过集成非易失存储和阈值电压可调逻辑晶体管的功能,可以在可控器件模式下将二维CTTs实现为非易失三值内容可寻址存储器(TCAM),体现了紧凑的双晶体管架构。此外,基于模拟电导变化行为,二维CTT还实现了突触晶体管功能模式,能够在系统级别实现卷积神经网络(CNN)的模拟仿真。在单个单元中直接集成运行时电可重构的逻辑、存储和突触功能,对于设计适用于强大存内计算系统的CMOS兼容构建模块极具前景。

【文献信息】

D. Tan, Z.-D. Luo, Q. Yang, F. Xiao, X. Gan, D. Zhang, Z. Chu, F. Xue, J. Zhang, Y. Xia, Y. Liu, Y. Hao, G. Han, Reconfigurable Logic and in-Memory Computing Based on Electrically Controlled Charge Trapping in Dielectric Engineered 2D Semiconductor Transistors.

Adv. Funct. Mater.

2024, 2417887.

文献链接:https://doi.org/10.1002/adfm.202417887

上

海

昂

维

科

技

有

限

公

司

现

提

供

二

维

材

料

单

晶

和

薄

膜

等