为了方便各位同学交流学习,解决讨论问题,我们建立了一些微信群,作为互助交流的平台。2.告知:姓名-课题组-研究方向,由编辑审核后邀请至对应交流群(生长,物性,器件);欢迎投稿欢迎课题组投递中文宣传稿,免费宣传成果,发布招聘广告,具体联系人:13162018291(微信同号)成果介绍

缓存是现代高算力处理器的关键部件,而传统的六管静态随机存储器(6T-SRAM)虽然有着较高的速度,但因其低集成度和高功耗的瓶颈,难以满足日益增长的缓存容量需求。嵌入式动态存储器(eDRAM)凭借其高密度、低功耗的优势广泛应用于三级和四级缓存。然而,传统的“晶体管+电容”结构(1T1C-DRAM)面临破坏性读取、高深宽比电容制造困难以及与逻辑工艺兼容性差等问题。基于增益单元机理的双晶体管eDRAM (2T-eDRAM)完全与CMOS逻辑兼容,但其数据保持时间过短且单元面积大,难以满足高集成度和低功耗应用的严格需求。

近日,复旦大学信息学院万景研究员,联合微电子学院的周鹏教授,包文中研究员团队,合作设计并制造了一种结合硅和MoS2的异质双晶体管eDRAM(Si-MoS2 2T-eDRAM),解决了传统增益单元eDRAM的存储时间过短问题,进一步采用三维异质叠层工艺,实现集成密度的跨越式提升。这种新型结构充分利用了MoS2晶体管的低漏电特性,显著延长数据存储时间(高达6000秒,相比传统DRAM提升1000倍以上),还能实现5纳秒的工作速度,同时结合硅晶体管高开态电流的优点,实现了高感测裕度。该结构通过后端工艺(BEOL)实现MoS2与硅的三维堆叠集成,不仅显著提高集成密度(单元面积最小至8F²,比传统SRAM缩小10倍以上),还完全兼容现有CMOS逻辑工艺。

该技术在存储性能和制造工艺上具有突出优势,为高密度嵌入式存储器技术的发展带来了革命性突破,并为其在高性能处理器中的应用开拓了新的路径。这一研究成果发表在2024年11月的《自然通讯》(Nature Communications)上。

图文导读

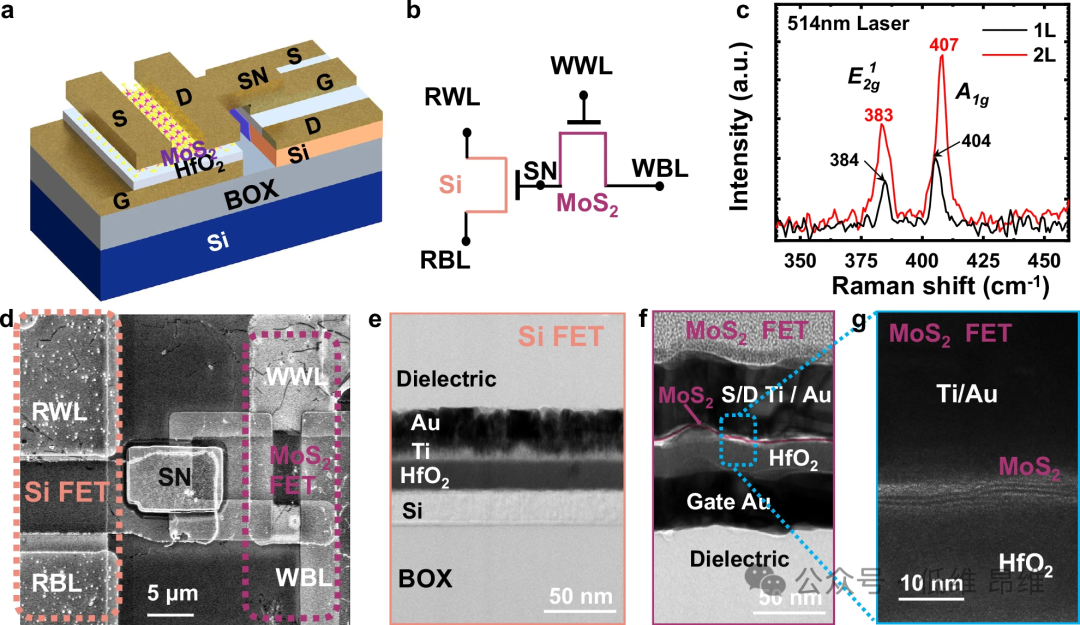

图1. Si-MoS2 2T-eDRAM的示意图和表征。

图1(a)展示了异质2T-eDRAM的三维结构,该器件采用绝缘体上硅(SOI)作为基底与MoS₂异质集成,晶体管均为n型,分别用于读取和写入数据。对应的等效电路图如图1(b)所示。写入晶体管(MoS₂)的源极连接到读取晶体管(Si)的栅极,利用后者的栅电容进行电荷存储。MoS₂晶体管低的关断电流(I_OFF)在确保长时间数据保持中起到关键作用。其栅极作为写入字线(WWL),漏极作为写入位线(WBL)。而基于硅的读取晶体管用于读取存储节点(SN)上的数据,其漏极和源极分别作为读取字线(RWL)和读取位线(RBL)。与传统的1T1C结构不同,2T-eDRAM单元与现有的硅逻辑工艺完美集成,并具备独立的读取和写入功能。监测读取晶体管的输出可在不扰乱SN电荷的情况下判断存储状态。数据保持由MoS₂晶体管的关断电流决定,而存储器的感应裕度则由Si晶体管的开启电流决定。因此,分别使用MoS₂和Si晶体管来实现写入和读取,可以使2T-eDRAM同时实现长数据保持时间和高感应裕度。图1(c)的拉曼光谱显示了MoS₂的两个特征峰:平面内E1₂g振动模式(383.0 cm⁻¹)和平面外A1g振动模式(407.0 cm⁻¹)。E1₂g与A1g峰值间的频率差约为24.0 cm⁻¹,对应于双层(2L)MoS₂,与扫描透射电子显微镜(STEM)表征的结果一致。图1(d)为2T-eDRAM的SEM图像,而标记为橙色和紫色区域的Si和MoS₂晶体管的STEM横截面图分别显示在图1(e)和1(f)中,揭示了具有独特层状结构的双层MoS₂。

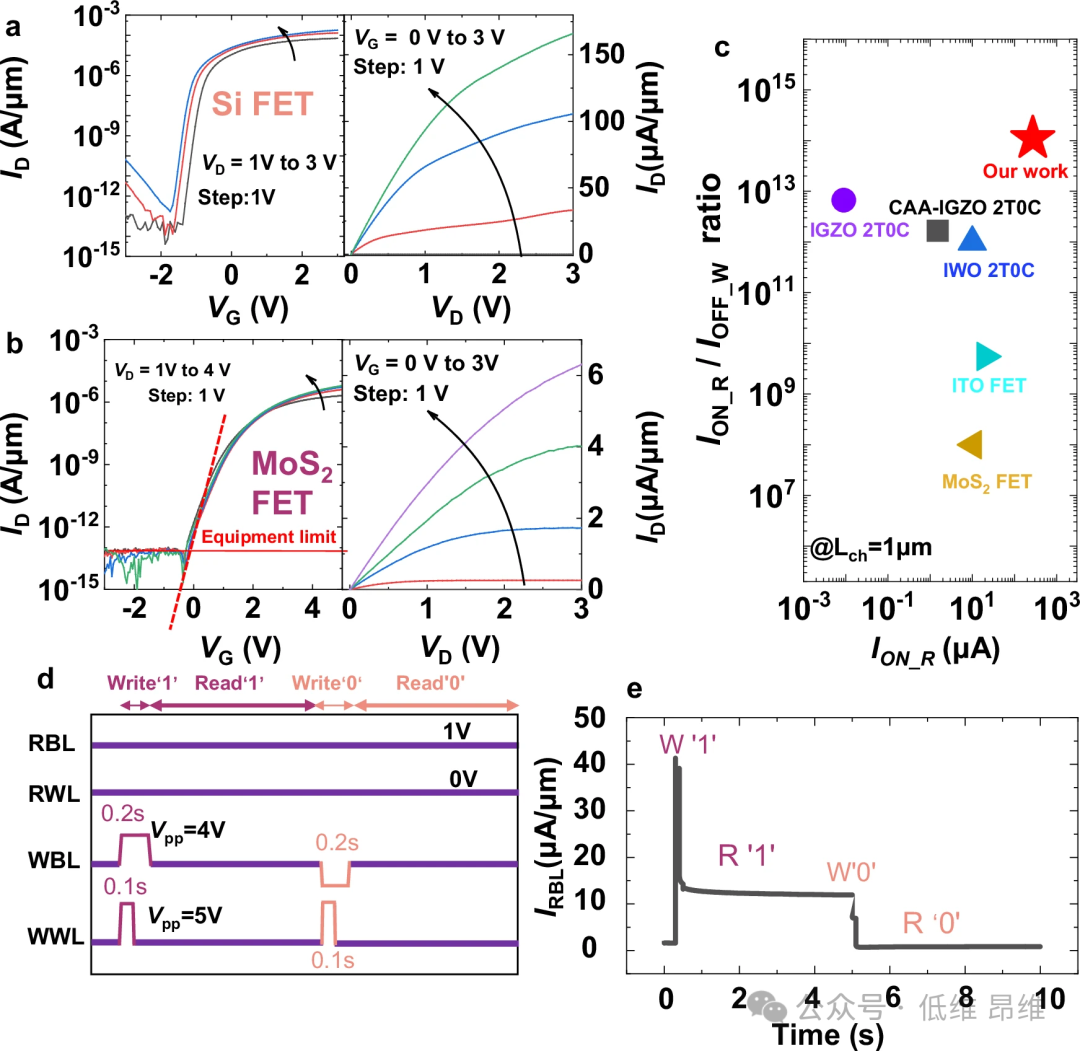

图2. Si读取晶体管、MoS2写入晶体管和异质2T-eDRAM的电学性能。

在器件制造完成后,电气性能测试在室温的环境中进行。图2(a)和2(b)分别比较了相同沟道尺寸(下Si和MoS₂晶体管的转移特性(ID-VG)和输出特性(ID-VD)。两种晶体管的转移特性均表现出优异的开关比(ON/OFF比)。MoS₂ FET即使在高VD偏置下,其关断电流也低于测量设备的下限,如图2(b)所示。两种FET的开启电流分别为6.31 μA/μm(MoS₂)和165.97 μA/μm(Si)在相同偏置条件下。图2(c)对比了异质eDRAM和传统AOS DRAM在读取晶体管开启电流(I_ON_R)及其与写入晶体管关断电流(I_OFF_W)的比值(I_ON_R/I_OFF_W)上的性能。低写入FET关断电流和高读取FET开启电流对于在2T-eDRAM中获得长数据保持时间和大感应裕度至关重要。通过使用Si-MoS₂异质结构,我们在读取FET上实现了280 μA/μm(通道长度和宽度归一化为1 μm)的开启电流,并在I_ON_R/I_OFF_W比值上达到10¹⁴。这显著优于AOS和纯MoS₂ FET。

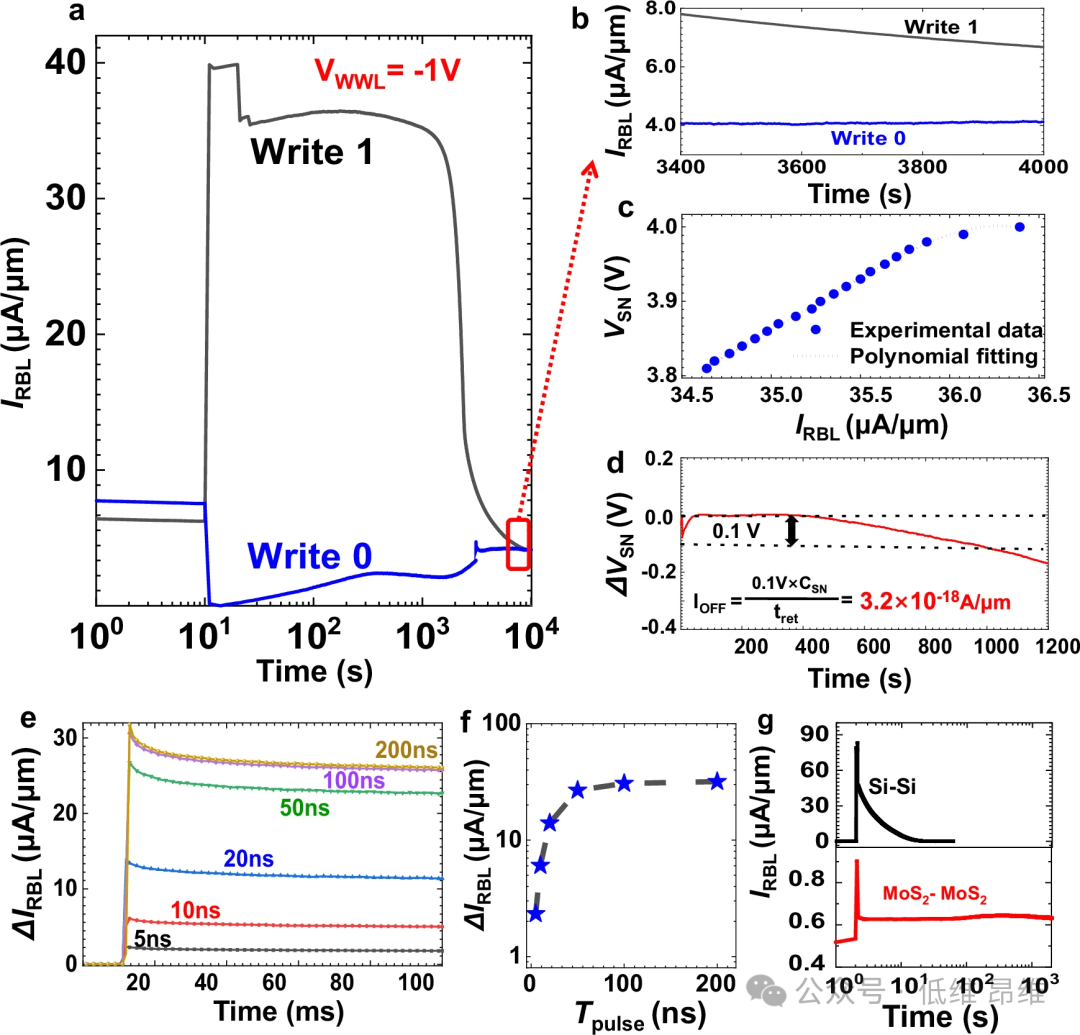

图3. Si-MoS2异质2T-eDRAM具有长时间数据保留和高速访问的优势。

为了评估Si-MoS₂异质2T-eDRAM的存储性能,对数据保持时间、感应裕度和访问速度进行了表征和比较。如图3(a)所示,在写入“1”和写入“0”操作后,IRBL随时间的变化表现出数据保持特性。写入“1”操作后,电荷存储在存储节点(SN)并驱动VSN达到更高的电平。得益于Si读取晶体管的高开启电流,逻辑“1”和“0”之间的感应裕度达到35 μA/μm。高感应裕度有助于放大器区分不同的逻辑状态。逻辑“1”状态的高电流保持稳定直至1000秒,之后迅速下降。传统的AOS-DRAM由于迁移率较低,导致逻辑“0”和“1”状态之间的感应裕度显著减小。图3(b)展示了IRBL随时间变化的细节。在写入“1”操作后,逻辑“1”和“0”状态之间的电流差在3400秒后仍然保持在最大差异的10%以上。通过IRBL的变化推导存储节点电压(VSN)的下降,如图3(c)所示。图3(d)显示了制造的2T-eDRAM的VSN随时间的变化特性。在VSN下降0.1 V作为保持失效判据的情况下,该器件的保持时间超过1000秒,其关断电流约为3.2 × 10⁻¹⁸ A/μm。此外,我们对2T-eDRAM进行了写入速度测试。在理想情况下,存储节点的存储电荷量由写入晶体管的开启电流(I_ON)和写入脉冲时间决定。在5ns写入脉冲后(受测试设备限制),数据“0”和数据“1”的IRBL响应电流差异超过2 μA/μm。得益于Si FET的高感应裕度,在不同写入时间(5至200 ns)下,读取FET的电流水平明显不同,并在整个100 ms测量周期内保持稳定。如图3(e)所示,这种显著的状态差异支持2T-eDRAM具有多级保持能力。图3(f)显示了写入脉冲时间与IRBL变化的关系。随着写入脉冲超过100纳秒,IRBL的变化趋于饱和,这是因为存储节点已经完全充电。与此同时,我们还对由纯Si FET和纯MoS₂ FET组成的2T-eDRAM进行了测试比较,如图3(g)所示。

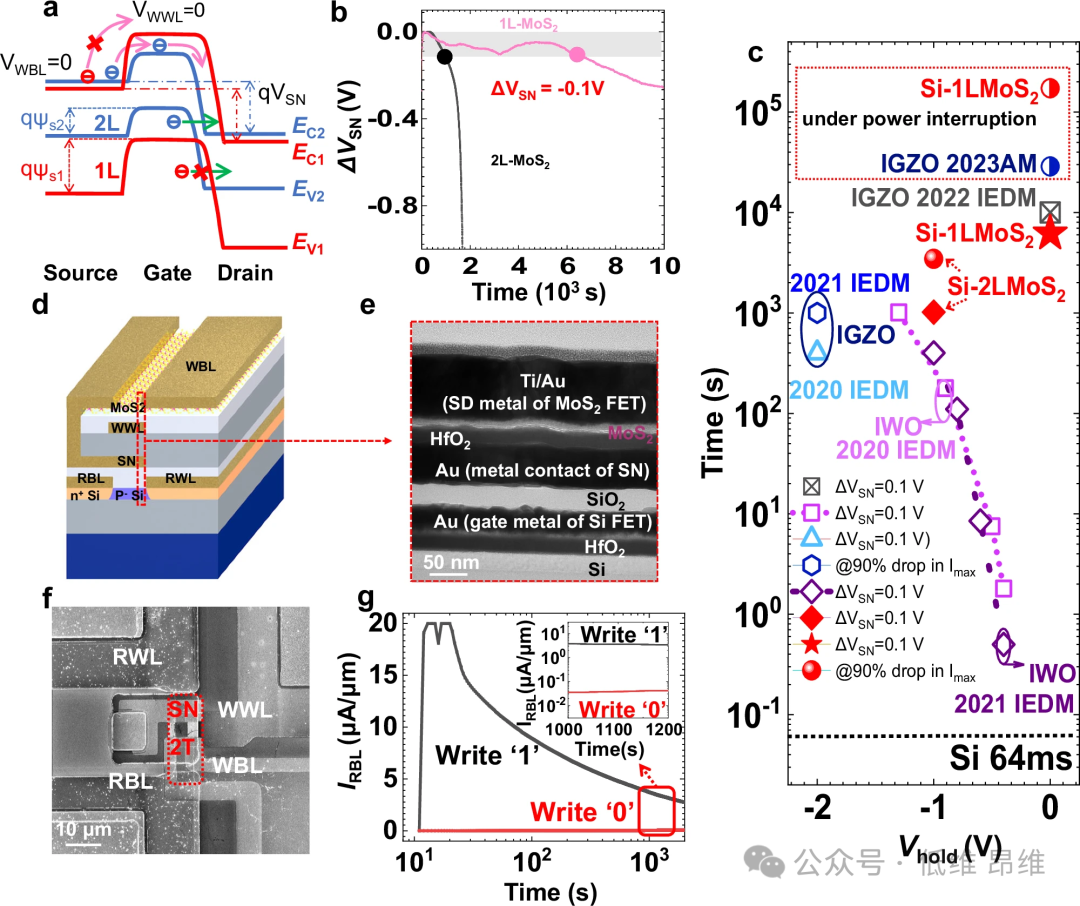

图4. 2T-eDRAM的基准测试和应用潜力。

单层MoS₂由于具有更宽的带隙,可以进一步减少亚阈值和隧穿泄漏电流,如图4(a)所示的能带图所示。以1L-MoS₂作为写入晶体管的沟道材料,其阈值电压(Vth)向右移动,使得异质2T-eDRAM可以在WWL保持为0 V的情况下工作,这显著减少了功耗。此外,与多层MoS₂相比,1L-MoS₂的关断电流更低,使得eDRAM的保持时间更长,如图4(b)所示。如图4(c)所示,我们进一步分析了2T-eDRAM的保持时间与保持电压(Vhold)的关系。在WWL保持为0 V的情况下,使用1L-MoS₂作为写入晶体管沟道材料的DRAM单元表现出近五个数量级的保持时间提升。这一改进显著提高了eDRAM的性能,克服了传统技术的关键限制。图4(d)展示了垂直堆叠3D结构的示意图。在该结构中,在Si读取FET制造完成后,MoS₂写入FET被制造在第一层之上。补充图9详细说明了该器件的制造工艺,其与传统CMOS工艺中的BEOL过程完全兼容。3D Si-MoS₂ 2T-eDRAM单元显著减小了单元面积,从而进一步提高了集成密度。图4(e)和4(f)分别展示了3D堆叠结构的STEM和SEM图像。与并联的异质结构相比,该设计的单元面积大幅减少。图4(g)中显示了垂直堆叠结构的IRBL随时间的变化。即使在状态“0”和“1”之间,感应裕度仍然很高,且IRBL差异在超过1000秒内保持稳定。

文献信息

High performance Si-MoS2 heterogeneous embedded DRAM

(Nat. Commun., 2024, DOI:10.1038/s41467-024-54218-w)

文献链接:https://www.nature.com/articles/s41467-024-54218-w

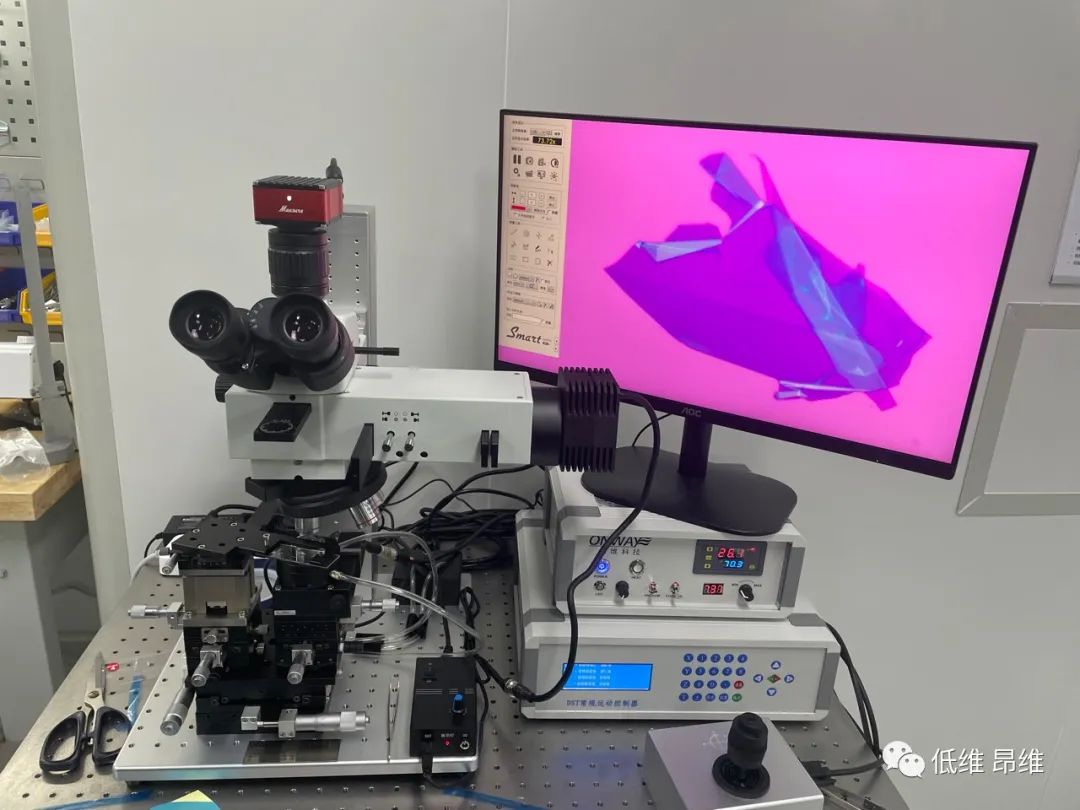

上海昂维科技有限公司现提供二维材料单晶和薄膜等耗材,器件和光刻掩膜版定制等微纳加工服务,以及各种测试分析,欢迎各位老师和同学咨询,竭诚做好每一份服务。