作者:Masoud Beheshti

作者:Masoud Beheshti

电力电子世界在1959年取得突破,当时Dawon Kahng和Martin Atalla在贝尔实验室发明了金属氧化物半导体场效应晶体管(MOSFET)。首款商业MOSFET在五年后发布生产,从那时起,几代MOSFET晶体管使电源设计人员实现了双极性早期产品不可能实现的性能和密度级别。

然而,近年来,这些已取得的进步开始逐渐弱化,为下一个突破性技术创造了空间和需求。这就是氮化镓(GaN)引人注目的地方。

作为一种宽带隙晶体管技术,GaN正在创造一个令人兴奋的机会,以实现电力电子系统达到新的性能和效率。GaN的固有优势为工程师开启了重新考虑功率密度的方法,这些方法在以前并不可能实现,如今能满足世界日益增长的电力需求。在这篇文章中,我将探讨如何实现。

为何选择

GaN

?

当涉及功率密度时,GaN为硅MOSFET提供了几个主要优点和优势,包括:

•

较低的

R

DS

(

on

)

:如表1所示,GaN的MOSFET面积为R

DS

(

on

)

的一半。这直接使电路中传导损耗降低了50%。因此,您可以在设计中使用较小的散热器和更简单的热管理。

|

表1:R

DS(on)

比较

|

|

MOSFET

|

GaN

|

|

R

DS

(

on

)

- 面积公制

|

14-18 mΩ-cm

2

|

6-9 mΩ-cm

2

|

•

较低的栅极和输出电荷:

GaN提供较低的栅极电荷。与MOSFET的4nC相比,典型的中压器件具有大约1nC的栅极电荷(表2)。较低的栅极电荷使设计具有更快的导通时间和转换速率,同时减少损耗。

类似地,GaN具有显著较低的输出电荷(表2),这为每个设计带来双重优势。首先,开关损耗下降多达80%,结合较低的传导损耗,对功率密度有重大和积极的影响。第二,根据拓扑和应用,设计可在更高的开关频率运行高达10倍。这大大减少了磁性材料的尺寸以及设计的尺寸和占用空间,同时将整体效率提高了15%。

|

表2:输出电荷比较

|

|

MOSFET

|

GaN

|

|

栅极电荷

|

~4 nC-Ω

|

~1-1.5 nC-Ω

|

|

输出电荷

|

~25 nC-Ω

|

~5 nC-Ω

|

•

零反向恢复:

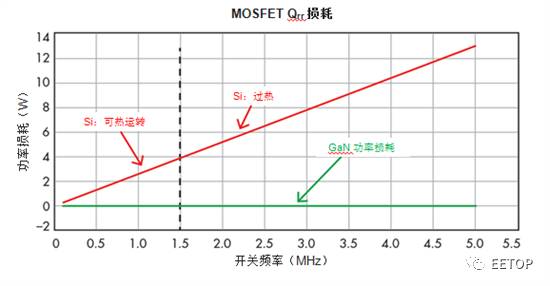

硅MOSFET在50至60 nC范围内具有典型的反向恢复电荷,具体取决于其尺寸和特性。当MOSFET关断时,体二极管中的反向恢复电荷(Qrr)产生损失,从而增加了总的系统开关损耗。这些损耗与开关频率成正比。如图1所示,较高频率下的Qrr损耗使得MOSFET在许多应用中变得不切实际。

1.

相比

GaN

替代品,

MOSFET

的反向恢复电荷(

Qrr

)损耗在较高频率下要大得多。

相比之下,GaN具有零反向恢复和零Qrr损耗,使GaN FET成为硬切换应用的理想选择,如稍后的示例所示。

驱动

GaN

不管所用的GaN类型如何,栅极驱动设计对于实现最佳的整体性能至关重要。一个糟糕的栅极驱动设计的一个很好的类比是在一级方程式赛车上使用街胎。

在设计栅级驱动器时,请注意以下几个关键参数:

•

偏置电压:

重要的是将栅极偏置为最佳电压以获得最佳的开关性能,同时保护栅极免受潜在的过压状况。偏置电平随类型和GaN制造工艺而异,需要相应设置。具有钳位或过压保护电路也极其关键。

•

环路电感:

由于GaN的高压摆率和开关频率,设计中的任何寄生电感都会在系统中引入损耗和振铃。许多电感源存在于GaN FET和驱动器封装中的引线和内部接合线以及印刷电路板(PCB)迹线的设计中。虽然可将其减少,但很难消除它们。诸如

LMG3410

的GaN功率级解决方案将驱动器和GaN FET集成到单个封装中,显著降低了总体电感。

•

传播延迟:

短传播延迟和良好匹配(针对半桥拓扑)对于高频操作非常重要。 25 ns的传播延迟和1到2 ns的匹配是高频(1 MHz或更高)设计的一个很好的起点。

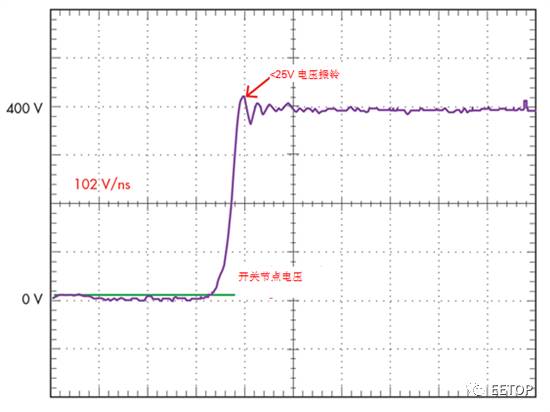

2.

如通过优化的驱动器设计的

GaN

开关波形所证明的,

GaN

可以非常高速的转换速率工作,并且使交换节点上的振铃最小。

通过最佳的栅极驱动设计和PCB布局,您可以非常高的转换速率(> 100 V / ns)运行GaN,使交换节点上的振铃最小。图2所示为这种设计的开关波形的示例。

设计实例:下一代

PFC

解决方案

由于其独特的特性,GaN帮助电源设计人员克服了不同系统和应用中功率密度方面最困难的挑战。这些好处不是来自于在现有设计中简单地将MOSFET替换为等效GaN。GaN使得以前不可能使用硅MOSFET实现的新电路拓扑结构和/或工作模式变为现实。显著的优势导致新一代的产品尺寸更小、效率更高。我们来看一个这样的示例。

功耗因数校正(PFC)在消耗大于75W的每个电气或电子产品中是强制性的。PFC是位于电源和系统其余部分之间的第一个电源转换模块,并在任何给定的工作点承载整个负载。因此,它直接影响整个系统的大小和效率。

已设计出不同拓扑的一代产品,旨在减小尺寸,同时满足行业标准的效率。例如,在80 Plus中定义的效率水平对于钛级电源需要96%的效率。

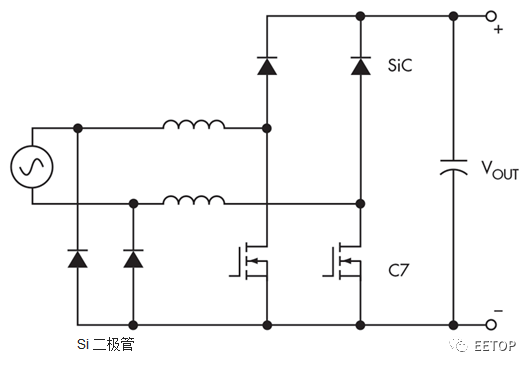

3.

双桥

PFC

拓扑通常用于许多大功率设计。

许多大功率系统(> 1 kW)采用双桥拓扑结构(图3)。随着碳化硅(SiC)二极管和最新一代的超结MOSFET晶体管的引入,我们已经看到过去十年中功率密度方面的改进。然而,这些改进已达到效率和功率密度的停滞期。

功率密度的显著增加需要一种替代方法:

•电源开关的数量

•滤波电感的数量

•电感器的尺寸

•散热片和冷却元件的尺寸

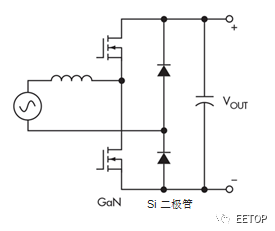

一种替代方案是连续导通模式图腾柱拓扑。这种拓扑结构充分利用了GaN的所有关键特性,最终导致尺寸更小、工作频率更高的设计(图4)。GaN的零反向恢复对于实现该拓扑特别重要。

4.

图腾柱

PFC

拓扑结构在降低工作频率的同时降低设计尺寸,充分利用了

GaN

的零反向恢复。

表3总结了这种无桥PFC设计的几个主要优点,并做了进一步阐述:

•

电源开关:

与双桥拓扑相比,图腾柱PFC替代了两个超结MOSFET和两个仅具有两个GaN器件的SiC二极管。

•

滤波电感器:

该拓扑结构消除了功率级中的一个庞大的滤波电感。电感器的去除及功率开关数量的减少也提高了整体系统的可靠性。

•

尺寸:

由于GaN在高得多的开关频率(通常为40至60 kHz条件下的MOSFET的四倍)条件下工作,您可使用较小的滤波电感。此外,GaN的较低开关损耗使得设计人员能够在功率级中显著缩小散热片的尺寸。

•

效率:

精心设计的图腾柱PFC的高效率达99%以上。为了说明这一点,在整个PFC阶段,1 kW的功耗消耗不到10W。

•

成本:

由于其现有制造成本,GaN器件的溢价将更高。然而,鉴于此处节省的成本,系统总成本应与现有的MOSFET设计相当。

|

表3:PFC 拓扑比较

|

|

双桥

PFC

|

图腾柱

PFC

|

|

功率级开关

|

两个超结FET

两个SiC二极管

|

两个GaN FET

|

|

滤波电感

|

2

|

1

|

|

功率密度

|

40-50 W/in.

3

|

>75 W/in.

3

|

|

效率

|

96%

|

>99%

|

现代图腾柱设计还利用数字功率控制器进一步提高效率,总谐波失真和其他关键设计参数。数字控制器(如C2000和

UCD3138

)可以智能地控制功率级操作,实时优化效率,并响应线路和负载条件。

结论

我们见证了需要更高功率的诸如云计算、5G电信基础设施、风电和太阳能电站及电动和混合动力汽车等行业的日益增长的需求。随着硅MOSFET达到停滞期,设计人员正在探索宽带隙技术,如GaN的下一个设计。

如PFC示例所示,GaN不仅提高了效率,而且将电源的尺寸大大降低了30%至50%。您可以在隔离或非隔离的dc-dc转换器、逆变器和其它电源转换子系统中使用GaN,以显著降低功耗、部件数量、重量和尺寸。(来源:EETOP TI社区)

为了更好地便于大家交流学习,EETOP按区域组建了一些微信群,欢迎所在区域的网友加入各自的区域群,加群方法:

先加 jack_eetop 为好友,发送如下信息:

加群+区域+单位(或院校)+职业

。如果加入的是以省为单位的群,则需按以下格式发送加群信息:

加群+省名+城市名+单位(或院校)+职业

比如: 加群+北京+利达科技+数字IC设计

加群+浙江+杭州+xxx公司+xxx设计

目前先开通如下9个区域群,欢迎对号入座。

长按二维码,加群主为好友,拉你入群

武汉 北京 合肥 苏州 上海

深圳 成都 西安 浙江

(如果不在所在省市,也欢迎加群)

此外,我们也会陆续开通一些行业群,现已开通:

汽车电子 ,

GPU&FPGA深度学习

,

物联网

(行业加群方式: )

欢迎业内人士加入

请按如下格式填写:加群+物联网(或 GPU等)+所在城市及单位

加群前请务必在朋友圈分享至少一篇EETOP的微信文章

点击阅读原文查看更多

点击阅读原文查看更多