为了方便各位同学交流学习,解决讨论问题,我们建立了一些微信群,作为互助交流的平台。

2.告知:姓名-课题组-研究方向,由编辑审核后邀请至对应交流群(生长,物性,器件);

欢迎投稿欢迎课题组投递中文宣传稿,免费宣传成果,发布招聘广告,具体联系人:13162018291(微信同号)

研究背景

布尔逻辑是信息处理的基础,它是由一个叫做开关的单独组件构成的。在CMOS芯片中,开关基本上是一个MOSFET。在过去的半个世纪里,MOSFET的缩放使集成密度、计算能力和固态芯片的经济性取得了进步。然而,FET开关行为的非理想性存在,特别是在亚阈值区域,尽管有栅极控制,但漏极电流呈指数级下降,很像正向偏置二极管。在MOSFET中,开关斜率(SS)传统上由亚阈值斜率(或其倒数,亚阈值摆幅)决定,这是模拟FET弱反转区域的核心参数,对晶体管性能和效率的基准测试至关重要。在玻尔兹曼热离子统计量的控制下,MOSFET在室温(300 K)下具有60 mV/dec的理论极限,这是电源电压(V

DD

)缩放,泄漏控制以及最终功耗的主要限制。几十年来,突破玻尔兹曼极限一直是研究界和工业界实现超低功耗CMOS电子器件的一个活跃的研究主题。具有接近理想开关斜率的逻辑开关是纳米机电场效应晶体管(NEMFET),其SS几乎为零,类似于机械继电器。然而,由于机械磨损,NEMFET存在可靠性问题。在过去的二十年里,在打破玻尔兹曼极限的竞赛中,许多陡坡场效应管被提出并原型化,例如基于非热离子输运(隧穿FET或TFET),栅极工程(负电容FET或NCFET)或非pn结源(狄拉克-源FET或DS-FET)。然而,就亚阈值行为而言,没有一个接近理想的逻辑开关。阈值开关FET(TS-FET)是近年来提出的一种通过导电丝开关和内部放大共同作用而实现突然开关的器件。

成果介绍

有鉴于此,近日,

浙江大学俞滨教授,徐杨教授和张亦舒研究员(共同通讯作者)等展示了一种基于全2D材料范德华异质结(vdW)的场效应管,具有超陡开关(0.33 mV/dec)、大开/关电流比(~10

7

)和超低关电流(~0.1 pA)

。通过功能材料的集体行为实现的“无亚阈值”操作使FET能够直接从关断状态切换到导通状态,完全消除亚阈值区域,充当理想的逻辑开关。本文展示了两英寸晶圆级器件的制造。在器件创新和新兴材料的推动下,这项研究在实现“超越玻尔兹曼”晶体管方面取得了进展,克服了CMOS电子产品中最臭名昭著的技术障碍之一,这一障碍已经困扰了研究界几十年。文章以“

All-2D-Materials Subthreshold-Free FieldEffect Transistor with Near-Ideal Switching Slope

”为题发表在著名期刊

ACS Nano

上。

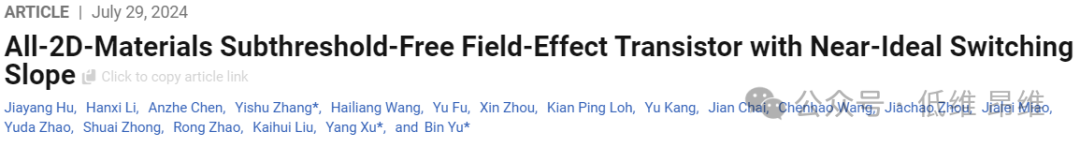

图文导读

图1. 具有近零亚阈值斜率的全2D漏极嵌入式TS-FET。(a)TS-FET结构的示意图。(b)漏极嵌入式TS-FET的等效图。(c)漏极处异质结的横截面TEM图像和能谱图像。(d)TS-FET的光学图像,显示晶体管结构紧凑。(e)从共享同一沟道的TS-FET和MoS

2

基线FET测量的转移曲线。

图1a显示了漏极嵌入式TS-FET的示意图,其中TS与栅控沟道在串行设计中集成。采用少层MoS

2

作为沟道材料,由于其优异的静电性能抑制了短沟道效应,与TS共享多层hBN。这种晶体管结构简化了制作过程,为MoS

2

沟道提供了vdW栅极介质,并为TS提供了稳定的电化学动力学。同时,石墨烯(Gr)被用作漏极/源极接触,促进了载流子注入到2D半导体中,显著消除了钉扎效应。作为一种化学惰性电极,Gr还有助于增强导电丝的自发断裂,确保TS在高顺从电流下具有突然电阻转变的易失性开关。此外,多层Gr作为Ag离子的有效扩散势垒,屏蔽了hBN介质中V

BG

诱导的电场,避免了对TS电化学动力学的干扰。图1b是漏极嵌入式TS-FET的等效电路示意图,可以看作是在漏极侧连接TS的基线MoS

2

FET。漏-源电压(V

DS

)驱动沟道和TS,而栅-源电压(V

GS

)仅直接调制沟道。TS的开关特性由其上的电压控制,对应于串联配置中的单个电阻。TEM横截面图显示2D异质结,EDS成像确定了每层的材料组成(图1c)。TEM图像显示MoS

2

/Gr/hBN异质层界面清晰(图S1),表明hBN厚度小于12 nm,可制成TS-FET。该器件的光学图像如图1d所示。TS-FET和基线MoS

2

沟道FET的转移特性如图1e所示。基线FET具有超低关断电流(<1 pA),高开/关电流比(>10

7

),最小亚阈值摆幅(SS

min

)分别为121.6 mV/dec(正向扫描)和123.9 mV/dec(反向扫描)。相反,全2D TS-FET显示出非常陡的摆幅(SS

min

<0.5 mV/dec),而不影响导通状态驱动电流。

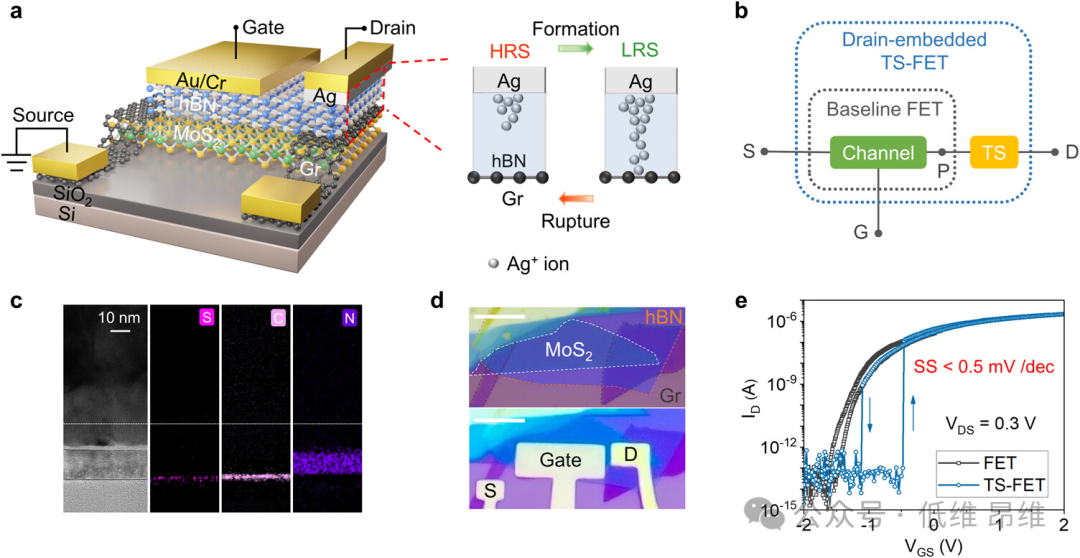

图2. 无亚阈值晶体管的工作原理和性能。(a)与经典FET相比,TS-FET的转移曲线示意图。(b)Ag/hBN/Gr基阈值开关在50个周期(I

cc

:10 μA)下的电流-电压扫描曲线,表明了易失性。(c)TS在恒压采样模式下的电阻开关行为,表明了在较低工作电压下的积分效应。(d)MoS

2

FET在V

GS

从-0.8 V到0 V下的输出特性(I

D

-V

DS

),表现出具有低接触电阻的近线性关系。(e)-0.8~0 V V

GS

下TS-FET的输出特性(I

D

-V

DS

),类似于TS I-V曲线,导通状态电流被沟道电阻箝位。(f)在0.20~0.30 V不同V

DS

下测量的TS-FET前向扫描转移特性。

MOSFET的理想和实际转移曲线示意图如图2a所示。在此,将TS导通时的栅极电压定义为导通电压(V

on

),以区别于传统的阈值电压。V

DS

在串行配置中分为沟道和TS,对应于它们的电阻。亚阈值区域的“阶梯状”电流反映了沟道电阻的主导地位(关断状态沟道电阻R

off-channel

>关断状态TS电阻R

off-TS

)。无亚阈值晶体管是在原始MOSFET的基础上,通过抑制亚阈值电流,将V

on

正推过亚阈值区域,并以陡坡开关电阻的方式建立的。对于理想的亚阈值无晶体管,TS-FET的关断电流(I

off

)最初由沟道决定,并随着沟道电阻减小而增加。同时,TS上的电压降逐渐上升,接近V

DS

,在电阻转变发生之前触发导电丝生长(积分过程)。当导电丝桥接电极时,TS切换到LRS,在向前扫描中引入突然开启。然后,由于超低TS电阻,I

D

遵循基线FET特性,而不会影响驱动电流(I

on

)。在V

GS

=V

on

时,突变发生,其斜率由TS动力学决定。在TS-FET转移曲线中,器件在开关区域(积分后)直接从关断状态切换到导通状态。经典的亚阈值区域不再存在,导致“无亚阈值”操作,就像在接近理想的开关中一样。在反向扫描中,当电压降至接近零时,LRS处的TS趋于关闭。然而,在主通路上的大电流会引起导电丝的进一步横向生长,而在小电流下,导电丝的自发溶解可以主导开关。因此,随着导电丝断裂,I

D

迅速下降,导致陡峭关闭。伴随着导电丝的形成/断裂,TS-FET的迟滞窗口类似于如图1e所示由忆阻效应引起的逆时针转变。全2D TS-FET的亚阈值抑制和陡坡特性归因于TS电化学。对于具有Gr/hBN/Ag结构的TS,Ag纳米颗粒的迁移有助于导电丝的形成和断裂。在电场的促进下,活性电极(Ag)被氧化,生成的阳离子(Ag

+

)向惰性电极(Gr)迁移并被还原,导致纳米颗粒沿扩散路径分布在hBN中。Frenkel-Poole发射和陷阱辅助隧穿过程的结合控制了高阻态(HRS)的电荷输运。当导电丝桥接Gr时,电子通过热离子发射或隧穿在相邻的纳米颗粒之间传输。当电压去除时,导电丝在界面能的驱动下开始自发断裂,TS转变为HRS,并在hBN中随机分布Ag团簇和纳米颗粒。

图2b显示了I

cc

为10 μA时TS的50个周期直流扫描I−V特性。在正阈值电压(V

th-TS

≈0.31 V)下,TS从HRS切换到LRS,此时输出电流突然跳到I

cc

的极限。当电压下降时,TS在保持电压(V

hold-TS

≈0.12 V)下自发返回到HRS,表现出超低的漏电流(<1 pA)。TS在50个周期内表现出稳定的切换,V

th-TS

和V

hold-TS

分布很窄(图S5)。石墨烯作为化学惰性电极,由于其对Ag离子的不渗透性,有利于易失性开关,这有助于在高I

cc

(100 μA)下实现极陡的开/关斜率(<0.2 mV/dec)和大的开/关电流比(>10

8

),有助于在串联结构中实现无损驱动电流和超陡的开关斜率。高质量的机械剥离hBN层提高了TS的HRS,大大抑制了全2D TS-FET的亚阈值电流。与之前的报道相比,由于导电丝生长的集成,TS可以在测量的V

th-TS

以下打开(图2c)。

全2D TS-FET通过集成TS、用抑制的亚阈值电流修改主通路的输出电流和导电丝主导的电阻开关来实现无亚阈值行为。对于本文的器件,MoS

2

沟道在不同的V

GS

下具有近似线性的输出特性,表明了与Gr的欧姆接触(图2d)。超薄层状hBN提供了vdW界面,很大程度上抑制了MoS

2

中光声子诱导的载流子散射,从而通过多层hBN介质实现了对MoS

2

沟道的强静电调制。由于TS与沟道串联,全2D TS-FET的输出曲线(图2e)可以认为是串联恒定电阻的TS的开关特性。一旦TS切换到LRS,输出电流由MoS

2

沟道决定。随着V

DS

减小,导通电压正移,显示出TS的积分效应(图2f)。V

on

的移动也被观察到依赖于电压扫描速率。因此,优化TS与沟道之间的电阻匹配对于实现大开关比至关重要。迫切需要具有大HRS的TS来抑制亚阈值电流,而强沟道调制对于串联(R

off-channel

>R

off-TS

)下TS的关断也是至关重要的。全2D TS-FET显示出超低的SS

min

(<0.5 mV/dec)。值得注意的是,晶体管利用TS中的快速电阻跃迁以亚阈值抑制导通。因此,SS

min

能够对TS-FET的性能进行基准测试。

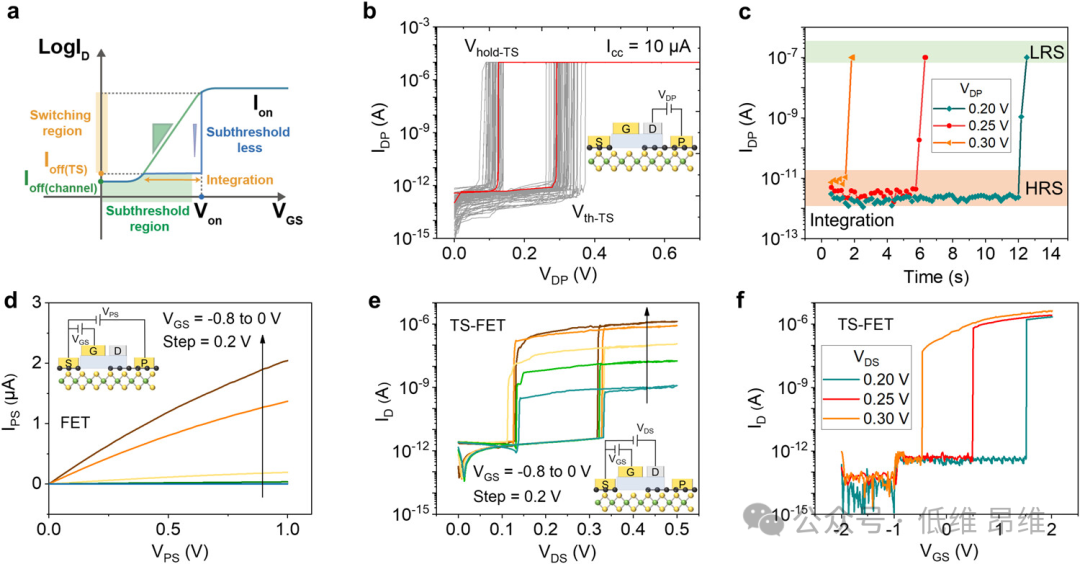

图3. 全2D TS-FET的导通电压正移。(a)不同沟道调制的TS-FET转移特性的示意图。(b)不同V

DS

下TS-FET和MoS

2

FET的转移曲线。(c)20个周期内V

on

分布与FET亚阈值区域的对比。(d)不同V

DS

下TS-FET和MoS

2

FET的转移曲线。(e)在20个周期(强沟道调制)中,V

on

分布与FET亚阈值区域的对比。(f)V

on

与MoS

2

FET开关斜率(SS

FET

)关系的模拟。

通过将TS串联到MoS

2

沟道,利用导电丝的突变电阻转变来改变主通路上的电流。在全2D TS-FET中,这两个元件的协同作用促进了具有亚阈值电流抑制和陡坡特性的高效开关动力学。一方面,TS的集成有助于实现无亚阈值特性。另一方面,沟道对TS的控制涉及到V

on

向电源电压(V

DD

)的正移,进一步增强了待机功耗降低。仅受TS随机变化的限制,可以将V

on

推至接近V

DD

,此时晶体管直接从关断状态切换到导通状态。因此,增大的V

on

、陡峭的SS和抑制的亚阈值区域协同作用有助于TS-FET的低功率工作。本文研究了不同沟道调制方式下TS-FET的电学性能。顶栅诱导的沟道调制决定了积分的起点,由底栅电压V

BG

继续。对于本文的器件,由于vdW界面的hBN电介质,当V

BG

=0 V时实现了强沟道调制。在背栅施加大电压(V

BG

=30 V)以减弱沟道调制,导致I

off

从1 pA增加到1 nA。如图3a所示,与V

on

正向移动的强调制相比,TS-FET倾向于在前向扫描中以弱调制更早地导通。图3b显示了全2D TS-FET和MoS

2

FET在不同V

DS

下弱调制的转移曲线。低的关断状态沟道电阻不能承担大部分的V

DS

,因此高电阻的TS在低V

TG

时开始积分。在这种情况下,积分TS有助于比MoS

2

FET降低I

off

。当沟道失去对TS的控制时,TS上的电压接近V

DS

。有效的V

DS

被限制在V

th-TS

以下,以保证正常工作,避免在没有集成的情况下立即打开TS。Von的变化遵循TS固有的随机性,图3c给出了20个周期内V

on

的分布,证实了弱沟道调制的TS-FET倾向于在亚阈值区域导通。因此,由于线性/饱和区域消耗的动态功率保持不变,TS-FET的陡峭开关在实现低功率方面是无效的。此外,积分时间随着V

DS

减小而延长,由于导电丝的形成涉及随机离子动力学,增强了V

on

的变化。相反,大的关断状态沟道电阻可以有效地将TS关断,控制输出电流达到TS关态电流时的压降和积分起点。换句话说,除了改变外部电压幅值外,可以通过改变积分起点来传递V

on

。图3d显示了全2D TS-FET和MoS

2

FET在不同V

DS

下的转移曲线。如图3e所示,在强调制下,V

on

的分布向V

DD

的分布靠近。为了帮助V

on

的正移动,有效的V

DS

被限制在V

th-TS

以下,这表明TS-FET具有低功率工作的潜力。简而言之,全2D TS-FET有望通过超陡的转变直接从关断状态切换到导通状态(饱和区),从而抑制亚阈值区和线性区消耗的动态功率。全2D结构增强了静电调制,便于电阻匹配,实现了优异的性能。

为了进一步了解沟道的作用,本文进行了各种沟道调制的TS-FET模拟。基线场效应管(SSFET)的亚阈值斜率与V

on

的关系如图3f所示。提取SS

FET

对沟道调制进行基准测试,当TS上的压降仍然得到控制时,V

on

随SS

FET

增加而减小。对于较小的SS

FET

,积分起始点正向移动,导致延迟导通。当沟道失去控制时,由于漏极电压完全施加在TS上,V

on

显示各种SS

FET

几乎没有偏移。简而言之,结合实验和仿真,沟道对TS的控制对于实现受抑制亚阈值行为的突然开关至关重要。

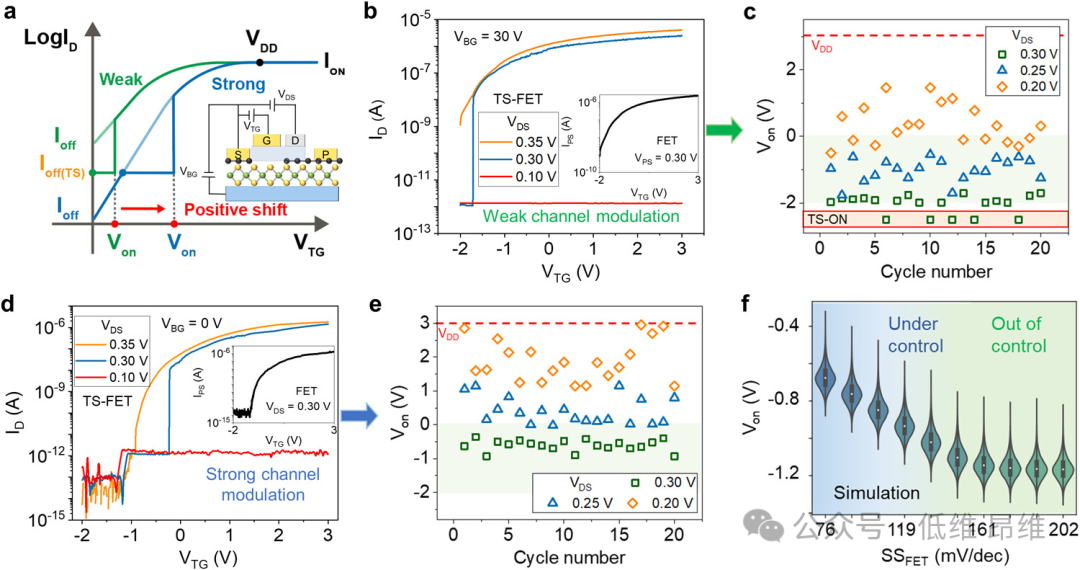

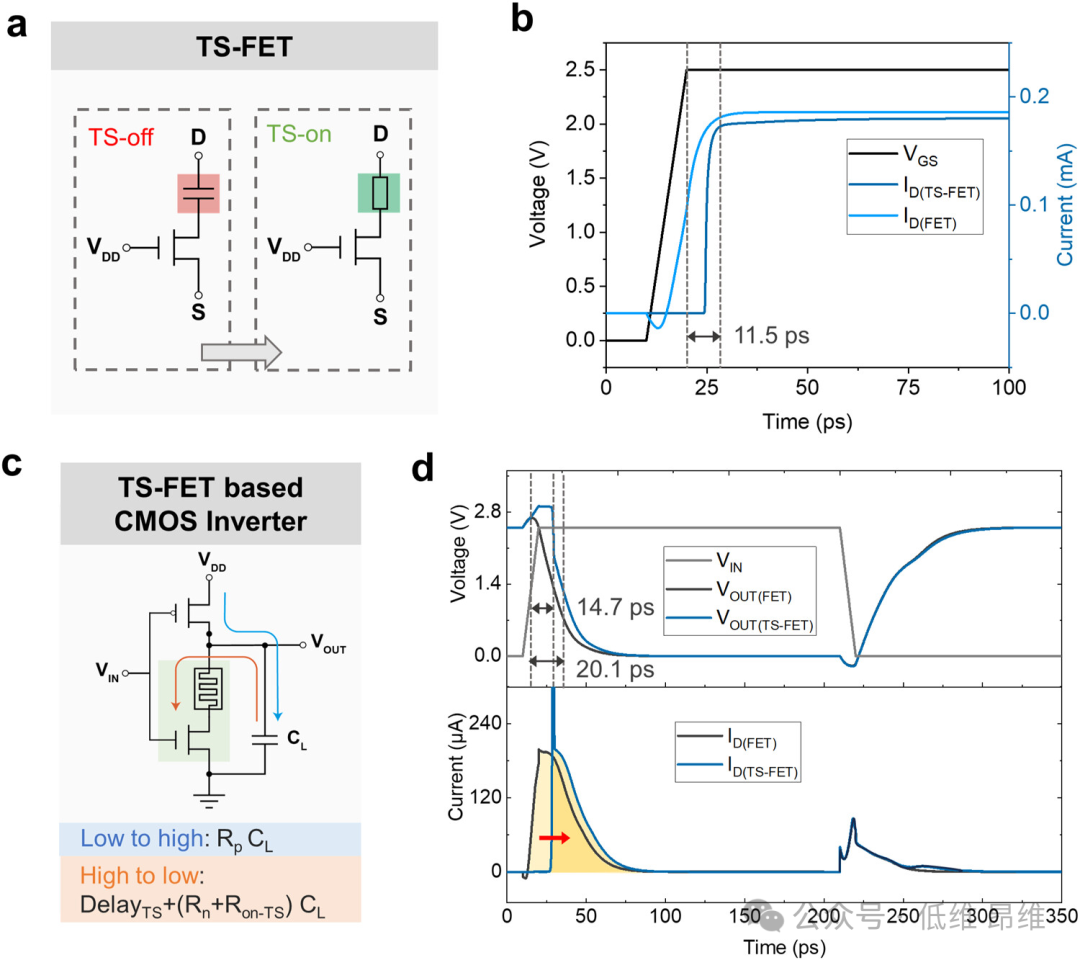

图4. 无亚阈值FET及其CMOS反相器的开关动力学仿真。(a)在开关过程中TS-FET的等效电路图。(b)栅极和漏极电源电压作用下TS-FET的动态响应。(c)TS-FET基CMOS反相器的等效电路图,显示负载电容C

L

的充放电情况。(d)TS-FET基CMOS反相器与基准CMOS反相器的动态响应比较,显示出低动态功率下延迟的高到低转换。

低耗散器件对固态电路是必不可少的。通常,更陡的SS和更低的关断状态电流使电源电压可以缩放,实现低功耗器件工作。逻辑开关的总开关能量(E

total

)由动态和静态两部分组成。然而,传统基于独立载流子动力学的推断并不适用于具有集体行为的TS-FET。本文的TS-FET结合了多种功能材料,在TS电化学动力学和沟道场效应动力学的基础上呈现出集体响应。虽然表征的SS降低了,但与原始基线FET相比,电源电压保持不变。因此,基于隔离测量的降低SS的低功率工作主张将是无效的,而需要对工作功率进行必要和系统的分析,以重新评估TS-FET的节能工作潜力。本文分析了无亚阈值FET及其CMOS反相器的动态响应。首先,该器件的等效电路方案在栅极和漏极处施加电源电压(图4a)。在关断状态下,TS被认为是连接在主路上的额外电容,在导通状态下被认为是一个电阻。TS在达到其阈值电压时开始充电,与沟道电阻的指数下降平行。定制的脉冲序列分别应用于栅极和漏极,以测量开关时间。第一个脉冲用于检查TS是否处于关闭状态,第二个脉冲用于切换TS-FET。观察到器件在电容充电期间导通,实际导通时间估计小于310 ns。本文模拟了TS-FET的动态导通行为,与基线FET相比,显示出快速响应而没有明显延迟(图4b)。由于空间分离结构,栅极电容充放电引起的动态延迟与串联电阻无关。忆阻器的开关速度为10 ps,因此TS与沟道的集成对器件响应速度的影响可以忽略不计。为了支持无亚阈值FET在逻辑运算中的实际可用性,本文构建了基于n型TS-FET和基线p型FET的CMOS反相器(图4c)。反相器的暂态响应受负载电容(C

L

)的充放电影响。因此,将TS嵌入到NMOS模型中会造成过大的延迟,特别是在从高到低的转换期间。响应延迟的相应估计如图4c所示。与基准CMOS反相器相比,延迟的响应延迟归因于TS在关断状态下的开关时间和导通状态下TS电阻的延迟放电。本文构建了CMOS反相器的仿真(图4d),表明由于TS的集成,产生了从高到低的传播延迟时间,从14.7 ps延长到20.1 ps,忆阻器的开关时间对延迟CMOS反相器的响应速度起着至关重要的作用,已被证明可以降低到ps级,这表明了本文的器件在高速集成电路工作中的潜力。同时,电压转换过程中的直接传导电流被显著抑制,导致动态能耗从6.8 fJ降低到4.1 fJ,降低了三分之二。反相器的开关行为在低到高的转换过程中保持不变,这归因于反向扫描中缺乏无亚阈值特性。此外,通过将亚阈值电流从μA抑制到pA,使反相器的待机功率降至零,提高了总能效。