随着芯片的集成度增加,物联网等新应用带动的多样化需求增长,在集成电路的设计中,验证变得越来越重要。在过去,集成电路工程师把验证称之为买保险,因为一个集成电路的设计周期非常长,且流片成本极大,如果没有验证,最后出错了,就会造成不可弥补的损失。

Cadence公司全球副总裁石丰瑜先生则认为,验证更像是健康体检,在不可挽回的结果出现之前做好一切,防患于未然。总之就是在现在的集成电路设计中,验证不可或缺。

Cadence公司全球副总裁石丰瑜

集成电路越来越复杂,验证迎来新挑战

在集成电路的设计中,验证的存在就是为了确保所设计电路功能的准确性,具体的方式可以通过软件仿真和硬件仿真。软件仿真很直观,简单来说就像调试软件程序,在这个过程中,参与者可以看到每一时刻的状态;而硬件仿真一般就是指FPGA验证,也就是说把电路用FPGA来实现,验证电路。

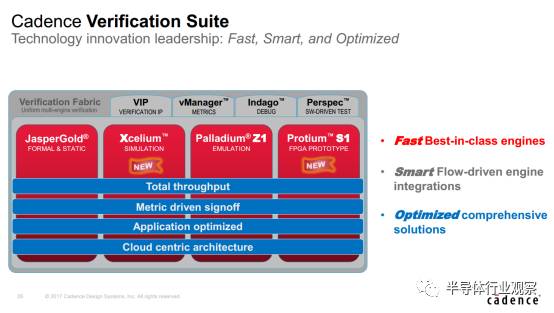

Cadence公司认为,2017年的验证有两大趋势:首先是改善用于验证的核心引擎,包括形式验证、仿真、硬件加速仿真和以FPGA为基础的原型验证,提高速度、容量和资源利用率;其次,智能化验证应利用核心引擎,更合理的制定验证任务的执行方式和引擎组合。而在核心引擎之后,并行仿真也将成为2017年的主流趋势。

而伴随着SoC的尺寸和集成度增加,验证面临新挑战,历经三十年发展的仿真迈进了一个新时代。

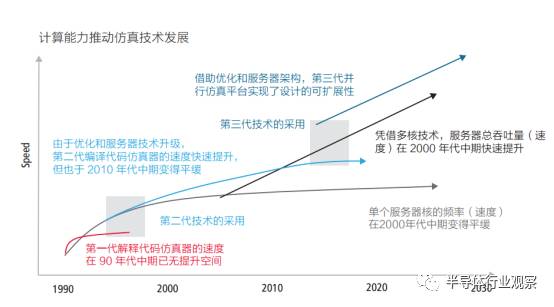

计算能力推动方针技术的发展

根据石丰瑜先生介绍,从以上世纪八十年代Verilog-XL 和 RapidSim 等编译代码仿真器为代表的第一来商业化仿真技术算起,仿真技术能管理了三代的发展。

据了解,第一代仿真器的工作机制是先编译成p代码再将其执行,因此运行速度极为缓慢,但是对当时的小型设计来说,已经足够了;

到了九十年代中期,随着综合技术的出现,设计规模变大,就出现了编译代码仿真器满足设计对速度、容量的要求,这是第二代仿真器。这时候的仿真器的工作原理是在运行仿真之前,将源代码转化为机器代码。自其出现以来,就一直是业界主流的仿真器,它们实现了对 e、 SystemC® 、 SystemVerilog、 CPF 和 UPF 等多种新标准的支持。然而,随着设计尺寸变得越来越庞大,越来越复杂,第二代仿真技术已经无法满足市场需求。这就推动了第三代仿真器的面世。

“现在的芯片包含的门很多,数百万级别,且有各样的组合;再者,随着物联网等便携设备的逐渐流行,功耗成为了验证的关键;加上芯片平台跑了很多OS,很多软件,这就给芯片的验证带来新的需求,为了保证越来越复杂产品的质量,验证平台要进步,仿真也要更新”,石丰瑜告诉半导体行业观察的记者。

为了适应SoC尺寸的增长和复杂度的提升,仿真技术也在迅速发展。最近出现的并行仿真正是这样一种通过加快测试速度来提高验证效率的技术。在并行仿真技术的新时代中,工程师再也无需担忧验证会成为瓶颈了。

三代仿真技术

Cadence全新平台解决验证之难

为了帮助IC验证工程师解决验证之难,Cadence公司推出了全新的验证平台,助力集成电路产业的发展。

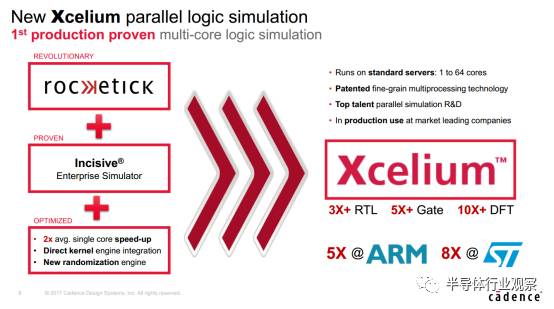

首先,Cadence推出了业界首个第三代的并仿真平台Xcelium。

Cadence公司系统与验证事业部产品管理与运营副总裁Michal Siwinski

据Cadence公司系统与验证事业部产品管理与运营副总裁Michal Siwinski先生介绍,新一代的仿真平台Xcelium是基于上一代的Incisive仿真平台,结合Cadence早前收购的Rocketick公司的技术开发的。较Cadence上一代仿真平台,Xcelium单核版本性能平均可提高2倍,多核版本性能平均可提高5倍以上。在寄存器传输级(RTL)仿真可平均提速3倍,门级仿真可提高5倍,DFT仿真可提高 10倍,节约项目时间达数周至数月。

从介绍中我们得知,Cadence Xcelium仿真平台已经在移动、图像、服务器、消费电子、物联网(IoT)和汽车等多个领域的早期用户中得到了成功应用,并通过产品流片验证。支持标准多核服务器(多达 64 核)且采用获得专利的细粒多进程技术, Xcelium 可以将编译代码仿真平台上运行的仿真分解成可加速和不可加速两个部分。可加速的部分(如门级网标或 SystemVerilog RTL 部分)由并行引擎处理,验证工程师无需改变测试平台、设计或断言。 Xcelium 在语言层运作,因此不依赖于工艺节点,也无所谓设计是一个 CPU、处理器,还是一个数据通路设计。此外,设计层次也不会造成影响。

对于新平台的推出是否会给开发者带来操作指令的相关问题,根据Cadence方面介绍,第三代平台的指令和上一代的指令基本是完全继承,只需要在名称上做一些小改变,就能完全契合新需求。

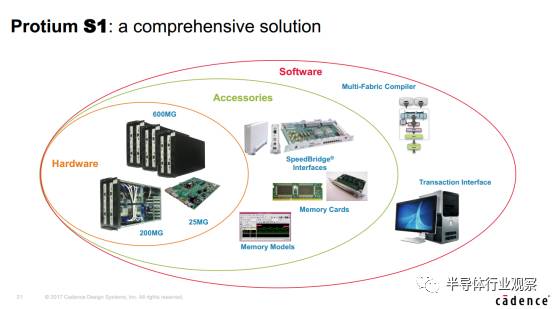

基于FPGA的原型验证平台Protium S1是Cadence的另一个杀手锏。

Michal Siwinski指出,Protium S1采用Xilinx Virtex UltraScale FPGA技术,设计容量比上一代平台提升6倍,性能提高2倍。

而从Cadence的相关介绍中我们可以看到,Protium S1与Cadence® Palladium® Z1企业级仿真平台前端一致,初始设计启动速度较传统FPGA原型平台提升80%。这个平台更可以确保多至数以百计的软件开发者在开发流程的最早阶段,就能专注于设计验证和软件开发,而不仅仅是原型验证。

Protium S1提高初启时间

值得一提的是,Protium S1不是一个单一的解决方案,Cadence方面不但提供单板、单机架系统、多机架配置的硬件选择,很提供了包括配件和软件在内的多种选择,帮助开发者提升设计效率,保证产品质量。

Protium S1的多样化解决方案

作为一个全球领先的EDA工具提供商,Cadence的解决方案当然并不止这两种,他们提供了包括JasperGold®形式化验证工具、Xcelium™并行仿真平台、Palladium®硬件仿真加速器以及Protium™ FPGA原型验证平台核心引擎在内的一个套间,另外还在套间中囊括了验证IP、Perspec™测试、vManger™指标与Indago™调试等多引擎验证架构,全方位解决IC验证中的问题。

芯片的验证从来没有那么复杂。而从某个角度看,在Cadence们的努力下,芯片的验证也越来越简单。你们准备好拥抱新时代了吗?

今天是《半导体行业观察》为您分享的第1271期内容,欢迎关注。

关注微信公众号 半导体行业观察,后台回复关键词获取更多内容

回复 A股,看《A股知名芯片公司盘点,你更看好哪家?》

回复 CPU,看《CPU制造全过程,一堆沙子的艺术之旅》

回复 挣钱,看《最会挣苹果钱的中国半导体公司》

回复 IGBT,看《中国IGBT真的逆袭了吗?》

回复 禁运,看《对中国禁运的那些先进设备和技术》

回复 打破垄断,看《中国半导体在三个领域打破了国外垄断 》

回复 产业链,看《半导体产业链最全梳理,建议收藏》

回复 泪流满面,看《二十个让IC工程师泪流满面的瞬间》

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“半导体行业观察icbank”微信公众号。谢谢合作!

【关于征稿】:欢迎半导体精英投稿(包括翻译、整理),一经录用将署名刊登,红包重谢!签约成为专栏专家更有千元稿费!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号 MooreRen001或发邮件到 [email protected]

【关于征稿】:欢迎半导体精英投稿(包括翻译、整理),一经录用将署名刊登,红包重谢!签约成为专栏专家更有千元稿费!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号 MooreRen001或发邮件到 [email protected]

点击阅读原文加入摩尔精英