近十多年来

数字集成电路和各种接口总线标准的发展

令人

眼花

缭乱

,

目

不

暇接

各个总线标准通常由不同团队制订

其纷繁芜杂的测试和测量技术

给从业人员带来许多困扰

对于一个硬件设计工程师而言

由于相对参考设计的系统重新设计和降成本的需求

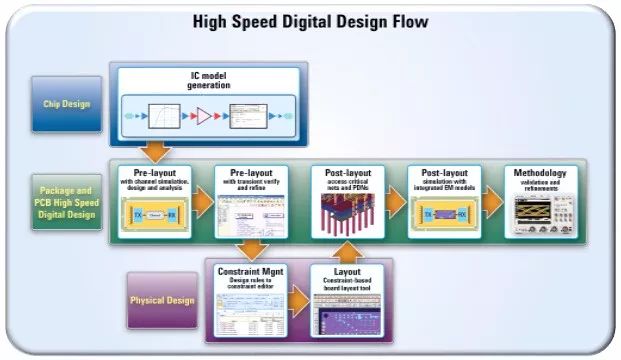

仿真与设计相结合已经变得越来越不可或缺

鉴于此,本系列文章将就

当下高速数字电路和信号的仿真设计及

测试技术发展趋势

作一些简明的总结和说明

1

与传统的单端并行总线不同,近

10

年来串行差分信号正在成为数字电路与系统中的主流,基本已经完全统治接口总线。在消费类电子领域

,

目前最高的总线速率是

Thunder Bolt3

接口,达

20Gbps.

在数据通信与传输骨干系统,目前采用

25Gbps

的

NRZ

编码的差分信号已经成熟,更高速率如

56Gbps

的传输则会采用

PAM-4

编码实现。

今天的差分信号主要有如下特点:

近几年,为了实现更高传输带宽,比如

PCIExpress

即

100G/200G/400G

传输中,也会采

用多链路以实现大带宽,因此针对多链路串行差分总线,串扰测试也开始成为一个新的课题。

而新的课题不仅只有一个

各种新技术、新标准层出不穷

凭借自己的实战设计经验

已经难以跟得上

电子产品发展的速度

而利用设计仿真,迭代经验,重塑设计规则

将成为工程师们的必然选择

点击下载,了解本文全部内容

助您掌舵

高速数字电路仿真设计

精准把脉测试技术发展

▼