(点击查看

第一章节选

)

内容简述:

本文选自第二章第一节,《集成电路工艺、闩锁效应和

ESD

电路设计》第二章分六节,第二节到第六节的内容暂时不会公开。第二章第二节到第六节的内容分别是:第二节

. Hard Mask

(硬光罩)工艺制程技术、第三节

.

热载流子注入效应(

HCI

)与

LDD

结构、第四节

. Polycide

和

Salicide

(自对准硅化物)工艺制程技术、第五节

. ESD IMP

(静电保护离子注入)工艺制程技术、第六节

.

平坦化以及金属(

AL

和

Cu

)互连工艺制程技术,这部分的内容都包括目前这些工艺集成在实际晶圆生产工艺流程中的应用,通过实际应用让大家快速的掌握实际的工艺集成技术。

第一节内容主要介绍集成电路隔离技术的发展过程,集成电路隔离技术从最初的

PN

隔离技术发展到

LOCOS

和

STI

隔离技术。

虽然PN结隔离技术工艺制程简单、成本低、成品率高,但是利用PN结隔离技术制造的集成电路集成度非常低,结电容大和高频性能差,并且它会引起CMOS自身固有的寄生PNP和NPN导通,它们之间会形成正反馈机制导致电源与地之间形成PNPN的低阻通路,电源与地之间产生大电流烧毁CMOS集成电路,这就是CMOS电路的闩锁效应,所以它并不适合制造比较先进的、高密度的CMOS。PN结隔离技术只被广泛应用于低成本的TTL集成电路。

为了改善利用PN结隔离技术制造的集成电路集成度低、结电容大和闩锁效应等问题,20世纪70年代半导体研发人员在LOCOS的基础上开发出LOCOS隔离技术方案。LOCOS隔离技术与PN结隔离技术非常类似,实际上LOCOS隔离技术就是把PN结隔离技术中的PW保护环换成氧化物,LOCOS隔离技术是PN结隔离技术的副产物,氧化物能很好地隔离器件,降低结电容,同时改善闩锁效应和寄生NMOS等问题。但是LOCOS隔离技术存在两个问题,鸟嘴效应和白带效应,鸟嘴效应严重影响了利LOCOS结隔离技术制造的集成电路集成度,白带效应效应会影响栅氧化层的击穿电压。20世纪80年代末期,研究人员发现LOCOS隔离技术还是不能满足高密度的集成电路的要求,因为最先进的LOCOS隔离技术的最小隔离距离大概是0.6u,LOCOS场氧的鸟嘴向每个方向的横向凹进的宽度是0.3u,所以LOCOS最小的器件与器件的距离是1.2u,它严重影响集成电路的集成度。由于存在鸟嘴效应,LOCOS被只被广泛应用于工艺特征尺寸0.3

µ

以上的CMOS和BiCMOS技术。

为了解决LOCOS隔离技术的鸟嘴效应和白带效应,研究人员在LOCOS的基础上开发出STI隔离技术方案,但是早期STI隔离技术的工艺集成也面临一些问题,例如早期在没有CMP(Chemical Mechanical Polishing)全局平坦化技术的时候,需要光刻和刻蚀去除多余的氧化物,并且产品良率非常低,早期的STI隔离技术并不适合用于实际集成电路生产。1983年,IBM发明了CMP技术,CMP技术的出现为STI隔离技术的实用化开辟了道路,1994年,CMP技术被应用于STI隔离技术的实际生产中。STI隔离技术与LOCOS隔离技术非常类似,只不过STI是采用凹进去的沟槽结构,它场区的氧化物不是通过热氧化生长的,而是采用HDP CVD(High Density Plasma CVD)的方式淀积的SiO

2

,所以STI隔离技术可以解决鸟嘴效应和白带效应。由于STI隔离技术的器件密度非常高,STI隔离技术被广泛应用于工艺特征尺寸在小于0.3u的集成电路。

《集成电路工艺、闩锁效应和

ESD

电路设计》一共五章内容,第一章介绍集成电路工艺制造技术的发展过程,第二章介绍工艺集成,第三章介绍主流的集成电路工艺制程技术,第四章介绍闩锁效应,第六章介绍

ESD

电路设计。未来我们会节选《集成电路工艺、闩锁效应和

ESD

电路设计》剩下章节的部分内容进行发布。

目前本书处于前期推广阶段,图书还没有正式出版,预计两到三个月后会出版。如果对本文或者《集成电路工艺、闩锁效应和

ESD

电路设计》有兴趣可以联系编著者本人或者负责本书的出版社。

第二章:

典型工艺

2.1

隔离技术

---------------------------------------------------------------------------------------------

(发表)

2.1.1 PN

结隔离技术

----------------------------------------------------------------------------

(发表)

2.1.2 LOCOS

(硅局部氧化)隔离技术

-----------------------------------------------------

(发表)

2.1.3 STI

(浅沟槽)隔离技术

----------------------------------------------------------------

(发表)

2.2 Hard Mask

(硬掩膜版)刻蚀技术

--------------------------------------------------------------

(暂时不发表)

2.2.1

硬掩膜版简介

---------------------------------------------------------------------------------

(暂时不发表)

2.2.2

硬掩膜版的应用

-----------------------------------------------------------------------------

(暂时不发表)

2.3

热载流子注入效应(

HCI

)与

LDD

结构

--------------------------------------------------

(暂时不发表)

2.3.1

热载流子注入效应简介

---------------------------------------------------------------

(暂时不发表)

2.3.2 LDD

结构的工艺应用

-------------------------------------------------------------------

(暂时不发表)

2.4 Polycide

和

Salicide

(自对准硅化物)技术

----------------------------------------------

(暂时不发表)

2.4.1Polycide

和

Salicide

简介

---------------------------------------------------------------

(暂时不发表)

2.4.2Polycide

的工艺应用

-------------------------------------------------------------------

(暂时不发表)

2.4.3Salicide

的工艺应用

--------------------------------------------------------------------

(暂时不发表)

2.5 ESD IMP

(静电保护离子注入)技术

------------------------------------------------------

(暂时不发表)

2.5.1 ESD IMP

简介

-----------------------------------------------------------------------------

(暂时不发表)

2.5.2 ESD IMP

的工艺应用

------------------------------------------------------------------

(暂时不发表)

2.6

后段平坦化以及金属(

AL

和

Cu

)互连技术

------------------------------------------------

(暂时不发表)

2.6.1

后段平坦化

------------------------------------------------------------------------------

(暂时不发表)

2.6.2 AL

互连技术

-------------------------------------------------------------------------------

(暂时不发表)

2.6.3 Cu

互连技术

-------------------------------------------------------------------------------

(暂时不发表)

2.1

隔离技术

半导体集成电路是通过平面工艺制程技术把成千上万颗不同的器件(如电阻、电容、二极管和MOS管等)制造在一块面积非常小的半导体硅片上,并按需要将它们连接在一起,形成具有一定功能的电路。集成电路工作时,集成电路里的各个器件的电压是不同的,必须要对它们之间进行相互绝缘隔离,保证器件之间不相互干扰,每个器件的工作都是独立的,从而实现电路的功能。隔离技术是半导体集成电路的关键,它决定了集成电路的性能和器件的密度。最初商业化的隔离技术是PN结隔离技术,它是利用PN结反向偏置时呈高电阻性,来达到相互绝缘隔离的目的。PN结隔离技术工艺制程比较简单,成品率高,价格便宜,但是利用PN结隔离技术制造的集成电路的密度非常低,它只被广泛应用于低成本的TTL集成电路。由于利用PN结隔离技术制造的集成电路集成密度非常低,并且如果利用PN结隔离技术制造CMOS集成电路,集成电路中寄生的NPN和PNP会形成正反馈导致PNPN的低阻通路导通形成闩锁效应,烧毁CMOS集成电路,所以它并不适合制作比较先进的、高密度的CMOS和BiCMOS集成电路。为了得到更好的隔离和更高的器件密度,后来半导体工程人员研发出LOCOS(Local Oxidation of Silicon硅的局部氧化)隔离技术。由于利用LOCOS隔离技术制造的集成电路能实现较高的器件密度,所以LOCOS隔离技术被广泛应用于工艺特征尺寸0.30

µ

以上的CMOS和BiCMOS集成电路。随着集成电路制造技术不断发展,LOCOS隔离技术并不适用于制造器件密度远大于10

7

cm

-2

的CMOS集成电路,20世纪80年代出现了STI(Shallow Trench Isolation浅沟槽)隔离技术,由于利用STI隔离技术制造的集成电路能实现非常高的器件密度,所以STI隔离技术被广泛应用于特征尺寸0.30

µ

以下的CMOS集成电路。

2.1.1PN

结隔离技术

为了理解PN结隔离技术,以最早出现的双极型集成电路为例,先了解双极型工艺制程技术流程,再通过双极型集成电路去分析PN结隔离技术。

双极型工艺制程技术流程主要包含以下八大主要步骤:

第一步、准备P型衬底硅(P-type-Substrate P型衬底);

衬底的掺杂浓度一般是10

15

cm

-3

,晶向是(100)的轻掺杂P型硅。低的掺杂浓度可以减小集电极的结电容,提高集电极的击穿电压。

第二步、形成NBL(N-type-Burrier-Layer N型埋层);

首先在P型衬底上生长一层二氧化硅作为阻挡层,再进行光刻和刻蚀处理,露出需要形成NBL埋层的区域,然后淀积N型杂质砷,通过退火使杂质扩散到衬底,同时激活砷离子,最后通过湿法刻蚀清除二氧化硅层。在N-EPI外延层和Psub衬底之间制作中等掺杂的NBL埋层,目的是减少双极型晶体管集电极的串联的电阻和减小寄生的PNP管的影响。

第三步、生长N-EPI(N-type-Epitaxy N型外延层);

外延生长一层轻掺杂的N型外延硅,作为双极型晶体管的集电极,整个双极晶体管便是制作在这层N型外延层上的。为了减小结电容和提高击穿电压BVcbo,外延层必须是轻掺杂的。

第四步、形成PW保护环隔离;

生长一层二氧化硅作为阻挡层,再进行光刻和刻蚀处理,露出需要形成PW保护环的区域,然后淀积P型杂质硼,通过退火使杂质扩散到所需的结深,同时激活硼离子,形成PW保护环。PW保护环的结深要大于N型外延层的厚度,这样可以通过PW保护环隔离可以形成许多N型外延的孤岛,它们便是通过PN结隔离技术进行隔离的。电性上利用反偏的PN结实现双极型晶体管的电性隔离,因为反偏的PN漏电流非常小。最后通过湿法刻蚀清除二氧化硅层。

第五步、形成重掺杂DNW(Deep-N-Type-Well)集电极;

生长一层二氧化硅作为阻挡层,再进行光刻和刻蚀处理,露出需要形成集电极的区域,然后通过离子注入N型杂质磷,并退火激活磷离子,形成N型重掺杂DNW集电极,目的是减少双极型晶体管集电极的串联的电阻。最后通过湿法刻蚀清除二氧化硅层。

第六步、形成NPN基区(P-base);

生长一层二氧化硅作为阻挡层,再进行光刻和刻蚀处理,露出需要形成基区的区域,然后通过离子注入P型杂质硼,通过退火激活硼离子,形成P型轻掺杂P-base基区。为了减小结电容,提高击穿电压BVcbo,提高电流增益,P-base与DNW和NBL不能重合,P-base基区必须是轻掺杂。最后通过湿法刻蚀清除二氧化硅层。

第七步、形成NPN发射极和集电极接触;

生长一层二氧化硅作为阻挡层,再进行光刻和刻蚀处理,露出需要形成发射极和集电极接触的区域,然后通过离子注入N型杂质砷,通过退火激活砷离子,形成N型重掺杂发射极和集电极接触。最后通过湿法刻蚀清除二氧化硅层。

第八步、形成基极和PW接触。

生长一层二氧化硅作为阻挡层,再进行光刻和刻蚀处理,露出需要形成基区和PW接触的区域,然后通过离子注入P型杂质硼,通过退火激活硼离子,形成P型重掺杂基区接触。最后通过湿法刻蚀清除二氧化硅层。

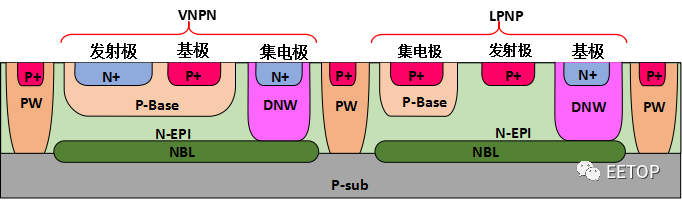

上面的工艺流程是前段器件级的工艺,如图2.1所示是双极型集成电路的剖面图。当前段工艺完成以后,在器件上淀积一层二氧化硅绝缘层,目的是把器件和互连的金属隔离,然后进行光刻和刻蚀,形成接触孔,并淀积金属层,接着进行光刻和刻蚀,形成互连线。

图2.1双极型集成电路剖面图

为了有效的隔离双极型集成电路各个器件,双极型集成电路各个PN结都是反偏的,保证PN结维持反向偏压是必不可少的,这种利用反偏PN结做器件隔离的技术在1959年首次获得专利,它是最早实用化的器件隔离技术。为了追求芯片商业利润的最大化,设计人员都希望两个器件做的尽量靠近,这样可以缩小单个芯片的面积,同时单位面积的硅片可以产出更多的芯片,提高晶圆的利用率。

以双极型集成电路中两个相互靠近的NPN为例,NPN的集电极DNW与PW保护环或者NBL和P型衬底的PN结是反偏的,它们会建立起一个的势垒高度,形成耗尽层。当相邻的两个NPN集电区相互靠近时,它们的耗尽层也相互靠近时,势垒高度开始减小,电子就更容易越过这个势垒形成漏电流,那么相邻的器件的集电极相互之间就会形成漏电流,增加了集成电路的功耗。同时它也影响了器件的隔离效果,所以相邻的器件间会有有一个最小的安全距离。因为PW保护环是轻掺杂的,DNW是重掺杂的,当N-EPI与PW保护环的耗尽区接触到DNW时,DNW与PW保护环的PN结表现为单边突变结,轻掺杂的PW保护环耗尽层的宽度会变大。当Psub偏置电压是0V时,当两个NPN的集电极分别加5V和3V电压时,两个NPN集电区的耗尽区距离会相互靠近,如图2.2所示是相邻的两个NPN集电极分别加5V和3V电压时的剖面图,灰色的区域是耗尽层,它与DNW、PW保护环和E-EPI层的掺杂浓度有关。它们的隔离效果除了与它们的偏置电压有关,也与DNW、PW保护环和E-EPI层的掺杂浓度有关。当NPN的集电极偏置电压越大时,PW耗尽层的宽度也越大,那么相邻器件的隔离距离会随着耗尽层宽度的增大而减小。为了达到比较好的隔离效果,工作电压越大的芯片,器件相互间的隔离距离也要越大,也就是PW保护环的宽度也要越大。也可以通过提高PW保护环的掺杂浓度,来减低PW保护环耗尽层的宽度,从而达到减小器件相互间的隔离距离的目的,但是提高PW保护环的掺杂浓度会间接增大集电区和PW保护环的寄生电容,从而影响双极型集成电路的工作速度,所以考虑集成电路器件密度的同时也需要对集电极和PW保护环的寄生电容做折衷考虑。

图2.2 NPN耗尽层宽度变化的剖面图

对于一个典型的集电区掺杂浓度为10

16

cm

-3

,P型衬底掺杂浓度为10

15

cm

-3

的双极型工艺制程技术,考虑到横向杂质的横向扩散距离大概4um左右,PW保护环的宽度是8um,对于10V偏压的NPN器件,集电区之间的间距可能需要12um。

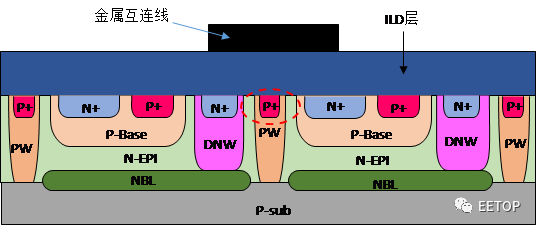

除了考虑简单的隔离以外,还要考虑高压电路的寄生的场效应管问题。当金属线在两个NPN之间PW保护环的上方横向跨过时,它们就会形成寄生的场效应晶体管NMOS,相邻的两个NPN的集电区为该寄生NMOS的源和漏,金属线是栅,如图2.3所示。如果金属线的电压足够大,那么该寄生NMOS就有可能导通开启,那么原本隔离的两个NPN就可能漏电。而且它们之间的漏电流与NPN的集电区的距离是没有关系的,就算它们间距非常远也可能形成寄生NMOS导通漏电,只要有金属线从它们上方横向跨过,并且金属线的电压足够大。寄生NMOS的阈值电压与PW保护环的浓度和ILD(Inter Lay Dielectric)氧化层的厚度有关,为了提高寄生NMOS的阈值电压,可以提高PW保护环的浓度,但是提高PW保护环的浓度会增加集电区与Psub衬底的寄生电容,所以提高PW保护环的浓度的方法并不是最好的选择,那么就要考虑增加ILD氧化层的厚度去提高寄生NMOS的阈值电压,这个方法是最可取的,而且不会发生其它的效应。

图2.3 寄生的NMOS的剖面图

PN结隔离技术工艺制程简单,成本低,成品率高,并且能有效实现了双极型集成电路的平面隔离。但是PN结隔离技术集成电路集成度非常低,结电容大和高频性能差,并且利用PN结隔离技术制造CMOS集成电路时,它会引起CMOS自身固有的寄生PNP和NPN导通,并且它们之间会有正反馈机制导致它们之间会形成低阻通路的PNPN闩锁效应结构,产生电源与地之间的大电流烧毁CMOS集成电路,所以它并不适合制造比较先进的、高密度的CMOS和BiCMOS集成电路。PN结隔离技术只被广泛应用于低成本的TTL集成电路。

2.1.2LOCOS

(硅局部氧化)隔离技术

为了改善利用PN结隔离技术制造的集成电路集成度低、结电容大和闩锁效应等问题,20世纪70年代半导体研发人员在LOCOS的基础上开发出LOCOS隔离技术方案。LOCOS隔离技术与PN结隔离技术非常类似,实际上LOCOS隔离技术就是把PN结隔离技术中的PW保护环换成氧化物,LOCOS隔离技术是PN结隔离技术的副产物,氧化物能很好地隔离器件,降低结电容,同时改善闩锁效应和寄生NMOS等问题。LOCOS被广泛应用于工艺特征尺寸0.3

µ

以上的CMOS和BiCMOS技术。

为了更好的理解LOCOS隔离技术,先简单介绍一下LOCOS隔离技术的工艺流程,它主要包括以下步骤:

第一步生长前置氧化层(PADOxide),缓冲Si

3

N

4

层对衬底的应力;

第二步生长Si

3

N

4

,它是场氧化的阻挡层;

第三步有源区AA(Active Area)区域光刻处理和刻蚀;

第五步场区氧化,形成硅局部场氧化物隔离器件。

第六步湿法刻蚀去除Si

3

N

4

。

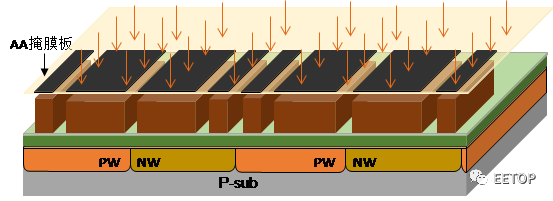

LOCOS工艺流程如图2.4~图2.13所示。

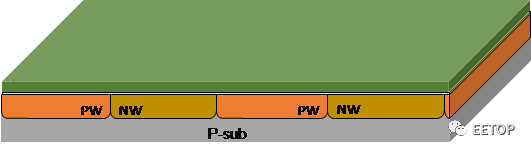

1.

选取已经完成PW和NW离子注入的集成电路为初始步骤。图2.4是PW和NW的剖面图。

图2.4 PW和NW的剖面图

2.

淀积前置氧化层。利用常压化学气相淀积(APCVD- Atmospheric Pressure Chemical Vapor Deposition),在高温H

2

O或O

2

的环境中形成一层SiO

2

薄层,称为前置氧化层,厚度约150Å~250Å。淀积前置氧化层的目的是缓冲Si

3

N

4

层对衬底的应力,因为衬底硅的晶格常数与Si

3

N

4

的晶格常数不同,直接生长Si

3

N

4

会在衬底中形成应力,如果应力超过衬底硅的屈服强度就会在衬底硅中产生位错。较厚的氧化层可以有效的减小Si

3

N

4

层对衬底的应力。图2.5是淀积前置氧化层后的剖面图。

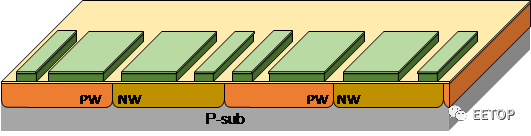

图2.5前置氧化层的剖面图

3.

淀积Si

3

N

4

层。利用低压化学气相淀积(LPCVD–Low Pressure CVD),淀积一层厚度约1500 Å~1700 Å的Si

3

N

4

层,它是场氧化的阻挡层。图2.6是淀积Si

3

N

4

层后的剖面图。

图2.6 Si

3

N

4

层的剖面图

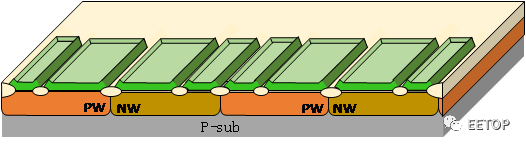

4.

淀积SiON层。利用LPCVD淀积一层厚度约200Å的SiON层,作为光刻的防反射层。图是2.7 是淀积SiON层后的剖面图。

图2.7 SiON层的剖面图

5.

涂光刻胶。图2.8是涂光刻胶后的剖面图。

图2.8 涂光刻胶的剖面图

6.

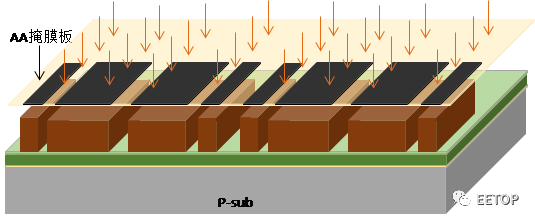

AA光刻处理。通过光刻(曝光、显影、坚膜等工序)将AA掩膜板(mask)上的图形转移到光刻胶上,定义出AA区域,AA区域上保留光刻胶。图2.9是AA光刻的剖面图。

图2.9 AA光刻的剖面图

7.

AA干法刻蚀。利用热H

3

PO

4

与Si

3

N

4

反应去除晶圆上的Si

3

N

4

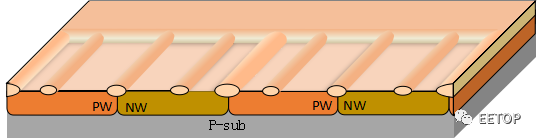

,最终形成AA图形。图2.10是AA干法刻蚀的剖面图。

图2.10 AA干法刻蚀的剖面图

8.

去除光刻胶。利用干法刻蚀和湿法刻蚀去除光刻胶,干法刻蚀利用O

2

燃烧分解大部分光刻胶,然后湿法刻蚀利用H

2

SO

4

&H

2

O

2

与光刻胶反应去掉残留的光刻胶。图2.11是去除光刻胶后的剖面图。

图2.11去除光刻胶后的剖面图

9.

淀积LOCOS场氧化物。利用APCVD淀积场氧化物,在高温H

2

O或O

2

的环境中生长一层厚度为4000Å~4300Å的SiO

2

层,作为LOCOS隔离的氧化物。Si

3

N

4

阻挡了氧化剂的扩散,使Si

3

N

4

下面的硅不被氧化,Si

3

N

4

的顶部也会生长出一层薄的氧化层。图2.12是生长场区SiO

2

的剖面图。

图2.12生长场区SiO

2

的剖面图

10.去除Si

3

N

4

层。因为Si

3

N

4

的顶部也会形成一层薄的氧化层,所以首先要去除该氧化层。湿法刻蚀,首先利用HF去除氧化层,再利用热H

3

PO

4

与Si

3

N

4

反应去除晶圆上的Si

3

N

4

。图2.13是去除Si

3

N

4

后的剖面图。

图2.13去除Si

3

N

4

后的剖面图

LOCOS隔离技术存在两个严重问题:一个问题是场区氧化层横向形成鸟嘴(

bird’s beak

),形成LOCOS场氧的过程中需要消耗掉大约44%的硅,氧原子既进行纵向扩散越过已生长的氧化物与正下方的硅反应生产成氧化物,氧原子也进行横向扩散与Si

3

N

4

掩膜下硅反应生产成氧化物。LOCOS场氧的中部是凸起的然后向两边横向延伸凹入Si

3

N

4

掩膜下的有源区,并且凹入Si

3

N

4

掩膜下的氧化物会逐渐变薄形成鸟嘴的形状,所以横向延伸凹入有源区的现象被称为鸟嘴效应(bird’s beak)。鸟嘴效应与LOCOS场氧的厚度和前置氧化层的厚度成正比关系,通常鸟嘴效应凹进有源区的长度度大于等于前置氧化层的厚度,并且LOCOS场氧的厚度或者前置氧化层的厚度越厚,鸟嘴效应就越显著。对于先进的LOCOS工艺隔离技术,前置氧化层的厚度大约300Å,鸟嘴大概会横向向有源区凹进0.3u,鸟嘴效应减小了器件的有效宽度,从而减小了器件的电流。形成鸟嘴的同时,场区离子注入的杂质也会扩散到有源区边缘的里面,如果器件很窄,场区的杂质可能扩散到器件的沟道下方,它会提高器件的阈值电压,从而减小器件的电流,这一效应被称为窄沟道效应。改善鸟嘴效应的方法有两种,一种是减小前置氧化层的厚度,但是减小前置氧化层的厚度会造成衬底位错形成缺陷,因为很薄的前置氧化层的厚度不足以抵消Si

3

N

4

膜对衬底的应力,另一种是降低LOCOS场氧的厚度,但是降低LOCOS场氧的厚度会影响LOCOS对器件的隔离效果,也会造成寄生的场效应晶体管NMOS导通漏电。所以要对鸟嘴效应、前置氧化层的厚度和LOCOS场氧的厚度进行折中考虑。LOCOS隔离技术的另外一个问题是白带效应,也称Kooi Si

3

N

4

效应,LOCOS是在高温的湿氧的环境下反应生长的,而Si

3

N

4

也会在高温的湿氧的环境下生成NH

3

,NH

3

会扩散到Si/SiO

2

界面,并在Si/SiO

2

界面与Si反应形成Si

3

N

4

,这些Si

3

N

4

在有源区的边缘形成一条白带,这些Si

3

N

4

会影响后续生长的栅氧化层的质量并导致栅氧的击穿电压下降。为了消除Kooi Si

3

N

4

效应,目前最常用的方法是在生长栅氧化层之前,生长一层牺牲层氧化物SAC Oxide(Sacrificial Pre-Gate Oxide),通过SAC Oxide消耗掉Si

3

N

4

,然后再利用湿法刻蚀去掉SAC Oxide,这样可以有效的减小Kooi Si

3

N

4

效应。如图2.14是 LOCOS隔离技术的白带效应。

形成NH

3

的化学反应式 Si

3

N

4

+ H

2

O = SiO

2

+ NH

3

-------------- (1)

形成Si

3

N

4

的化学反应式 Si

+ NH

3

= Si

3

N

4

+ H

2

--------------- (2)

图2.14 LOCOS隔离技术的鸟嘴效应和白带效应

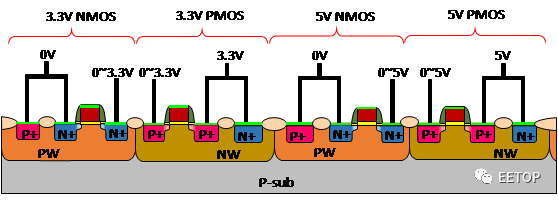

在LOCOS隔离技术的CMOS工艺集成电路中,MOSFET的源和漏扩散区的掺杂类型与衬底的掺杂类型是不同的,源漏与衬底实际上相当于PN结二极管,例如NMOS的源漏是把重掺杂的N型扩散区放在PW里,源漏与衬底形成N型二极管,PMOS的源漏是把重掺杂的P型扩散区放在NW里,源漏与衬底形成P型二极管,PMOS的衬底NW和NMOS的衬底PW形成二极管,PMOS的衬底NW和P-sub也会形成二极管。无论器件工作在开启还是关闭状态,MOS管的源漏与衬底的PN结都是零偏或者反偏的,所以它们的漏电流几乎为零,MOS管是被这种自身的PN结相互隔离的。如图2.15所示是0.35u 3.3V/5V工艺制程技术的器件偏置电压,MOS管的源漏与衬底之间,NW与PW之间形成的PN结都是零偏或者反偏的,它们可以达到相互隔离的效果。因为在CMOS集成电路中PMOS是紧邻NMOS,而NMOS的衬底PW对于NW又可以起到隔离的作用,它相当于BJT工艺中的PW隔离,PW可以隔离不同电压的NW的同时,也隔离了不同电压的PMOS。所以CMOS相当于节省了PW保护环的尺寸,但也不完全是,因为它还要考虑NMOS的漏端N型扩散区与PMOS的NW之间的耗尽区接触穿通问题,类似BJT工艺中的PW隔离的耗尽区隔离问题。如图2.16是3.3VNMOS漏端接3V电压与接3.3V电压的NW之间耗尽区相互靠近。接3V电压的NMOS漏端N型扩散区与接0V电压的PW形成耗尽区,接3.3V电压的NW与接0V电压的PW形成耗尽区,当它们之间的耗尽区相互靠近,它们之间的势垒高度开始减小,电子就更容易越过这个势垒形成漏电流,那么相邻的NMOS漏端N型扩散区与NW之间就会形成漏电流,所以需要考虑NMOS漏端N型扩散区与NW的穿通问题。类似的情况还有PMOS漏端P型扩散区与PW的穿通问题。

图2.15 0.35u 3.3V/5V工艺技术的器件偏置电压

图2.16 3.3V NMOS漏端N+扩散区与NW之间耗尽区相互靠近

利用LOCOS 隔离技术制造的CMOS集成电路工艺也存在寄生场效应晶体管的问题。当金属引线从NMOS的漏端N型扩散区与PMOS的NW之间的PW上方跨过时,将会形成寄生的场效应晶体管NMOS,NMOS漏端N型扩散区如同寄生的NMOS的源端,NW如同寄生的NMOS的漏端,金属互连线是寄生的NMOS的栅极。如图2.17是NMOS漏端N型扩散区与NW之间形成寄生的场效应晶体管。在寄生场效应晶体管NMOS中,LOCOS和ILD的厚度相当于栅氧化层,因为LOCOS和ILD的厚度都比较厚,寄生场效应晶体管NMOS的阈值电压大概在12V左右,对于低压CMOS工艺制程技术的集成电路,它的工作电压小于等于5V,LOCOS隔离工艺技术已经可以有效的解决低压CMOS工艺制程技术寄生的场效应晶体管的导通形成漏电的问题。但是对于高压HV-CMOS和BCD工艺制程技术,它们的工作电压高达40V,它们依然会导致寄生的场效应晶体管开启。

图2.17 NMOS漏端N型扩散区与NW之间形成寄生的场效应晶体管NMOS

为了解决高压HV-CMOS和BCD集成电路寄生场效应晶体管的问题,在生长场氧之后,要增加一道场区离子注入工艺流程,目的是提高寄生场效应晶体管的阈值电压,这样可以有效地改善因为寄生场效应晶体管的导通而形成漏端的问题。

场区离子注入工艺流程如图2.18~图2.22。

1.

涂光刻胶。图2.18是光刻胶的剖面图。

图2.18光刻胶的剖面图

2.

场区离子注入光刻处理。通过光刻技术(曝光、显影、坚膜等工序)将场区离子注入的掩膜板上的图形转移到光刻胶上,定义出场区离子注入区域,非场区离子注入上保留光刻胶。场区离子注入的掩膜板和PW掩膜板是相同的。图2.19 是场区离子注入光刻的剖面图。

图2.19 场区离子注入光刻的剖面图

3.

场区离子注入。场区离子注入的目的是提高寄生场效应晶体管NMOS的阈值电压。因为这道工序要求离子穿透很厚的LOCOS场氧化层,把离子注入LOCOS与Si的界面,所以选择比较轻的硼离子作为离子注入的掺杂源,并且离子注入的能量很高,另外高能量的硼离子会直接穿透没有场氧化层的区域进入衬底Psub,所以场区离子注入不会影响正常的NMOS的电特性。这道场区离子注入不能在淀积LOCOS场氧之前,因为生长场氧时会消耗44%的硅,在高温的环境下硼离子会严重扩散,所以在淀积LOCOS场氧之前进行场区离子注入会严重影响这道场区离子注入的效果,那么调节阈值电压的效果就不明显,因此这道工艺必须在生长场氧化层之后。图2.20是场区硼离子注入的剖面图。

图2.20 场区硼离子注入的剖面图

4.

去除光刻胶。利用干法刻蚀和湿法刻蚀去除光刻胶,干法刻蚀利用O

2

燃烧分解大部分光刻胶,然后湿法刻蚀利用H

2

SO

4

&H

2

O

2

与光刻胶反应去掉残留的光刻胶。图2.21是去除光刻胶后的剖面图。

图2.21去除光刻胶的剖面图

2.1.3STI

(浅沟槽)隔离技术

20世纪80年代末期,研究人员发现LOCOS隔离技术还是不能满足高密度的集成电路的要求,因为最先进的LOCOS隔离技术的最小隔离距离大概是0.6u,LOCOS场氧的鸟嘴向每个方向的横向凹进的宽度是0.3u,所以LOCOS最小的器件与器件的距离是1.2u,它严重影响集成电路的集成度。为了解决LOCOS隔离技术的鸟嘴效应和白带效应,研究人员在LOCOS的基础上开发出STI隔离技术方案,但是STI隔离技术的工艺集成面临许多问题,例如早期在没有CMP(Chemical Mechanical Polishing)全局平坦化技术的时候,需要光刻和刻蚀去除多余的氧化物,并且产品良率非常低,早期的STI隔离技术并不适合用于实际集成电路生产。1983年,IBM发明了CMP技术,CMP技术的出现为STI隔离技术的实用化开辟了道路,1994年,CMP技术被应用于STI隔离技术的实际生产中。STI隔离技术与LOCOS隔离技术非常类似,只不过STI是采用凹进去的沟槽结构,它场区的氧化物不是通过热氧化生长的,而是采用HDP CVD(High Density Plasma CVD)的方式淀积的SiO

2

,所以STI隔离技术可以解决鸟嘴效应和白带效应。由于STI隔离技术的器件密度非常高,STI隔离技术被广泛应用于工艺特征尺寸小于0.3u的集成电路。

STI隔离技术首先是利用各向异性的干法刻蚀技术在隔离区域刻蚀出深度大概2500Å~3500Å的浅沟槽,然后利用HDP CVD淀积SiO

2

,再通过CMP平台化技术对STI进行平台化,去除多余的氧化层,Si

3

N

4

是CMP抛光的终点。最后去除Si

3

N

4

和前置氧化层。

为了更好的理解STI隔离技术,先简单介绍一下STI的工艺制程技术的工艺流程,它主要包括以下步骤:

第一步生长前置氧化层,缓解后续步骤形成Si

3

N

4

层对衬底的应力;

第二步生长Si

3

N

4

,它是STI CMP的停止层,也是场区离子注入的阻挡层;

第三步AA区域光刻处理和刻蚀;

第四步场区侧壁氧化修复刻蚀损伤;

第六步利用HDP CVD淀积场区SiO

2

,形成场区氧化物隔离器件;

第七步利用CMP去除多余的氧化物,进行STI氧化物平整化;

第八步利用湿法刻蚀去除Si

3

N

4

。

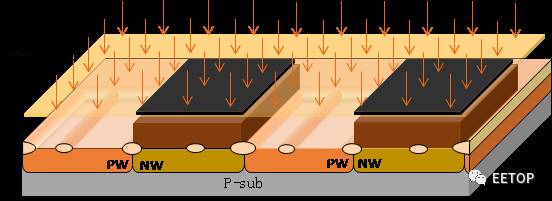

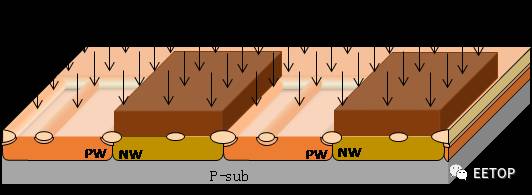

STI工艺流程如图2.22~图2.40。

1.

选取P-type的裸片作为衬底。图2.22 P型衬底剖面图.

图2.22 P型衬底剖面图

2.

淀积前置氧化层。利用APCVD在高温H

2

O或O

2

的环境中形成一层SiO

2

薄层,厚度约150Å~250Å。淀积前置氧化层的目的是缓冲Si

3

N

4

层对衬底的应力,因为衬底硅的晶格常数与Si

3

N

4

的晶格常数不同,直接生长Si

3

N

4

会在衬底中形成应力,如果应力超过衬底硅的屈服强度就会在衬底硅中产生位错。较厚的氧化层可以有效的减小Si

3

N

4

层对衬底的应力。图2.23是前置氧化层的剖面图。

图2.23 前置氧化层的剖面图

3.

淀积Si

3

N

4

层。利用LPCVD淀积一层厚度约1500 Å~1700 Å的Si

3

N

4

层,它是场区离子注入的阻挡层和STI CMP的停止层。图2.24是Si

3

N

4

层的剖面图。

图2.24 Si

3

N

4

的剖面图

4.

淀积SiON层。利用LPCVD淀积一层厚度约200 Å的SiON层,作为光刻的防反射层。图是2.25 是SiON层的剖面图。

图2.25 SiON的剖面图

5.

涂光刻胶。图2.26是涂光刻胶的剖面图。

图2.26 光刻胶的剖面图

6.

AA光刻处理。通过光刻技术(曝光、显影、坚膜等工序)将AA掩膜板上的图形转移到光刻胶上,定义出AA区域,AA区域上保留光刻胶。图2.27 是AA光刻的剖面图。

图2.27 AA光刻的剖面图

7.

AA干法刻蚀。基于氟的反应离子刻蚀(RIE)形成STI沟槽,沟槽的深度大概2500Å~3500Å,沟槽侧壁的角度在75~80度之间。图2.28是AA刻蚀的剖面图。

图2.28 AA刻蚀的剖面图

8.

去除光刻胶。利用干法刻蚀和湿法刻蚀去除光刻胶,干法刻蚀利用O

2

燃烧分解大部分光刻胶,然后湿法刻蚀利用H

2

SO

4

&H

2

O

2

与光刻胶反应去掉残留的光刻胶。图2.29是去除光刻胶后的剖面图。

图2.29去除光刻胶的剖面图

9.

STI侧壁的热氧化,形成SiO

2

。利用APCVD热氧化生长一层很薄的厚度大概250Å~350Å的SiO

2

,修复STI侧壁的刻蚀损伤,使沟槽底部和顶部的拐角圆一些,防止STI的拐角太尖,形成漏电,同时可以防止后续场区离子注入的光刻胶污染硅衬底。二氧化硅薄膜可以作为后续 HDP CVD工序的缓冲,因为HDP CVD工艺是淀积的同时也进行溅射刻蚀,该层二氧化硅薄膜可以保护衬底硅。图2.30是热氧化后的剖面图。

图2.30 热氧化后的剖面图

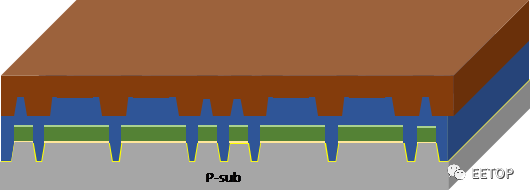

11.

淀积STI场区氧化层。利用HDP CVD淀积一层很厚的的SiO

2

层,厚度约4500 Å~5000 Å。因为HDP CVD是用高密度的离子电浆轰击,它可以防止CVD填充时洞口过早封闭,产生空洞现象,HDP CVD的台阶覆盖率非常好,它可以有效的填充STI的空隙。图2.31是淀积SiO

2

的剖面图。

图2.31淀积SiO

2

的剖面图

12.

涂光刻胶。图2.32是涂光刻胶的剖面图。

图2.32 涂光刻胶的剖面图

13.

AR(Active Area Reverse)光刻处理。利用AA层反版再进行尺寸缩小逻辑运算,得到AR光罩。通过光刻技术(曝光、显影、坚膜等工序)将AR掩膜板上的图形转移到光刻胶上,定义出AR区域,非AR区域上保留光刻胶。AR的目的是通过干法刻蚀去除大块AA区域上的大块SiO

2

,那么整个芯片上只留下小块的SiO

2

,这样有助于后续STI CMP工艺完全去除表面凹凸不平的SiO

2

,得到更平整均匀的表面,同时也可以防止大块AA上的SiO

2

在STI CMP工艺时因为应力过大而损伤AA。图3.33是AR光刻的剖面图。

图2.33 AR光刻的剖面图

14.

AR干法刻蚀。利用干法蚀刻去除大块AA 区域上的的SiO

2

,刻蚀最终停在Si3N4上。图2.34是AA反向刻蚀的剖面图。

图2.34 AR刻蚀的剖面图

15. 去除光刻胶。利用干法刻蚀和湿法刻蚀去除光刻胶,干法刻蚀利用O2燃烧分解大部分光刻胶,然后湿法刻蚀利用H2SO4&H2O2与光刻胶反应去掉残留的光刻胶。图2.35是去除光刻胶后的剖面图。

图2.35去除光刻胶的剖面图

16.