信号完整性,Signal integrity(

简称SI

)

到底是什么,在解决什么问题?

若干年来,硬件攻城狮们

一直为了这个名词在上下求索

一千个人眼里有一千个哈姆雷特

不同时代的攻城狮眼里也有不同的SI问题

— 15年前 —

【

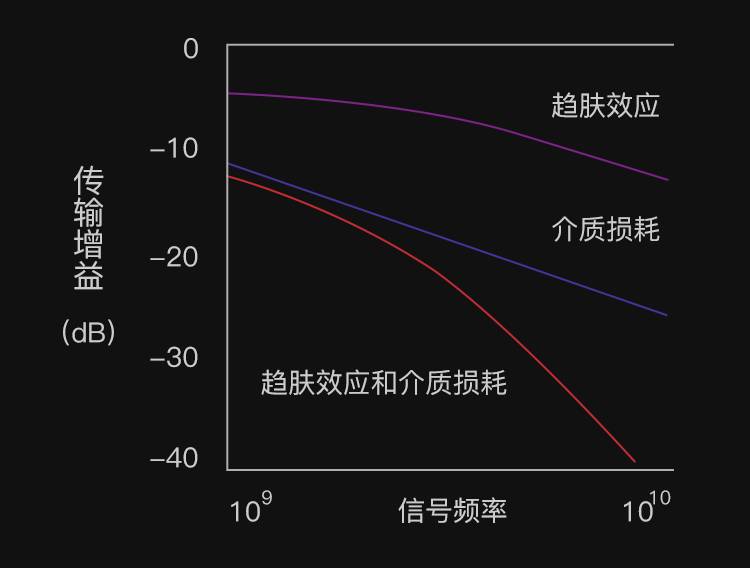

趋肤效应和介质损耗

】

15年前,SI攻城狮们刚开始面对Gbps的信号时,探讨的SI问题是趋肤效应和介质损耗,如同天文学家预言未来有一天会发生彗星撞地球一样,惧怕灾难的降临。

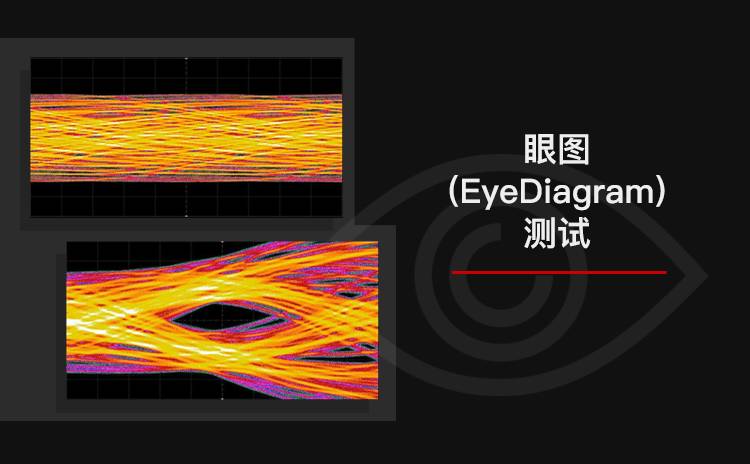

后来引入了

眼图(EyeDiagram)测试和抖动(Jitter)及BER测试,

从统计学角度很好地刻画了SI工程师们最终如何表征信号传输的质量问题,成功越过了险滩。

— 如今 —

信号速率跃迁至几十Gbps

攻城狮们又该何去何从

今天信号速率已经跃迁到几十Gbps,而且采用更宽的链路和复杂的调制方式,遇到的挑战和问题更加层出不穷,新标准新名词目不暇接,攻城狮们是否已经崩溃了?

加上现实成本的考虑

这一切还必须要在传统的FR4板材上实现

这个时候是不是觉得好无助?

然而你不是一个人在战斗!

测量

「英雄」

集结出击

为您搭建从SI设计仿真到测试的全面解决方案

传统产品设计

VS

高速电路设计

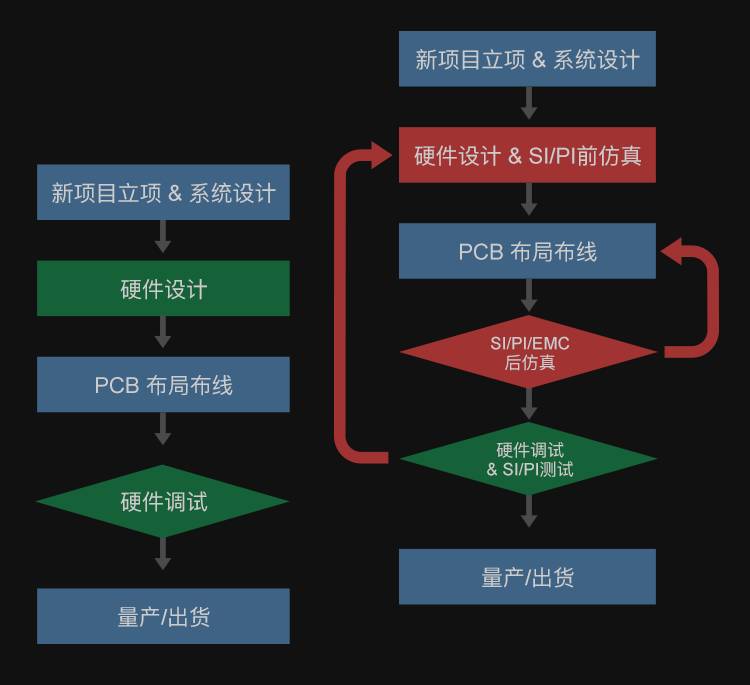

传统电路设计一般是项目立项之后开始硬件电路设计,根据主要元器件设计规范和工程师的经验设计进行PCB设计,制板完成之后调试并确定功能是否满足设计要求。如果发现问题再修改硬件和PCB设计,会浪费很多时间和物料成本。

对于高速电路,不能再按照传统的流程进行设计,高速电路设计在传统设计的基础上增加了前仿真和后仿真以及信号完整性/电源完整性(SI/PI)测试环节。在这一流程中,通过前仿真可以验证电路设计是否正确,并根据实际的设计需求制定相应的设计规范,并输出给PCB设计工程师进行设计。然后通过后仿真进一步验证设计是否符合要求。最后,再通过SI/PI测试以确保产品设计无误才量产发货。通过这样的流程,就能够把一些潜在的问题在研发过程中解决好,大大缩短研发的费用和周期。

下图所示为两种研发流程图,左图为传统产品设计流程,右图为高速电路设计流程:

Keysight作为业界最全面和最专业的测试测量解决方案供应商,可以为SI的设计仿真到测试提供最全面的咨询和服务。

本期内容将着重介绍ADS软件在SI仿真方面的解决方案。后续三期SI内容将分别介绍系统传输链路测试,高速信号的发送端测试以及接收端测试。

点击下方链接,下载本期内容 ——《

ADS软件在SI设计和仿真解决方案

》