最近看到行业群里面经常有人问CPU怎么验证,还有问SOC验证在做什么,今天和大家简要介绍下IP,FPGA,SOC和CPU验证。一般一个芯片的团队组成由以下几个部门组成,Architecture部门,IP designer部门,IP DV部门,Analog 部门,SOC integrator部门,SOC DV部门,DFT部门,PD部门,Firmware部门。比较大点的公司还有CPU部门,CPU DV部门。如果把Firmware部门负责的FPGA验证算在内,验证(DV)在一个芯片设计公司里面占据很大一部分。

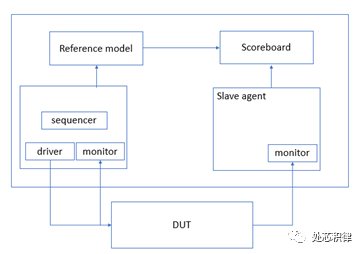

首先介绍IP验证。IP是英文IntellectualProperty的缩写。芯片行业将芯片设计工程师开发出的功能模块作为一种知识产权。我们可以理解IP为实现某些功能的模块,比如AXI,AHB,USB,PCIE,DDR等。IP验证工程师主要保证这些功能模块正常工作。IP验证工程师采用的验证方法主要有UVM验证,Formal验证,当然也可能用到C。一个典型的验证模型一般如下图所示

IP验证又可以分为算法类验证和协议类验证,采用的验证方法大同小异。目前来讲还是以覆盖率(coverage)收敛为导向。IP验证工程师主要做得事情有:

a. 读spec,列测试计划(testplan);

b. 设计验证环境架构,搭建验证环境;

c. 根据测试计划,设计测试用例;

d. 收集code coverage 和function coverage;

e. 测试IP性能。

以上五点是IP验证工程师的主要工作内容,有些公司也会让IP验证工程师参与功耗的测试,FPGA验证,以及SOC验证中。

FPGA验证是指将设计综合成bitfile 烧录到FPGA平台进行测试的过程。FPGA验证的工作主要是Firmware部门主导完成。在成熟的流程里面FPGA验证甚至都可以不用,理论上FPGA能验到的问题通过IP DV都能验到。FPGA的缺点是debug起来非常麻烦,但是由于FPGA跑起来非常快,FPGA相较于IPDV 更侧重于高频次的压力测试,即对某一场景或者很多种场景重复很多次的测试。

很多公司希望能够获得FPGA的仿真速度又可以直观的拉波形进行debug。已有的解决方法有研发硬件加速器,以Cadence的Palladium和Synopsis 的ZEBU为代表。还有通过云计算加速仿真速度,目前国内有创业公司在做这方面研究。此外国外有公司将FPGA和动态仿真进行结合,如Smart DV SimXL。相关知识如果有想了解可以在网上搜索,这里不展开讨论。

图片来源Smart DV

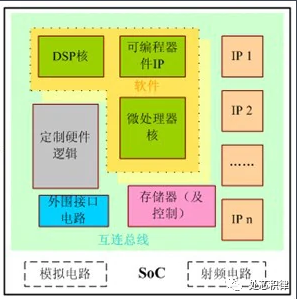

SOC验证主要做什么呢?SOC是System On Chip的缩写,SOC验证工程师验证对象为整个芯片的设计,是保证整颗芯片功能正常运行的重要工作岗位。SOC的验证更侧重于系统级连线,电源管理,多个模块(核)协同工作以及系统级的性能测试等。有时候SOC DV也会配合Firmware部门做一些软件的debug。

SOC验证的手段主要是通过编写C/asm软件代码来完成一系列测试用例,然后通过调用工具链将C/asm代码编译成二进制的文件放在RAM/flash里面,通过CPU读取RAM/flash里面的资料执行相关指令去驱动对外设内存等控制。整个的过程就在模拟一个芯片的实际运行。其工作包括以下内容

a. 罗列测试计划;

b. Bootrom的测试;

c. 各个IP在SOC上集成的测试;

d. 总线互连的测试;

e. 各种时钟和复位测试(时钟开关/调频,软硬件复位等);

f. 电源管理测试;

g. 性能测试;

h. 功耗测试(如PTPX);

i. 电源连接性相关测试(UPF/CPF测试);

j. 网表功能测试(Postsim);

k. 覆盖率的收集;

SOC验证除了用C去完成,有些也会用到UVM和Formal。当芯片超过2000万门时可能还会让SOC验证工程师跑emulation,就是上面提到的采用ZEBU或者Palladium验证整颗芯片的功能和性能。

CPU验证对大部分人比较陌生,主要是因为自己开发CPU的公司比较少。目前RISCV发展迅速,很多公司将自己集成在SOC的功能用拓展指令去控制,因此会对CPU进行改动,未来对CPU验证需求可能会变多。CPU验证的方法学和IP验证稍有不一样,其主要验证手段有通过软件自测,用随机指令产生器(ISG)结合指令仿真器(ISS)进行验证和用Formal进行验证。

软件自测是通过程序自己运行然后与正确的结果进行比对进行检测,比如运行一个乘法运算时,程序将CPU的计算的结果与预存的结果进行比对。

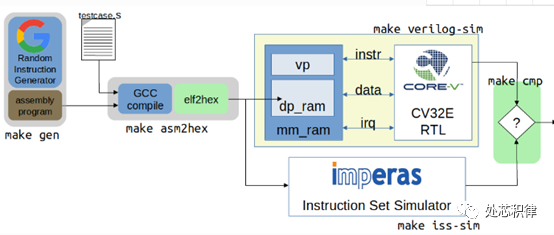

运用ISG和ISS的测试是通过ISG产生随机指令,然后将随机的指令程序给CPU执行,同时将该份程序给ISS执行,最后通过CPU执行产生的跟踪文件(trace log )和ISS执行的跟踪文件比对判断CPU执行的指令是否正常。其验证框架一般如下

目前ISG用的比较经典的是google的ISG,也有公司用UVM自己实现ISG。如果要自己拓展RISCV的指令集,ISS和ISG都需要自己去开发。

EETOP创芯大讲堂金牌芯片课程推荐

双11 75折优惠已开启