文章链接:https://www.nature.com/articles/s41586-024-07786-2

我很喜欢这篇文章!牛的~

摘要

由具有高载流子迁移率的原子级薄材料组成的二维 (2D) 结构已被研究作为未来晶体管的候选结构。然而,由于缺乏合适的高质量电介质,尽管 2D 场效应晶体管 (FET) 具有优异的物理和电学性能,但仍无法发挥其全部理论潜力和优势。这里我们展示了原子级薄单晶 Al2O3 (c-Al2O3) 作为 2D FET 中高质量顶栅电介质的制造。通过使用插层氧化技术,在室温下在单晶 Al 表面形成了一层稳定的、化学计量的、原子级薄的 c-Al2O3层,厚度为 1.25 nm。由于良好的晶体结构和明确定义的界面,c-Al2O3的栅极漏电流、界面态密度和介电强度符合国际器件与系统路线图的要求。通过由源极、漏极、介电材料和栅极组成的一步式转移过程,我们实现了顶栅 MoS2 FET,其特点是陡峭的亚阈值摆幅为 61 mV dec −1,高的开/关电流比为 108,磁滞非常小为 10 mV。该技术和材料展示了生产高质量单晶氧化物的可能性,这种单晶氧化物适用于集成到完全可扩展的先进 2D FET 中,包括负电容晶体管和自旋晶体管。

研究背景和主要内容

随着硅 (Si) 场效应晶体管 (FET) 接近尺寸的基本极限,需要新一代半导体通道来减少短沟道效应。二维 (2D) 材料如二硫化钼 (MoS2 ),其厚度为原子级且具有高载流子迁移率,因此在未来的晶体管中具有巨大的潜力 。尽管2D材料具有比 Si 更好的物理和电学性能,但是还没有合适的高质量电介质材料。因此,基于 2D 材料的 FET 器件无法发挥理论上预测的全部潜力 。在Si

技术中工作良好的非晶态氧化物电介质,例如 SiO2、Al2O3和HfO2,由于长程有序的破坏而无法与2D材料提供均匀且明确的界面。由于二维材料具有非晶态特性及界面不清晰,电荷散射和陷阱难以消除,导致(1)栅极漏电流较大(J > 1.5 × 10−2 A cm−2),(2)界面态密度较大(Dit >1010 cm−2eV−1)和(3)介电强度较低(Ebd < 10 MVcm−1 ) ,无法满足国际器件和系统路线图(IRDS)所规定的要求。此外,由于二维材料具有惰性的无悬挂键表面,在不损坏相邻层的情况下沉积原子级薄的氧化物仍然具有挑战性。

与非晶态氧化物相比,六方氮化硼 (hBN) 、氟化钙 (CaF2 ) (参考文献 11 ) 和钙钛矿氧化锶钛 (SrTiO3 ) (参考文献 13 ) 等晶体电介质材料具有原子级平整表面,可以很好地结合,从而形成更光滑的电介质/2D材料界面。理论上,这些材料可以克服界面质量和缺陷带的问题。然而,晶体电介质也有一些缺点。例如,由于相对较窄的带隙和低介电常数,具有超薄物理厚度的hBN表现出极高的漏电流 ( J >103 Acm−2 ) (参考文献 15)。CaF2和SrTiO3的使用仅限于背栅 FET,尽管大规模集成电路需要顶栅 2D FET。 Bi2SeO5所提供的独特优势本质上与其半导体对应物相关,这意味着当与其他 2D 材料配对时,它可能无法提供相同的优势。其他晶体电介质,如云母,难以精确控制通过剥离或化学生长方法产生的绝缘体的面积和厚度。此外,要从包含晶体电介质的器件中获得1010 cm

-2 eV -1的界面态密度是一项挑战。此外,高质量晶体电介质的晶圆级合成相当具有挑战性。由于目前还没有明确的策略来将电介质缩小到商用 FET所要求的原子级厚度,因此可能有必要为 2D 器件找到完全不同的方法。

原子级薄的金属氧化物最近引起了人们的关注,因为它们具有在块体氧化物中很少发现的独特电子、光学和磁性能。通过简单的氧化,可以在2D器件的金属表面形成稳定的、化学计量的、原子级薄的氧化层。到目前为止,已经提出了由过渡金属如HfO2、TiO2、Fe2O3和Ni2O3;后过渡金属如Al2O3;以及稀土金属,包括Gd2O3 制成的氧化物。这些原子级薄的金属氧化物具有足够的介电性能和原子级平整的表面,使其适用于静电调制2D材料的通道以克服目前的限制。

本研究在 2D MoS2 FET 上获得了单晶 Al2O3 (c-Al2O3) 作为高质量电介质层。通过结合外延剥离和插入氧化,制备了厚度为 1.25 nm 的原子级薄 c-Al2O3,其厚度比先进 Si 晶体管中使用的传统氧化物更薄。由于良好的晶体结构和明确定义的界面,原子级薄 c-Al2O3 的栅极漏电流 ( J < 1 × 10−6 A cm−2 )、界面态密度 ( D it = 8.4 × 109 cm−2 eV−1 )和介电强度 (

E bd = 17.4 MVcm−1 )可以满足低功耗器件的IRDS要求。通过使用范德华 (vdW) 转移方法,整个 FET 堆栈(包括源极、漏极、电介质和栅极)可以一步转移到 MoS2沟道,从而产生具有出色接触和电介质界面的 2D FET。顶栅 MoS2 FET 显示出 61 mV dec−1的陡峭亚阈值摆幅 (SS) 、108的超高开/关电流比和 10 mV 的小回滞。通过制造一批 100 个器件,证明了出色的工艺可重复性和均匀性。

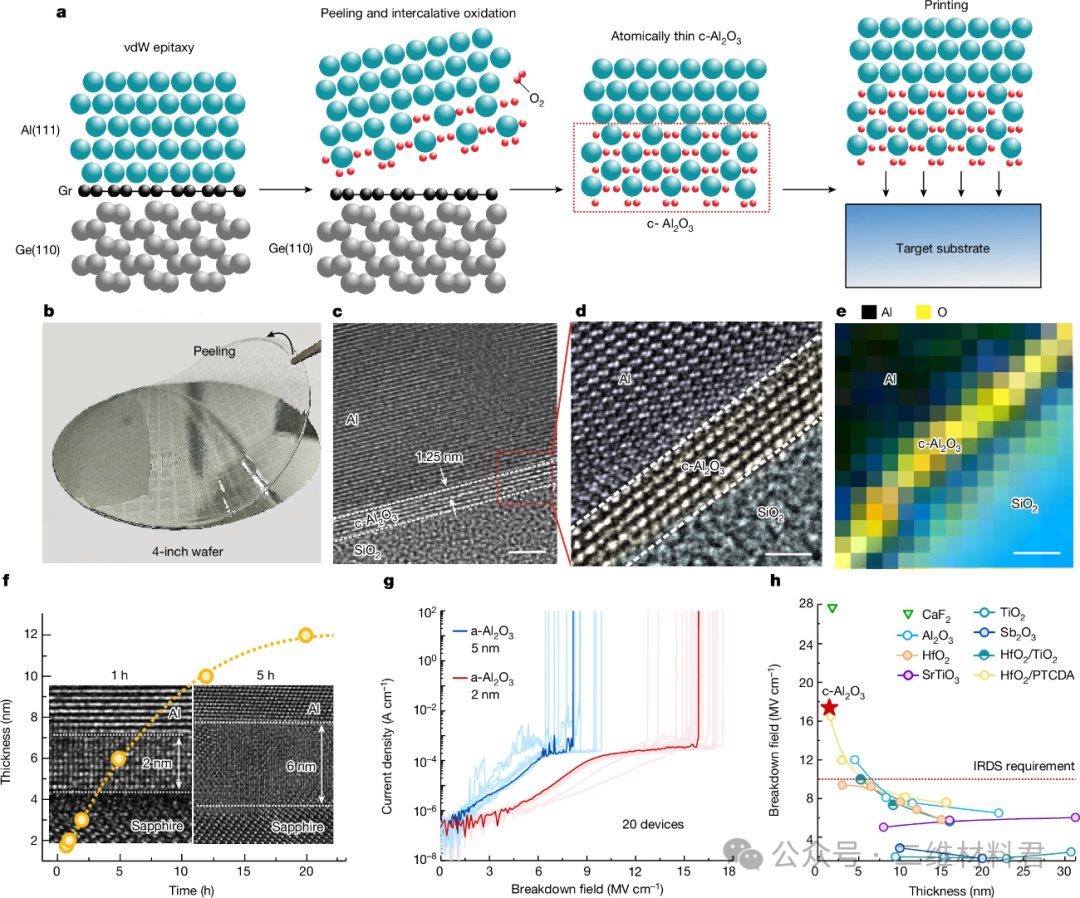

图1a显示了一种可扩展的方法,无需复杂的化学反应或精密的设备即可合成高质量的原子级薄 c-Al2O3层。以石墨烯 (Gr)/锗 (Ge) 晶片为模板,采用范德华外延方法通过电子束蒸发生产晶片级单晶 Al。考虑到Ge在 Si 上的外延, Gr/Ge 基板的直径可以制造到 12 英寸,因此工业规模生产单晶 Al 成为现实。扩展数据图1显示了横截面高分辨率透射电子显微镜 (HR-TEM) 图像和 X 射线衍射结果,以确认在单晶 Gr/Ge(110) 上的单晶 Al(111) 的晶片级范德华外延。我们证明,利用弱的范德华力,可以将具有原子级平整表面的图案化金属从石墨烯上剥离。在这种情况下,Al 可以很容易地从石墨烯上剥离,然后在 0.2 ppm 氧气环境中在室温下轻度氧化。由于原子级平整的单晶 Al 表面和缺氧环境(0.2 ppm O2),可以实现化学吸附氧原子的均匀覆盖和有限的氧渗透。因此,当一个氧原子化学吸附在一个 Al 原子上时,会形成去极化的 c-Al2O3 层,这已经得到理论和实验的证实。在短短几秒钟内,通过逐层机制形成了厚度为几纳米的超薄 c-Al2O3层。扩展数据图2中呈现的横截面 HR-TEM 图像显示了 c-Al2O3 (0001) 和 Al (111)之间的外延关系。最后,将原子级薄的 c-Al2O3转移到目标基板(例如 SiO2、MoS2或 Au)上以制造器件。制造细节在方法和扩展数据图3中呈现。为防止 Al 在 H2O 中氧化,整个过程均无水。此外,得益于无水转移过程,石墨烯表面不受损坏,从而允许重复使用 Gr/Ge 晶片(扩展数据图4)。

图 1:c-Al 2 O 3的制造和表征。a

、通过外延剥离和单晶 Al 膜插入氧化制备原子级厚度的 c-Al2O3。b 、从 4 英寸 Gr/Ge 晶圆剥离 Al/c-Al2O3的光学图像。c 、目标 SiO2基底上 Al/c-Al2O3的横截面 HR-TEM 图像。d 、c中红色框的放大原子分辨率图像。e 、Al/c-Al2O3 /SiO2的 EEL 映射。f 、缺氧环境(0.2 ppm O 2 )中的曝光时间与 c-Al2O3厚度的关系。插图分别为经 1 小时氧化和 5 小时氧化后获得的厚度为 2 nm 和 6 nm 的 c-Al2O3的横截面 HR-TEM 图像。g 、c-Al2O3和 a-Al2O3的击穿场。h 、不同电介质的击穿场与薄膜厚度的比较。比例尺,2 nm(c);1 nm(d、e)。

图1b显示剥离的 Al/c-Al2O3具有接近 100% 的产率,这通过使用聚乙烯醇将 4 英寸图案化 Al 膜从 Gr/Ge 基底上剥离来证明;补充视频 1展示了整个剥离过程。剥离的 c-Al23膜被转移到 SiO2基底上,横截面 HR-TEM 图像如图1c所示。Al表面的c-Al

2O3层厚度约为 1.25 nm。图1c中红色框的放大原子分辨率图像如图1d所示,揭示了 Al/c-Al2O3/SiO2的夹层结构。电子能量损失谱 (EEL) 映射显示了元素分布(图1e),Al 和 O 的分布与夹层结构一致。

此外,可以通过将vdW外延Al层暴露于缺氧环境中不同时间来控制c-Al2O3的厚度。如图1f所示,随着氧化时间从1小时增加到12小时,氧化速率从2nm h -1降低到0.8nm h -1。这是因为氧化过程首先受界面反应控制,然后受氧扩散控制。图1f(插图)显示了厚度为2nm(氧化1小时)和6nm(氧化5小时)的c-Al 2 O 3的横截面HR-TEM图像,更多的HR-TEM图像显示在扩展数据图5中。结果证实,通过控制氧化时间可以制备不同厚度的c-Al2O3层。此外,补充图1和补充表1显示了4 英寸 c-Al2O3 /Al 晶片的厚度映射,表明变异系数非常均匀,为 ±6%。

图1g显示了击穿场 ( E bd ) 与电流密度趋势的比较。c-Al2O3在远高于 IRDS 要求的 10 MV cm −1的工作场中保持完全绝缘。从 20 个具有 c-Al2O3绝缘体的金属-绝缘体-金属 (MIM) 器件确定的平均E bd为 16 MV cm −1

,最大值为 17.4 MV cm −1。相比之下,通过在周围环境中剥离 Al 膜制造的厚度为 5 nm 的非晶态Al2O3 (a-Al2O3 ) 层表现出较小的平均E bd ,约为8 MV cm −1 ,与之前的研究相似。E bd的增强可能来自能隙增量或晶体绝缘体中的缺陷密度降低。图1h比较了不同金属氧化物的E bd与薄膜厚度的关系,详细信息见补充表2。由于晶体结构和大带隙(8.8 eV),c-Al2O3中的缺陷辅助隧穿受到抑制。因此,与非晶态氧化物(TiO2 、Al2O3和 HfO2)以及单晶氧化物(CaF2、 SrTiO3 和 Sb2O3 )相比,原子级薄的 c-Al2O3 表现出最高的 E bd (17.4 MV cm −1) 之一。值得注意的是,c-Al2O3的Ebd超过了低功率器件的IRDS要求(E bd > 10 MV cm −1 )。

栅极漏电流(

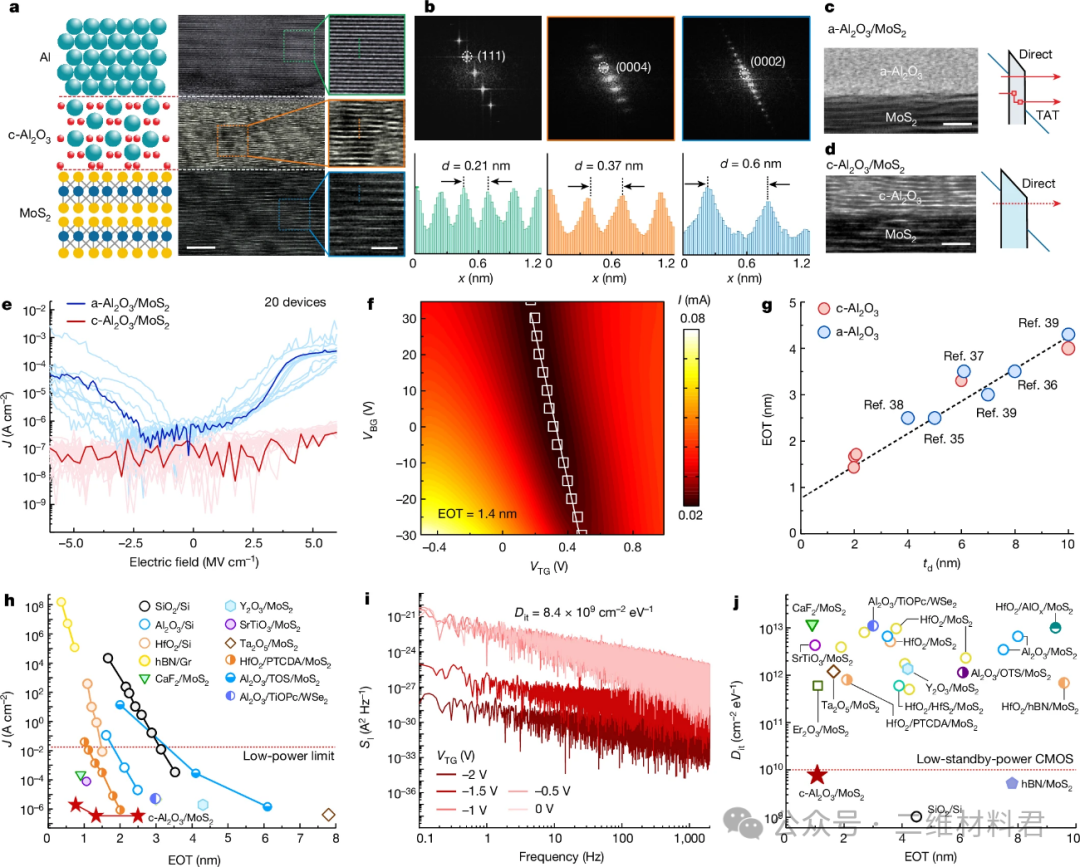

J)和界面态密度(D it)是低功耗器件的重要特性,J和D it应分别小于1.5×10−2 A cm−2和1010 cm−2 eV−1,以满足低功耗器件的IRDS要求。然而,对于2D器件来说,满足这些严格的要求具有挑战性,因为非晶氧化物不能提供明确定义的界面 ,而晶体电介质材料容易与2D通道形成突变界面,但其中一些,例如Sb2O3 ,SrTiO3 ,h-BN,具有相对较小的带隙。可以使用单晶 c-Al2O3解决这些问题,因为与其他高κ氧化物相比,它具有 8.8 eV 的足够带隙。为了确定 Al/c-Al2O3栅极特性,将该结构转移到多层 MoS2上以形成 Al/c-Al2O3 /MoS2异质结构(图2a )。异质结构的横截面 HR-TEM 图像显示从上到下分别由单晶 Al、c-Al2O3和 MoS2层组成的堆栈。在 c-Al2O3和 MoS2之间观察到原子级清晰的界面。图2a (右)中虚线绿色、橙色和蓝色框的放大图像分别表示单晶 Al、c-Al2O3和MoS2。图2b显示了图2a

中绿色、橙色和蓝色虚线框的选定区域电子衍射图案,证实了每个堆叠区域的结晶性。图2a中沿绿色、橙色和蓝色虚线的线轮廓(图2b ,底部)显示了原子间距离的周期性变化。Al、c-Al 2 O 3和 MoS 2的距离分别为0.21nm、0.37nm和0.6nm。

图 2:Al/c-Al2O3栅极的特性。a 、Al/c-Al2O3/MoS2异质结构的示意图(左)、横截面 HR-TEM(中)和放大的原子分辨率(右)图像。b 、从a中虚线绿色、橙色和蓝色框获得的选定区域电子衍射图案(顶部)。沿a中虚线绿色、橙色和蓝色线的线强度分布(底部)。c、 a-Al2O3 /MoS2的 HR-TEM 图像(左)和重要的隧穿贡献(右)。d 、 c-Al2O3 /MoS2的 HR-TEM 图像(左)和重要的隧穿贡献(右)。e 、具有 c-Al2O3和 a-Al2O3的 2D FET 的实验栅极漏电流。f 、电流和栅极电压之间的关系。VTG,顶栅电压;VBG,背栅电压。g、EOT 与介电厚度的关系。h 、在标准工作栅极电压 1 V 下测量的实验栅极漏电流与 EOT 的比较。i 、噪声功率谱与频率的关系。j 、 Si 器件与不同 2D 技术测得的D it

值比较。比例尺,5 nm(a,底行,中间);2 nm(a,底行,右);2 nm(c,d)。TAT,陷阱辅助隧穿。

通过相同的积分方法将两种不同类型的 Al2O3电介质材料(非晶态和晶体态)转移到 MoS2沟道上。图2c(左)显示了a-Al2O3 /MoS2的 HR-TEM 图像,图2d (左)显示了c-Al2O3/MoS2的HR-TEM 图像。图2c (右)显示了a-Al2O3 /MoS2结的重要隧穿贡献,图2d (右)显示了c-Al2O3 /MoS 2结的重要隧穿贡献。除了通过 a-Al2O3的直接隧穿外,在含有大量缺陷的绝缘体中观察到的陷阱辅助隧穿也起着重要作用。相反,这些隧穿电流受到抑制,因为 c-Al2O3具有更宽的带隙和更小的缺陷密度。图2e给出了c-Al2O3 /MoS2和 a-Al2O3 /MoS2的实验J

值,c-Al2O3 /MoS2显示的J值比 a-Al2O3 /MoS2大约低两个数量级。

制作了以 SiO2 /Si 为全局背栅、以 Al/c-Al2O3为顶栅堆叠的双栅器件,以准确测量等效氧化物厚度 (EOT)。如扩展数据图6所示,通过实验提取顶栅电容 ( C TG )。使用方程式 EOT = 3.45/ CTG (参考文献 32 )计算出 EOT 为 1.4 nm (图2f )。此外,制作了六个具有不同 EOT 的器件,如扩展数据图6所示。图2g比较了不同电介质厚度 ( t d )下的 EOT 值。补充图2显示了介电常数与t d的比较。正如预期的那样,对于 a-Al2O3和 c-Al2O3,EOT 都随 t d 线性增加,这与方程EOT = 3.9 td/ εd一致,其中εd是Al2O3的介电常数。 具体而言,与迄今为止报道的其他基于 Al2O3的 2D 器件相比, c- Al2O

3显示出最小的 EOT ,并且还展示了缩小 2D FET 的潜力。

图 2h 给出了具有不同 EOT 的其他典型非晶氧化物电介质、 c-Al 2 O 3电介质和晶体电介质的J值。除 hBN 外,具有明确界面的晶体电介质材料具有比传统非晶氧化物更小的J。由于带隙小、介电常数低,2D hBN 表现出极高的J值。c - Al2O3 / MoS2器件显示的J值为 10 −6 A cm−2 ,比 IRDS的低功耗要求 (10 −2 A cm −2 )低四个数量级。此外,即使温度升高到约 403 K(补充图 4),J 值(EOT = 0.77 nm;补充图 3)仍然保持稳定,这表明在c-Al2O3中几乎看不到非晶态介电材料中的陷阱辅助隧穿现象。将 c-Al2O3/MoS2与成熟的 Si-CMOS 技术进行比较,可以发现J比 Al2O3 /Si(参考文献 20 )低五个数量级,这表明 c-Al2O3/MoS2 FET具有巨大的缩小潜力。

界面态密度 ( D it )由 1/ f噪声法确定,如图2i所示。由于 c-Al2O3和 MoS2之间界面明确,因此D it降低至 8.4 × 109 cm−2 eV −1,与电容电压法测得的值相似(补充图5 )。计算细节在方法中描述。图2j显示了D it值与文献中值的比较,详细信息显示在补充表3中。大部分剥离 MoS2沟道的D it值都很高,范围从 5 × 10 11 cm −2 eV −1到 10 13 cm −2 eV −1 ,适用于传统非晶氧化物电介质和晶体电介质。在我们的案例中,c-Al2O3/MoS2实现了 8.4 × 10 9 cm −2 eV −1的Dit ,它满足低待机功耗CMOS的IRDS 要求,并且与 Si/SiO2 ( D it ~ 10 9 cm −2 eV −1)相当。

为了研究基于 c-Al2O3的 2D FET 的电子特性,采用 vdW 转移法制作了具有 2nm c-Al2O3的自对准 MoS2 FET。自对准 MoS2 FET 的制作过程如图3a和补充图6所示。图3b显示了自对准 MoS2 FET 阵列的扫描电子显微镜 (SEM) 图像。Al 栅极的宽度和长度分别为 100μm 和 250nm。图3c显示了 Au 和 Al 栅极之间的小气隙,这确保了顶栅极和源极或漏极之间的完全绝缘以及成功的自对准过程。沟道长度为 300nm(L