现场可编程门阵列(FPGA)可以实现任意数字逻辑,从微处理器到视频生成器或加密矿机,一应俱全。FPGA由许多逻辑模块组成,每个逻辑模块通常由触发器和逻辑功能以及连接逻辑模块的路由网络组成。FPGA的特殊之处在于它是可编程的硬件:您可以重新定义每个逻辑块及其之间的连接,用来构建复杂的数字电路,而无需物理上连接各个门和触发器,也不必花费设计专用集成电路的费用。

内部裸片显微照片

内部裸片显微照片

FPGA是由Ross Freeman发明的,他在1984年共同创立了Xilinx,并推出了第一款FPGA--XC2064。这种FPGA比现代FPGA简单得多,它只包含64个逻辑块,而现代FPGA中的逻辑块有几千个或数百万个,但它导致了目前价值数十亿美元的FPGA产业。由于其重要性,XC2064被列入芯片名人堂。在这篇博文中,我们对Xilinx的XC2064进行了逆向工程,解释了它的内部电路(上图)以及 "比特流 "是如何对它进行编程的。

Xilinx XC2064是第一款FPGA芯片

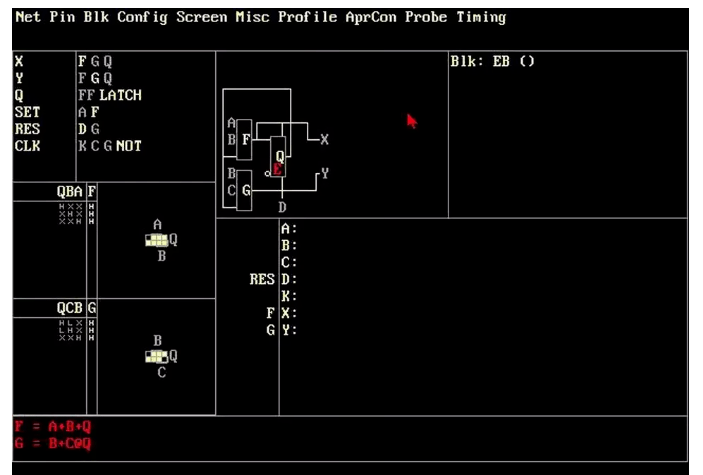

如今,FPGA是采用Verilog或VHDL之类的硬件描述语言编程的,但是当时Xilinx提供了他们自己的开发软件XACT,运行再MS-DOS操作系统之下,价格高达12,000美元。XACT自然无法与现在的FPGA开发工具相比,XACT通过用户定义了每个逻辑块的功能(如下面的屏截图所示)以及逻辑块之间的连接,对连接进行布线连接,并生成可加载到FPGA中的比特流文件。

XACT的屏幕截图。两个查找表F和G在屏幕底部实现逻辑运算,上面部分显示该逻辑的卡诺图

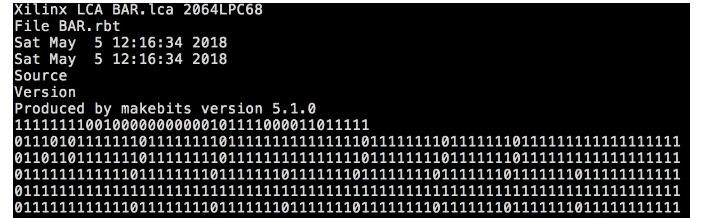

通过位流(具有专有格式的位序列)配置FPGA。如果您查看XC2064的比特流(如下所示),那是令人费解的混合模式,这些模式不规则地重复,并散布在比特流中。XACT中的功能定义与位流中的数据之间没有明确的联系。但是,研究FPGA的物理电路可以揭示比特流数据的结构,并且可以理解。

通过位流(具有专有格式的位序列)配置FPGA。如果您查看XC2064的比特流(如下所示),那是令人费解的混合模式,这些模式不规则地重复,并散布在比特流中。XACT中的函数定义与位流中的数据之间没有明确的联系。但是,研究FPGA的物理电路可以揭示比特流数据的结构,并且可以理解。

下图来自原始FPGA专利,显示了 FPGA 的基本结构。

在此简化的FPGA 中,有9个逻辑块(蓝色)和12个I/O引脚。

互连网络将组件连接在一起。

通过设置互连上的开关(对角线),逻辑块相互连接并连接到I/O引脚。

每个逻辑元素都可以使用所需的逻辑功能进行编程。

其结果是一个高度可编程的芯片,可以实现任何适合可用的电路。

虽然上图显示了九个可配置逻辑块(CLB),但XC2064有64个CLB。

下图显示了每个CLB的结构。

每个CLB有四个输入(A、B、C、D)和两个输出(X 和 Y)。

两者之间是组合逻辑,可以使用任何所需的逻辑功能进行编程。

CLB还包含一个触发器,允许FPGA实现计数器、移位寄存器、状态机和其他有状态电路。

梯形是多路复用器,可以编程通过其任何输入。

多路复用器允许为特定任务配置CLB,为触发器控件和输出选择所需的信号。

您可能想知道组合逻辑如何实现任意逻辑功能。它会采用与门、或门、异或门等逻辑吗?不,它使用一种称为查找表(LUT)的巧妙技巧,实际上它包含的是逻辑功能的真值表。例如,三个变量的功能由其真值表中的8行定义。LUT由8位内存以及多路复用电路组成,以选择正确的值。通过将值存储在这8位内存中,可以实现任何 3 输入逻辑功能。

FPGA的第二个关键部分是互连,可以对其进行编程以不同方式连接CLB。

互连相当复杂,但是粗略的描述是每个CLB之间有几个水平和垂直线段。

CLB互连点允许在水平线和垂直线之间建立连接,从而可以创建任意路径。

更复杂的连接通过“交换矩阵”(switchmatrices)完成。

每个开关矩阵都有8个引脚,可以(几乎)任意方式将它们连接在一起。

下图显示了XC2064的互连结构,提供了到逻辑块(青色)和I/O引脚(黄色)的连接。

该图显示了路由功能的特写。

绿色框是8针开关矩阵,而小方块是可编程的互连点。

每个CLB都有从AA到HH的字母名称。互连可以将例如块DC的输出连接到块DE的输入,如下所示。红线表示路由路径,红色小方块表示已激活的路由点。离开模块DC后,信号由第一个路由点定向到8针开关(绿色),该信号将其引导到另外两个路由点和另一个8针开关。(未显示未使用的垂直和水平路径。)请注意,布线相当复杂;即使是这条短路径,也使用了四个路由点和两个开关。

下面的屏幕截图显示了XACT程序中的路由外观。黄线指示逻辑块之间的路由。随着信号的加入,挑战在于如何有效地路由而不使路径发生冲突。XACT软件包执行自动路由,但也可以手动编辑路由。

XACT程序的屏幕截图。此MS-DOS程序通过键盘和鼠标进行控制

本文的其余部分讨论了XC2064的内部电路,从裸片照片中的反向工程。

下图显示了XC2064芯片的布局。FPGA的主要部分是8×8的网格。每个图块包含一个逻辑块和相邻的路由电路。尽管图片显示将逻辑块(CLB)显示为与围绕它们的路由不同的实体,但这并不是FPGA的实现方式。取而代之的是,每个逻辑块和相邻路由都实现为单个实体,即图块。(具体来说,图块包括每个CLB上方和左侧的路由。)

I/O模块围绕集成电路的边缘提供与外界的通信。它们连接到小的绿色方形焊盘,该焊盘连接到芯片的外部引脚。裸片被缓冲区(绿色)划分:两个垂直和两个水平。这些缓冲器可放大在电路中传播很长距离的信号,从而减少延迟。垂直移位寄存器(粉红色)和水平列选择电路(蓝色)用于将比特流加载到芯片中,如下所述。

下图显示了XC2064中单个Tile的布局;如上图所示,该芯片包含64个这样的Tile挤在一起。每个Tile约有40%的面积被保存配置位的内存单元(绿色)所占据。顶部三分之一处通过两个交换矩阵和许多单独的路由交换处理互连路由,下面是逻辑块。逻辑块的关键部分是输入的多路复用器、触发器和查找表(LUT)。每个块通过垂直和水平布线连接到相邻的块,以实现互连,电源和接地。配置数据位被水平地馈送到存储单元,而垂直信号选择要加载的存储单元的特定列。

FPGA由CMOS逻辑实现,该逻辑由NMOS和PMOS晶体管构建。

晶体管在FPGA中具有两个主要作用。

首先,可以将它们组合以形成逻辑门。

其次,晶体管被用作信号通过的开关,例如以控制路由。

在此作用下,该晶体管称为传输晶体管。

下面的裸片照片特写显示了在显微镜下晶体管的外观。多晶硅栅极是两个掺杂硅区域之间的蛇形线。