苹果在iPhone 上使用“"fan-out"扇出式封装芯片,其主要优点是能够带来更紧凑的主板及天线设计,从而不进可以为电池预留出了更大的空间,而且也能够让机身变得更加的纤薄。

扇出WLP是一种晶圆级加工的嵌入式封装,也是I/O数较多、集成灵活性好的主要先进封装之一。

而且,它可以不用基板在一个封装中实现垂直和水平方向的多芯片集成。所以,目前扇出WLP技术正朝着诸如多芯片、薄型封装和3D

SiP这些下一代封装方向发展。扇出WLP不仅用于电子封装,而且用于传感器、功率IC和LED封装。本文报导下一代扇出WLP先进封装解决方案的进展情况。

像移动电话一类的电子装置已从单一的通讯工具转化为综合多种特性的集成系统,成为有多种用途的精巧工具。随着这一趋势的发展,用于便携式电子设备的半导体封装器件正遇到前所未有的挑战。不断增长的互连间距的失配、加入具有不同功能的各种芯片、以及在同样的占用面积下减少封装尺寸以便增加电池大小延长使用时间等均已为创新嵌入封装技术打开了窗口。

为了满足上述挑战,开发了扇出WLP技术,它提供了另外的空间用于给硅面积顶部上的较高I/O芯片布线,这在常规的WLP或WLB中是不可能的。

WLP的应用正在扩展到新的领域,并基于I/O数目与器件进行细分。无源、分立、RF和存储器等器件的基础正在扩展到逻辑IC和MEMS。WLP在过去10年已臻成熟,大量资料提供了多种晶圆直径上的大批量应用,并扩展到各式各样的终端市场产品。随着基础设施和批量应用的到位,降低成本就是主要的关注领域了。

扇出WLP结构最著名的例子之一是由英飞凌公司(Infineon Technologies

AG)开发的eWLB技术。该技术采用前后道制造技术结合并行加工晶圆上的全部芯片,能大大降低制造成本。其优点是:与常规的引线框架或叠层封装比较,封装面积较小、I/O数量从中等到高、连接密度最大化、以及能获得所需的电学和热性能。它也能为无线市场提供高性能和节能的解决方法。

硅片上制造的集成电路以各种不同的电子封装形式装配,广泛应用在如个人便携式、医疗保健、娱乐、工业、汽车、环保和安保系统等电子产品中。这些电子系统当前和未来在性能、功耗、可靠性及合理成本方面的要求,将通过开发先进/适用的硅加工技术,创新的采用芯片封装系统协同设计、低成本材料、先进的装配和可靠互连技术的封装封装解决方案得到满足。本文讨论了手持应用的封装解决方案,详细讨论了称为扇出WLP的下一代芯片嵌入技术。

扇出WLP技术

扇出WLP技术提出了许多影响因素。这方面的一端是封装成本以及测试成本。除此以外就是其占用面积和高度这样的物理限制。开发阶段要考虑的其他参数有:I/O密度(对具有高引脚数的小芯片是特殊的挑战);需要兼容系统级封装(SiP)方法;与功耗有关的散热问题以及器件的电学性能(包括电寄生参数和工作频率)。

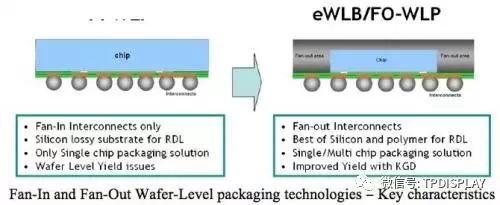

驱动力是某种形式的WLP。不过提出了自己的选择:扇入或扇出。扇入WLP是在晶圆上直接加工的互连系统,与母板技术节距要求兼容。它将常规的前后道制造技术结合起来,并行加工所有芯片。加工中有3个阶段。晶圆厂的另外一些步骤在每一芯片上创建互连系统,占有面积比芯片小。然后在晶圆上应用焊球和实行并行测试。最后,晶圆切割成独立单元,这些单元直接用在母板上,不需要插入件或底部填充。扇出WLP方法不应与凸点倒装芯片器件混淆,后者有较精细的节距和较小的凸点,因此需要底部填充。

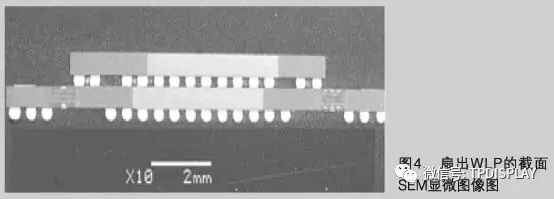

扇出WLP中,芯片被合适的材料围绕,这些材料将封装所占面积扩展到芯片以外。测试合格芯片用晶圆级模塑技术嵌入人造塑料晶圆(重组晶圆)内。然后用前道绝缘和金属化工艺,以晶圆级光刻和制图方法将互连扇出到周围区域。再次在晶圆上应用焊球并进行并行测试。然后把重组晶圆切割为独立单元,包装和发运。用扇入方法时,互连数和它们的节距必须与芯片尺寸适应。相反,扇出WLP支持适应性强的扇出面积,对焊球节距没有什么限制。

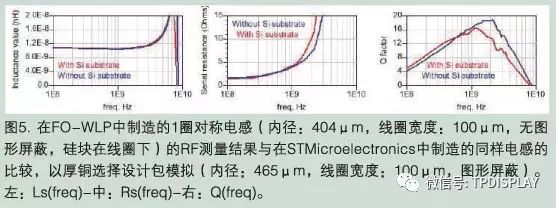

扇出WLP的推动力为:减少厚度、高I/O密度、节距、散热性能、性能参数。扇出WLP的一个关键性能是质量因子。由于在扇出WLP上采用了特殊材料,质量因子比CMOS晶圆好得多。

下一代扇出WLP技术

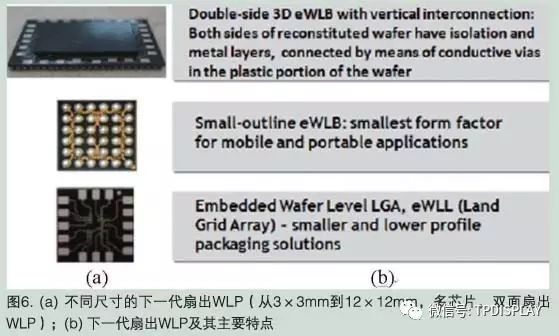

第一代扇出WLP技术设计用于单芯片、单面和1层RDL方面。为了解决市场对于更高性能和设计复杂性不断提高的要求,应开发新的技术和外壳,并在目前的扇出WLP技术中实现,如下所示:

小芯片尺寸扇出WLP:用于移动和手提电子设备

具有垂直互连的2面3D扇出WLP:重组晶圆的二面均有绝缘和金属层,用晶圆塑料部分中的导电通孔连接

嵌入晶圆级LGA,eWLL(平面栅格阵列)- 较小和较薄封装解决方法

小芯片扇出WLP

正进行评估的另一组封装技术是小型扇出和超小型扇出WLP。由于Si技术节点正从40nm向更小尺寸移动,或是有越来越多的功能集成于Si器件中,或是功能不变时Si芯片尺寸本身不断缩小。因此,需要有仅仅比嵌入的Si片尺寸稍大的封装。本文设计了如下二种试验方案:

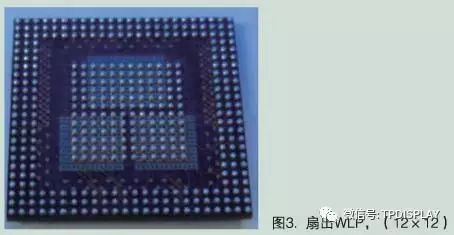

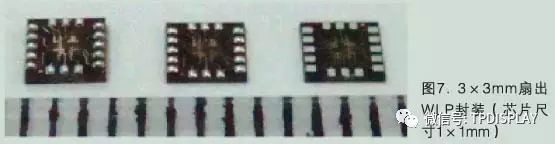

TV1-1×1mm芯片尺寸,3.0×3.0mm扇出WLP

TV2-2×2mm芯片尺寸,2.4×2.4mm扇出WLP

I/O总数是49,36,节距0.4mm,SnAgCu焊球。TV2在Si和封装外形间的间隙只有250μm,如图7、图8所示。

图7和图8显示了某些合格的超小型扇出WLP。正成为晶圆级批量加工技术的扇出WLP能导致这种小尺寸封装的显著成本优势。为了评估封装级可靠性,进行了JEDEC标准测试。小外形扇出WLP已通过JEDEC

MSL1,TC,uHAST,HTS,20X再流和跌落/TCoB测试。

2面3D扇出WLP

通过实现以下各种先进封装,下一代扇出WLP扩大了扇出WLP的应用空间:(a)用2-L

RDL的高密度布线,(b)用薄扇出WLP的超薄封装,(c)混合信号集成及SiP封装采用多芯片扇出WLP,(d)用大和超大扇出WLP的高扇出比嵌入Si封装。在3D封装领域,正开发应用于PoP的超薄扇出WLP。图9显示12×12mm扇出WLP中5芯片SiP的详细情况。PoPb有3个嵌入芯片,PoPt有2个嵌入芯片。PoPb和PoPt二者均是在晶圆级工艺中制造的。顶部和底部封装二者均不需要基板,这使整个PoP非常薄。由于扇出WLP的CTE(热膨胀系数)比基板的小得多,这就导致扇出WLP与下面的PCB之间的CTE失配小得多,预计焊点可靠性会有提高。

对于更薄的薄型封装解决方案,制备了0.5mm高度的双面扇出WLP研究更薄封装板级可靠性。薄扇出WLP的体厚度为250μm。制备了高度不同的二种封装,见图10。

为了评估封装级可靠性,对2面3D扇出WLP测试器件进行JEDEC标准测试。已通过了JEDEC MSL1、TC、uHAST、HTS、20X再流及焊球剪切试验和开路-短路试验。

手提电子产品很容易发生意外跌落,从而引起内部电路板损坏,例如,在焊点金属间化合物(IMC)界面处由于脆性断裂产生的焊点失效,或由于焊接材料中的冲击疲劳引起的焊点失效。若焊点很牢固,失效处能迁移到电路板的铜走线,甚至使树脂开裂。当电子产品跌落到地上时,冲击力和变形会向内部传递到印刷电路板(PCB)、焊点和集成电路(IC)封装。IC封装易发生焊点开裂,这是在冲击过程中PCB弯曲和机械惯性冲击相结合引起的。跌落测试为跌落可靠性设计提供了有用的实验方法。