近来,HTC 以 11 亿美元价码,出售代工部门给 Google 的新闻,让笔者不得不回忆起,1997 年 11 月先跟国家半导体合并、随后出售给 VIA,在高效能 x86 处理器发展史占有一席之地的 Cyrix,与史上第一款 Pentium 兼容处理器6×86「M1」。

距今已 22 载的 1995 年,Windows 95 的问世前所未见地刺激个人计算机的市场需求,以 Intel Pentium 为首的高效能超纯量(Superscalar)x86 处理器,自然而然成为执行微软全新32 位元作业系统的引擎,而 1995 年底上市的 Intel Pentium Pro,和 1996 年拥有和 Windows 95 相同使用者界面的 Windows NT 4.0,更敲开了 x86 处理器涌入工作站与服务器市场的大门。

在当时,「Pentium 跑 95、Pentium Pro 跑 NT」是不可质疑的搭配,而 Pentium Pro 执行16 位元程序码效能不佳的疑虑,更让这约定俗成的潜规则,更加牢不可破。

但过没多久,1996 年个人计算机零售市场却出现了 Intel 以外的另类选择:价格较廉、时脉较低、整数运算更强,但浮点运算更弱、使用起来更烫的 Cyrix 6×86「M1」,它也引爆了短暂的 x86 处理器战国时代。

1995 年到 2000 年这段期间,堪称是处理器与显示芯片市场最热闹的时期,这在论 x86 处理器只想到Intel 和 AMD(可能连 VIA 都快被遗忘了)、显示芯片仅列出nVidia 和 AMD 的今天,实在令人难以想象。

微软视窗作业系统最重大里程碑Windows 95,和最普及办公室生产工具Office 95 的问世,带来了个人计算机发展史上最巨大的升级潮与采购潮,远较过去作业系统更飢渴难耐的系统效能需求,也刺激了对更高速处理器与更快 2D 视窗加速的需要,吸引来自四面八方的众多英雄好汉,瓜分这块肥美的市场。

套句当时PC Magazine「Inside Track 专栏」的评论:市场仍可允许x86 处理器标上不菲的高价,即使是小厂,只要些许市占率,即可掠取丰厚的利润。所以不分新秀老将,像「有晶圆厂才是真男人」的 AMD、「三百壮士」的 Cyrix、IDT 投资的 Centaur、众多台湾企业集资的 Rise、僱用 Linus Torvalds的 Transmeta、AMD K6 起源的 NexGen,甚至在前苏联开发超级计算机背景的 Elbrus 等,无不磨刀霍霍,企图从 Intel 身上割下一块肥肉。

但严格说来,真正勉强交出像样成绩单的,除了今天依旧与 Intel 激烈交火的 AMD,就仅剩 Cyrix 了,其他厂商的表现,实在不用多说。

以旧世代Intel处理器脚位进行升级,提供跨代性能表现的Cyrix

有别于今日Intel、AMD 的处理器脚位,自从K7 时代的 Slot A 开始「你走你的阳关道,我过我的独木桥」,没经历过个人计算机上古时期的读者,可能较难想象,当初众多「Intel 脚位兼容处理器」百家争鸣的盛况,还包含今日少人知悉、在此市场以开发x87 浮点辅助运算器起家的 Weitek 与 Chips and Technologies(后来被 Intel 购并)等。

笔者曾瞻仰其他网站的「达人高见」:使用与 Intel 相同的插槽,是个人计算机发展史上极为罕有的情况。拜托,在做主机板可以做到股王的年代(意思就是主机板的价格和获利都高到令人发指),你家的处理器不能和 Intel 共享脚位,才是让人感到诡异的怪事。

这些厂商的共同点:在比较老旧的 Intel 处理器脚位上,提供接近下一世代产品效能表现的替代品,抢攻旧系统的升级市场。当然,如果效能和价格具竞争优势,也有办法取得Intel 最新的系统总线授权,这些厂商也希望可直接跟 Intel 在相同脚位上硬碰硬,追求更高产品单价与获利,并设法攻入 OEM 大厂的供应链。

Cyrix 就以此块市场起家,例如FasMath 83D87 可装在 387 的脚位,提供比 Intel 80387 浮点辅助运算处理器多出 50% 的效能,而 486SLC/DLC 则是在 386 平台,带来部分Intel 80486 的特色,如第一阶快取存储器等。

而 Windows 95 推出之际,在 486 系统安装Cyrix 5×86(或 AMD 的 Am5x86)的「穷人第五世代计算机」,更是受学生欢迎的低阶 Pentium 替代品,当年光在学生宿舍就不知见证了多少案例。

因延宕而错失「首款非循序指令执行超纯量x86处理器桂冠」的Cyrix 6×86

前面提到,Windows 95 与 Windows NT 4.0 带来的市场动量,引爆了 x86 处理器的效能革命,CISC 指令集的 x86 处理器,也破除了昔日RISC 狂信者那「CISC 无法管线化、无法高时脉、无法超纯量」的多年诅咒,从整数运算效能为起点,开始具备挑战RISC 诸神的实力(但浮点运算受制于堆栈架构的 x87 指令集,难以飞跃性成长,这瓶颈到了 SSE 出现后才慢慢消失)。

如同第五世代战斗机需要的 3S:匿踪(Stealth)、超音速巡航(Super Cruise)、超机动性(Super Maneuverability),所谓80586 时期的第五世代x86 处理器,为了高效能,也同时追求 3 个 S:

•

超纯量(Superscalar)

:一个时脉可同时执行一个以上的指令。

•

超管线(Superpipeline)

:更高的运作时脉与后继的成长空间。

•

延展性(Scalability)

:支援服务器与工作站市场必备的多处理器环境。

Cyrix 首款正面挑战Intel Pentium,甚至在整数运算保有越级挑战Pentium Pro 潜力的 6×86「M1」,拥有前两项特性,并多出减轻暂存器相依伤害的「暂存器重新命名机制(非循序指令执行)」与「预测执行」,而缺乏第 3 个要素。当时市场上唯一三者兼备的 x86 处理器,仅有 1995 年 11 月上市的 Intel 新旗舰Pentium Pro,而上市时间一再延宕至 1996 年初,也让 Cyrix 6×86 痛失了「史上首款非循序指令执行超纯量 x86 处理器」的桂冠。

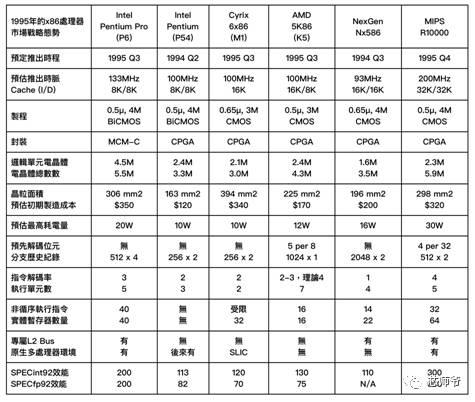

处理器既然是「产品」,产品就必然有「规格」,有规格就自然可以「比一比」,我们就来比较一下,在预定上市的 1995 年,6×86 跟同期的 x86 处理器(顺便拖 MIPS R10000 进来当 RISC 对照组,让各位看一下RISC 全盛期的荣光),规格差在哪里。

这张和后来实际状况有点出入的简略概观比较,其实就已经隐隐约约散发出对 Cyrix 不妙的气息了:制程劣势,这在 1996 年 Intel 开始大量销售0.35 µm(350nm)制程处理器时,就对 Cyrix 更加不利了。

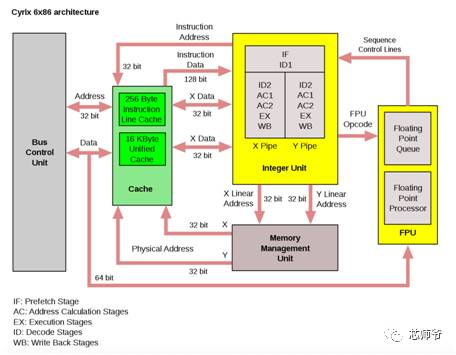

奠定未来数年微架构基础的6×86「M1」

不过「三分靠打拚,七分天注定」的制程劣势,带来更烫的运作温度和更高的制造成本是一回事,延宕已久的 Cyrix 6×86 在微架构设计,相较于对手Intel Pentium,却颇有看头。这里会花点篇幅仔细介绍,因为之后数年 Cyrix 的处理器产品,其管线结构均换汤不换药。

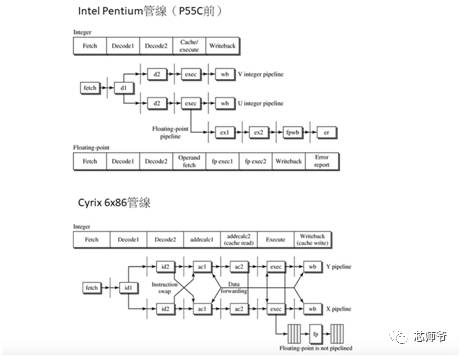

超纯量(Superscalar)部分,提供两条功能相对完整的管线

:Intel Pentium 的 U/V 管线须完美配对指令,如限定两个简单的单时脉周期整数运算指令(有少数例外,在此不论),才能发挥100% 的效率,因为只有U 管线能执行全部指令,V 管线仅能处理较简单者。所以像一个整数和一点浮点、或两个浮点指令配对,在 Pentium 都不被允许同时执行。

但 6×86 即使也有类似限制,如 X/Y 管线仅前者可执行分支指令与浮点运算,但远较 Pentium 弹性,且可在指令译码阶段,交换彼此负责的工作,所以在 Pentium 需要一个一个处理的指令流,在 6×86 就更有机会同时送作堆一起执行。

利于时脉发展空间的深度管线

:七阶的超管线(Superpipeline)分离了「从存储器载入资料」、「进行有效位址计算」与「回存资料到存储器」3 个动作,有效减少了存取快取存储器的延迟,足以媲美同期的 Alpha 21164(七阶)与 MIPS R10000(八阶),也意谓着比较高的时脉延展潜力,虽然受制于外包代工的制程(SGS Thomson与IBM),在与 Intel 竞争的过程中,完全显现不出其价值。

因管线深度加长,势必加强分支预测效率,与减轻预测错误的代价(Misprediction Penalty),这部份 6×86 大致近似Pentium,但增加了存放函数返回位址缓冲区(Return Stack Buffer),而配置指令预先撷取缓冲区,也缩短了发生预测错误时,回复指令管线运行需要的时脉周期数。

暂存器重新更名(Register Renaming)与存储器旁路(Memory Bypassing)

:这些与非循序指令执行相关的功能,堪称M1 微架构的重头戏。

讲的单纯一点,透过配置数量比指令集定义的逻辑暂存器、更多的实体暂存器为缓冲(6×86 用 32 个实体暂存器,「更名」成 8 个 x86 指令集定义的通用暂存器),可减轻因发生不同指令存取相同暂存器,导致「撞衫」但并非真正的资料相依时,指令管线的停滞时间。而发生快取误失(Cache Miss)时,指令管线亦可继续执行后继指令。

如发生「真正的」暂存器资料相依,如第一个指令要从存储器载入至某暂存器,第二个指令再对此暂存器进行加法运算,6×86 可同时执行这两个指令,并将第一个指令在 AC2 阶段的存储器资料,「Bypass」到后面指令的 EX 执行阶段。这情况发生在 Pentium 的话,就只能慢慢等了。

但这 3 种凌驾Pentium 的特色,都被 1995 年底发表、采取解耦式超纯量(Decoupled Superscalr)的 Pentium Pro 统统比下去了,后来P6 微架构降尊纡贵为进入桌机市场的 Pentium II,更是 20 世纪末期Intel 诸多竞争者的恶梦。

况且,除了制程以外,6×86 也不是没有弱点。

指令集兼容性仅有 486 水平

:Cyrix 在被国家半导体购并前,并未获得Intel 技术授权,完全藉由逆向工程独立开发x86 兼容处理器,所以自然而然不是百分百兼容Intel 产品,像 Intel 在 Pentium 新增的指令,如非常知名的 CPUID,在 6×86 就付之阙如(原本1994 年芯片Tape Out 时,Cyrix 宣称会支援,但后来预设关掉)。

Intel 在 Pentium 使用者手册,故意保持空白的「附录H」中,描述的众多新指令与新功能,如用来计算指令周期数的 RDTSC,Cyrix 也以「避免制造法律纷争」为由,统统不碰,若不幸碰到了,就视为非法指令,至于所谓「Undocumented」的非公开指令,更连提都不用提了。无法完全兼容的严重后果,就是软件公司需要特别为 6×86 撰写补丁程序,以确保兼容性。

同场加映 AMD 当时的处境:拚死拚活逆向工程,也要在 K5 挤出附录H 的兼容性,成果在此不论。

这也是 x86 处理器发展史一个潜在地雷,不像其他RISC 家族都有明确的版本演进规范,x86 指令集一直缺乏公定版本,很多厂商自己光明正大搞自己的特殊指令(包括Cyrix,后文会提到),而 Intel 基于「既得利益」,压根不打算做这功德无量的好事。

支援多处理器环境受限

:初代 Pentium 可透过外挂单价28 美元的 82498DX 先进可程序化中断控制器(APIC)实作双处理器环境,而 P54C 时期开始,更直接将其内建于处理器,成为无须外挂系统连结芯片(Glueless)的原生方案,但 6×86 并未整合APIC,而是采用自家SLiC,也只有VIA Apollo 芯片组提供支援。

其实x86 并不是到 Pentium 才有多处理器系统。由 17 位因 iAPX432 计划失败而离职的 Intel 员工所创立,堪称对称式多处理器架构(SMP)技术先驱,后来被 IBM 购并的 Sequent Computer Systems,就曾先后推出一系列采用386 与 486 的多处理器产品线。这些象征「x86 团结就是力量」的产品,全都仰赖特制系统芯片组与特化过的作业系统,才能搞定正确路由(route)系统中断至各处理器的宿疾,且因专属规格所费不赀,P54C 时代的 Pentium 才就此划下句点。

但双 Pentium 处理器环境,因低落的快取存储器与系统总线效能而缺乏竞争力,这缺陷到了 Pentium Pro 才釜底抽薪(这也强化了用 Pentium Pro 跑 Windows NT 的诱因)。即使Cyrix「硬上」,惨况只会跟 Pentium 如出一辙。