随着摩尔定律发展趋缓,先进封装越来越成为延续和拓展摩尔定律的重要手段;同时,在集成电路应用的多元化发展趋势下,满足系统微型化、多功能化的先进封装技术成为产业发展的新的引擎。在人工智能、自动驾驶、

5G

网络、物联网等新兴产业的加持下,三维(

3D

)集成先进封装的需求越来越强烈,技术发展迅猛。

先进封装发展背景

封装技术伴随集成电路发明应运而生,主要功能是完成电源分配、信号分配、散热和保护。伴随着芯片技术的发展,封装技术不断革新。封装互连密度不断提高,封装厚度不断减小,三维封装、系统封装手段不断演进。随着集成电路应用多元化,智能手机、物联网、汽车电子、高性能计算、

5G

、人工智能等新兴领域对先进封装提出更高要求,封装技术发展迅速,创新技术不断出现。

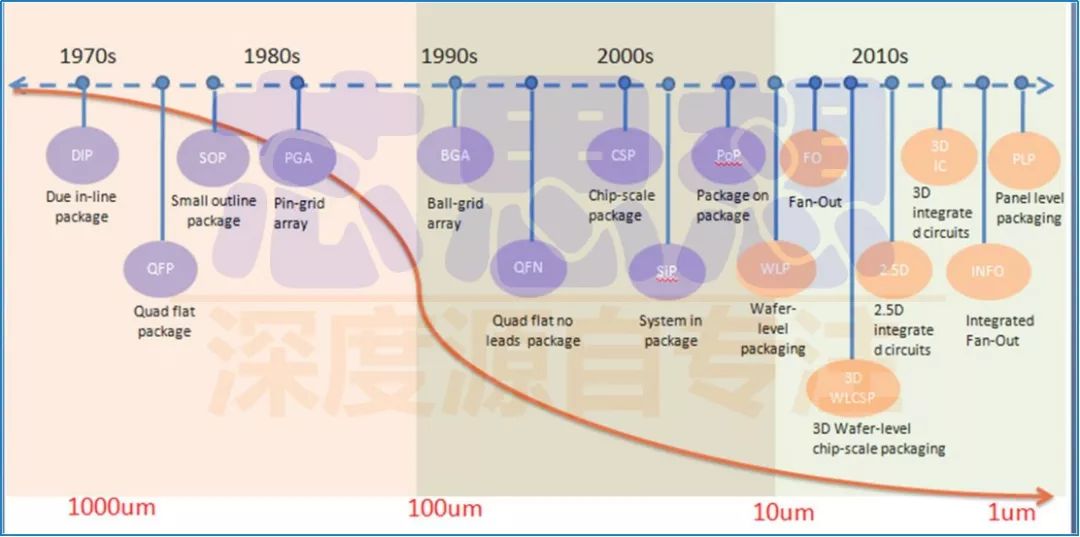

60

年来,由于集成电路技术按照摩尔定律飞速发展,封装技术跟随发展。进入

2010

年后,高性能芯片需要高性能封装技术。中道封装技术崭露头角,例如晶圆级封装(

WLP

,

Wafer Level Package

)、硅通孔技术(

TSV

,

Through Silicon Via

)、

2.5D Interposer

、

3DIC

、

Fan-Out

等技术的产业化,极大地提升了先进封装技术水平。

当前,随着摩尔定律趋缓,封装技术重要性凸显,成为电子产品小型化、多功能化、降低功耗,提高带宽的重要手段。先进封装向着超高密度、三维堆叠、高带宽、系统集成方向发展。

先进封装技术平台与工艺

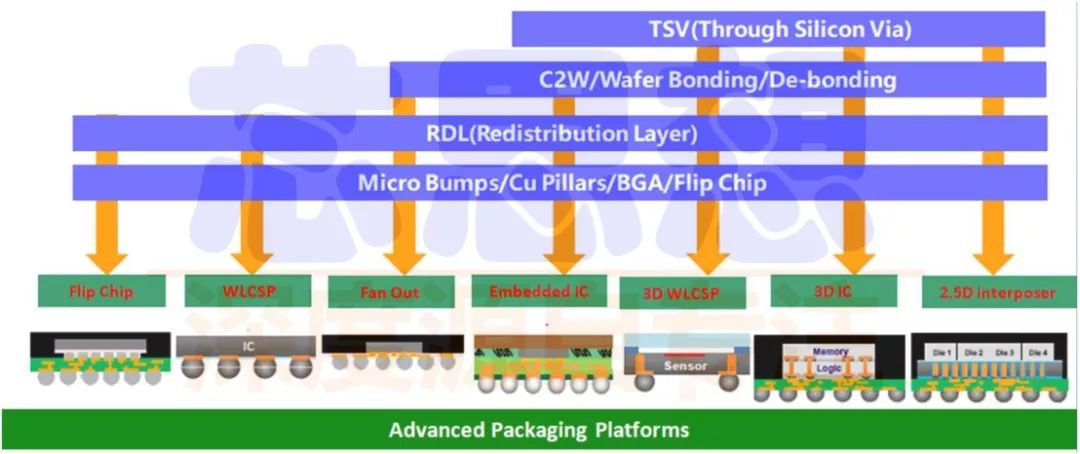

上图(先进封装技术平台与工艺)

展示了当前主流的先进封装技术平台,包括

Flip-Chip

、

WLCSP

、

Fan-Out

、

Embedded IC

、

3D WLCSP

、

3D IC

、

2.5D interposer

等七个重要技术。其中绝大部分和晶圆级封装技术相关。支撑这些平台技术的主要工艺包括微凸点、再布线、植球、

C2W

、

W2W

、拆键合、

TSV

工艺等。先进封装技术本身不断创新发展,以应对更加复杂的三维集成需求。当前,高密度

TSV

技术

/Fan-Out

扇出技术由于其灵活、高密度、适于系统集成,而成为目前先进封装的核心技术。

封装技术的发展得益于互连技术的演进和加工精度的显著提高。目前三种主要用于集成电路(

IC

)芯片封装的互连技术分别为:引线键合技术(

Wire Bond

,

WB

)、倒装芯片技术(

Flip Chip

,

FC

)和硅通孔技术(

Through Silicon Via

,

TSV

)。由于现代微电子晶圆级加工能力的大幅度提升,晶圆级封装的布线能力已达到微米量级。从线宽互连能力上看,过去

50

年,封装技术从

1000µm

提高到

1µm

,甚至亚微米,提高了

1000

倍。微凸点互连节距也从几百微米,发展到当前

3D IC

的

40µm

节距,很快将发展到

5µm

以下节距无凸点互连。

主要封装技术发展

三维封装技术发展

一、

2.5D

封装技术

1

、台积电

CoWoS

为解决有机基板布线密度不足的问题,带有

TSV

垂直互连通孔和高密度金属布线的硅基板应运而生。连接硅晶圆两面并与硅基体和其他通孔绝缘的电互连结构,采用

TSV

集成,可以提高系统集成密度,方便实现系统级的异质集成。

带有

TSV

的硅基无源平台被称作

TSV

转接板(

Interposer

),应用

TSV

转接板的封装结构称为

2.5D Interposer

。在

2.5D Interposer

封装中,若干个芯片并排排列在

Interposer

上,通过

Interposer

上的

TSV

结构、再分布层(

Redistribution Layer

,

RDL

)、微凸点(

Bump

)等,实现芯片与芯片、芯片与封装基板间更高密度的互连。其特征是正面有多层细节距再布线层,细节距微凸点,主流

TSV

深宽比达到

10:1

,厚度约为

100µm

。

台积电

2008

年底成立集成互连与封装技术整合部门,

2009

年开始战略布局三维集成电路(

3D IC

)系统整合平台。

2010

年开始

2.5D Interposer

的研发,

2011

年推出

2.5D Interposer

技术

CoWoS

(

Chip on Wafer on Substrate

)。第一代

CoWoS

采用

65

纳米工艺,线宽可以达到

0.25µm

,实现

4

层布线,为

FPGA

、

GPU

等高性能产品的集成提供解决方案。

第一个采用

CoWoS

封装的产品是

2012

年赛灵思(

Xilinx

)推出“

Virtex-7 2000T FPGA

”的

FPGA