来源:本文由半导体行业观察翻译自semiwiki

,作者Scotten Jones,

谢谢。

多年以来,2D NAND 一直都是半导体工业光刻(lithography)技术的发展推动力,其印刷尺寸是最小的,而且保持逐年下降。随着 2D NAND 的尺寸缩小到了十几纳米节点(16nm、15nm甚至 14nm),每个单元也变得非常小,使得每个单元中仅有少数几个电子,而串扰问题又使得进一步缩小变得非常困难而且不够经济。

随着 2D NAND 的问题越来越多,业界开始着眼于 3D NAND。现在,我们正见证着 3D NAND 的快速增长,3D 位产量正在超过 2D 位产量。在这篇文章中,我们将仔细探究 3D NAND 技术,并会对 3D NAND 和 2D NAND 的成本进行比较。

东芝和三星在 3D NAND 上的早期开拓性工作带来了两大主要的互相竞争的 3D NAND 技术。

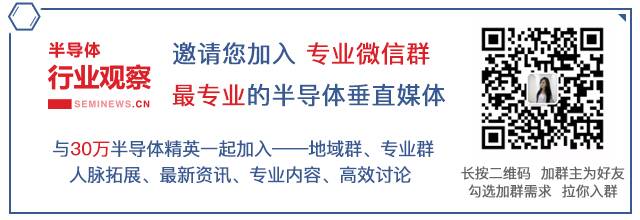

东芝开发了一种叫做 Bit Cost Scalable(BiCS)的工艺。BiCS 工艺采用了一种先栅极方法(gate-first approach),这是通过交替沉积氧化物(SiO)层和多晶硅(pSi)层实现的。然后在这个层堆叠中形成一个通道孔,并填充氧化物-氮化物-氧化物(ONO)和 pSi。然后沉积光刻胶,通过一个连续的蚀刻流程,光刻胶修整并蚀刻出一个阶梯,形成互连。最后再蚀刻出一个槽并填充氧化物。如图 1 所示。

图 1:BiCS 工艺

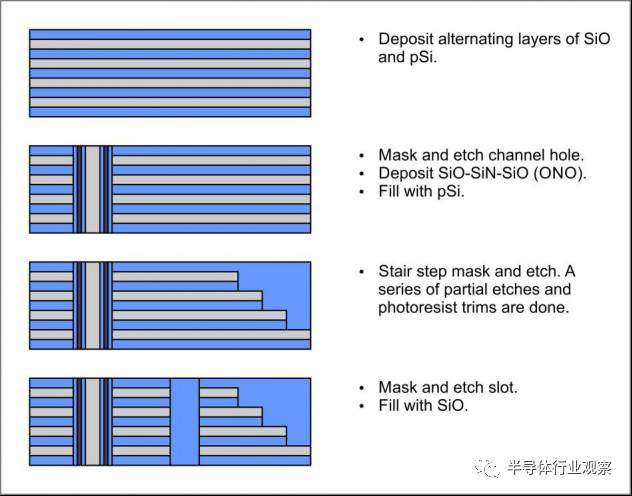

三星则开发了一种 Terabit Cell Array Transistor (TCAT)工艺。TCAT 是一种后栅极方法( gate-last approach),其沉积的是交替的氧化物和氮化物层。然后形成一个穿过这些层的通道并填充 ONO 和 pSi。然后与 BiCS 工艺类似形成阶梯。最后,蚀刻一个穿过这些层的槽并去除其中的氮化物,然后沉积氧化铝(AlO)、氮化钛(TiN)和钨(W)又对其进行回蚀(etch back),最后用坞填充这个槽。如图 2 所示。

图 2: TCAT 工艺

这两种工艺都能得到电荷陷阱存储单元(charge trap memory cell)。

从前面的讨论和图中可以看出,这两种工艺的基本不同在于 BiCS 使用了 pSi 字线的先栅极方法,而 TCAT 则使用 W 字线的后栅极方法。

长时间以来,业内都有传言说东芝做不出有效的 BiCS,而东芝的生产部分基本上就是复制的 TCAT 工艺,尽管东芝还是称之为 BiCS。

英特尔-美光走了一条类似于 BiCS 的路,只不过他们构建的是浮栅极(floating gates)。

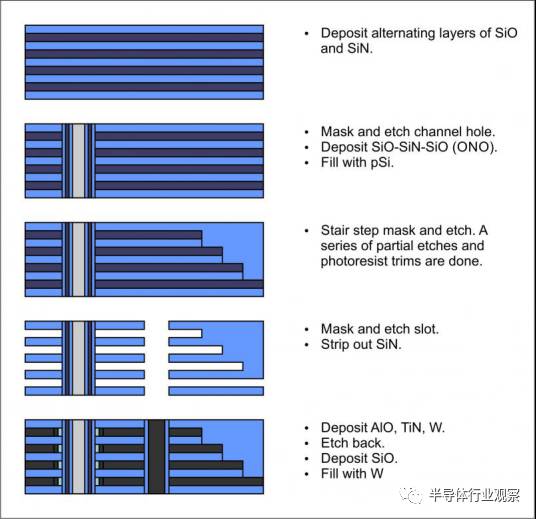

很多人看了下面美光给出的图后都评论说 3D NAND 的资金成本比 2D NAND 高 3 到 5 倍。但这幅图表达的不是这个意思!这幅图想表达的是从 2D NAND 节点转换到 3D NAND 节点的成本是从 2D NAND 节点转换到一个新的 2D NAND 节点的成本的 3 到 5 倍。

图 3:美光 2D NAND 到 3D NAND 的转换成本

2D NAND 是一种光刻主导的工艺,20nm 以下的节点需要多个四重图案步骤。从一个节点移动到下一个节点的推动力主要来自于光刻工具的改进。当升级光刻工具时,通常可以用当前的工具以旧换新获得改进后的工具,从而降低转换成本。

而 3D NAND 则是使用的 3D 存储堆栈技术所需的专门工具来进行沉积和蚀刻。光刻技术不是 3D NAND 发展的推动力,在 3D NAND 工艺流程中最多也只有一个双重图案步骤。但是,其流程中却有多个高纵横比蚀刻步骤,其中每个晶片的蚀刻时间高达 30 至 60 分钟!

为了进一步探索它,我们来研究一下 2D 和 3D NAND 新建晶圆厂的资金需求。我的公司 IC Knowledge LLC 开发了半导体行业中应用最广泛的成本建模工具。我们的战略成本模型(Strategic Cost Model)可以为 2D 和 3D NAND 工艺给出详细的设备配置需求。在比较新建晶圆厂之前,图 4 给出了基于三星工艺的 2D 和 3D NAND 的转换成本。

图 4: 2D NAND 和 3D NAND 的转换成本

从图 4 中我们可以看到,在特定的工艺转换上有类似于图 3 的 3 到 5 倍的转换成本。

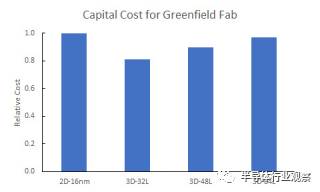

但是,如果我们模拟构建一家新建 2D NAND 晶圆厂的成本与一家新建 3D NAND 晶圆厂的成本,我们则会看到完全不同的景象,3D 的资金成本甚至比 2D 的资金成本还稍微低一点!如图 5 所示。

图5:新建晶圆厂成本

与资金成本类似,我们相信在晶圆成本上也有些模糊不清的地方。图 6 比较了三星的 Line 12 晶圆厂的 2D 16nm 晶圆成本与三星的西安晶圆厂的 3D 64 层晶圆成本。

图 6:升级后设施的 2D NAND 和 3D NAND 晶圆成本对比

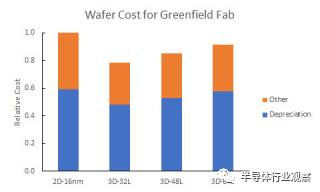

Line 12 在 2003 年上线,经过了多次升级,使得现在设备配置中关键部分的成本已经达到了最低。而西安晶圆厂则在 2014 年上线,所有设备的成本都还在下降过程中。如果我们将新建的 2D 和 3D NAND 晶圆厂的晶圆成本从不同的图片融合到一起,就得到了图 7.

图 7:新建的 2D NAND 和 3D NAND 晶圆厂的晶圆成本

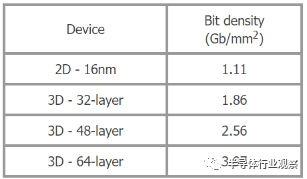

用一个 NAND 的位(bit)总数除以管芯尺寸(die size),我们可以计算出 bits/mm² 指标。在今年的 ISSCC 上,三星在 session 11 发表了论文《A 512Gb 3b/cell 64-Stacked WL 3D V-NAND Flash Memory》。根据这篇论文,我们可以比较从 64 层 3D NAND 到 2D NAND 的各种工艺的位密度。下面的表格给出了三星的值(所有器件都是 3 bits/cell)。

表 1:三星 NAND 的位密度

从表 1 中我们可以看到 3D NAND 的位密度高于 2D NAND,64 层的 3D NAND 更是超过了 16nm 的 2D NAND 的三倍!

目前 3D NAND 的产量还不及 2D NAND,因此每个晶圆上优良位的数量还未达到 3D 位密度优势应有的水平。