本文介绍了复旦大学包文中研究员与绍芯实验室的谭小军和王印合作发表的研究,该研究针对二维半导体材料(特别是过渡金属二硫属化物如MoS2和WSe2)在集成电路技术中的应用进行了探索。研究中提出了一种新型的自对准工艺,用于制造晶圆级自对准MoS2顶栅场效应晶体管(TG-FETs)。这一工艺利用顶栅金属作为硬掩模,通过湿法和干法混合刻蚀技术实现源漏金属的自对准沉积,具有优异的兼容性和大规模集成制造的潜力。优化后的器件展现出显著改进的电学性能和稳定性。此外,还成功制备了反相器、与非门和或非门逻辑门,展示了在先进电子电路中的小型化和应用潜力。

二维半导体材料在推动集成电路技术节点的发展中具有关键作用,得益于其独特性质,包括无悬键特性、超薄厚度以及与硅的优异兼容性。然而,目前的应用主要局限于沟道长度较长和大栅极区域的器件,探索支持缩小2DSM顶栅场效应晶体管尺寸的制造工艺至关重要。

研究团队提出了一种新型自对准工艺,用于制造晶圆级自对准MoS2顶栅场效应晶体管。该工艺利用顶栅金属作为硬掩模,结合湿法和干法选择性刻蚀技术,避免了栅极与源漏之间的重叠或未对准问题。优化后的器件展现出卓越的电学性能,包括高开态电流、高开关比、低滞后窗口和低亚阈值摆幅。成功制备了沟道长度为200 nm的器件,以及反相器和逻辑单元,验证了该工艺的有效性和可行性。

新型自对准工艺具有良好的兼容性和大规模集成制造的潜力。通过优化接触和介电层,所制备的器件实现了高性能和均匀性。此外,该研究还展示了该工艺在推动高性能二维电子器件在小型化和集成应用中的发展的重要性。

该研究的相关文献信息,包括作者、文章标题、期刊、年份和链接等。

为了方便各位同学交流学习,解决讨论问题,我们建立了一些微信群,作为互助交流的平台。

2.告知:姓名-课题组-研究方向,由编辑审核后邀请至对应交流群(生长,物性,器件);

欢迎投稿欢迎课题组投递中文宣传稿,免费宣传成果,发布招聘广告,具体联系人:13162018291(微信同号)

【研究背景】

【研究背景】

二维半导体材料(2DSM),特别是过渡金属二硫属化物(TMDs)如MoS

2

和WSe

2

,在推动集成电路(ICs)迈向下一代技术节点中具有关键作用。这主要得益于其独特的性质,包括无悬键特性、超薄厚度以及与硅的优异兼容性。这些特性有助于有效缓解短沟道效应,使器件在小型化过程中仍能保持较高的迁移率。迄今为止,通过化学气相沉积(CVD)和金属有机化学气相沉积技术,已成功合成了高质量的晶圆级TMD薄膜。TMDs在逻辑电路、模拟电路、传感器、存储器以及异质结单元中的应用已得到验证,展现了其广泛潜力。然而,目前TMDs的应用主要局限于沟道长度约为10 µm或更长以及较大栅极区域的器件。因此,探索支持缩小2DSM顶栅场效应晶体管(TG-FETs)尺寸并确保与大规模集成方法兼容的制造工艺至关重要。

2DSM FETs的集成工艺主要分为两类:栅极优先工艺和栅极后工艺。在栅极优先工艺中,埋栅或全局背栅在其他组件之前制备,而栅极后工艺则是在栅极对准沉积之前先制造源漏和介电层。然而,这两种方法在大规模制造,特别是沟道长度小型化方面均存在局限性。栅极优先工艺需要在栅极和介电层沉积后转移大尺寸MoS

2

,这一额外步骤可能导致裂纹和残留物的形成,从而降低良率。另一方面,栅极后工艺由于MoS

2

无悬键的表面以及沟道与源漏金属之间不可避免的台阶,在建立氧化物种子层和介电层方面面临挑战。随着沟道长度的减小,实现栅极与源漏区域的精确对准变得越来越复杂。栅极与源漏区域的显著重叠或未重叠可能会增加寄生电容或电阻,限制了当前集成工艺支持进一步小型化沟道长度的能力。

从硅产业的兴起到45 nm节点,多晶硅自对准工艺取代了基于铝(Al)的栅极结构。这一进步通过直接离子注入实现了栅极与源漏区域的对准,显著降低了寄生电容。随后,轻掺杂漏极工艺和自对准硅化物技术等自对准工艺被引入。通过自对准工艺制造2DSM FETs,可以克服介电层和转移的挑战,同时保留上述优势,从而进一步缩小沟道长度。然而,传统的硅基技术,包括离子注入和选择性干法刻蚀,在应用于2DSM固有的原子级薄厚度时存在局限性,这使得其在制造2DSM自对准TG-FETs时变得复杂。最近,针对2DSM FETs的几种新型自对准工艺已出现。一种有前景的方法是使用纳米线作为TG硬掩模,以促进源漏金属的自对准沉积,其中纳米线的宽度定义了沟道长度。然而,纳米线生长的不一致排列和尺寸对满足大规模集成的要求构成了重大挑战。此外,利用Al顶栅自氧化形成的硬掩模开发了自对准FETs。然而,这一自氧化过程对温度和环境因素敏感,可能会影响器件的一致性。此外,用作电荷捕获层的氧化物包覆Al通常会导致显著的滞后效应。尽管通过剥离和转移等替代方法成功制造了性能优异的2DSM自对准TG-FETs,但这些工艺在兼容性和可扩展性方面面临重大挑战。

【成果介绍】

鉴于此,复旦大学包文中研究员,绍芯实验室的谭小军和王印合作发表了题为“Development of Self-Aligned Top-Gate Transistor Arrays on Wafer-Scale Two-Dimensional Semiconductor”的工作在Advanced Science期刊上。该工作提出了一种基于化学气相沉积(CVD)生长单层MoS

2

的顶栅场效应晶体管(TG-FETs)新型自对准工艺。该创新方法利用顶栅金属作为硬掩模,并通过湿法/干法混合刻蚀技术对介电层进行处理,从而实现源漏金属的自对准沉积。这一方法展现了优异的兼容性,并促进了大规模集成制造。通过退火和封装等后工艺优化,降低了接触电阻并减少了缺陷,显著提升了器件的电学性能和稳定性。对制备和优化后的自对准MoS

2

TG-FETs阵列的对比分析表明,其开态电流、开关比(I

on

/I

off

)显著提高,同时亚阈值摆幅(SS)和滞后窗口显著减小。通过进一步缩小栅极长度(L

g

),成功制备了沟道长度为200 nm的自对准MoS

2

TG-FETs,其最大输出电流达到465.6 µA µm

−1

,开关比高达10

8

。此外,基于自对准MoS

2

TG-FETs成功制备了反相器、与非门(NAND)和或非门(NOR)逻辑门,展现了其在先进电子电路中进一步小型化和应用的潜力。

【图文导读】

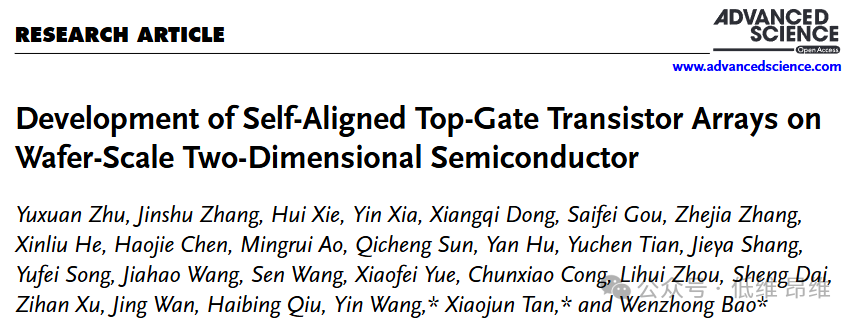

图 1. 自对准MoS

2

TG-FETs的制备与结构。a) 自对准MoS

2

TG-FETs制备工艺的示意图。b) 自对准MoS

2

TG-FETs的结构示意图。c) 自对准MoS

2

TG-FETs阵列的光学图像。d) 自对准MoS

2

TG-FETs接触区域和栅极区域的STEM和EDS图像。

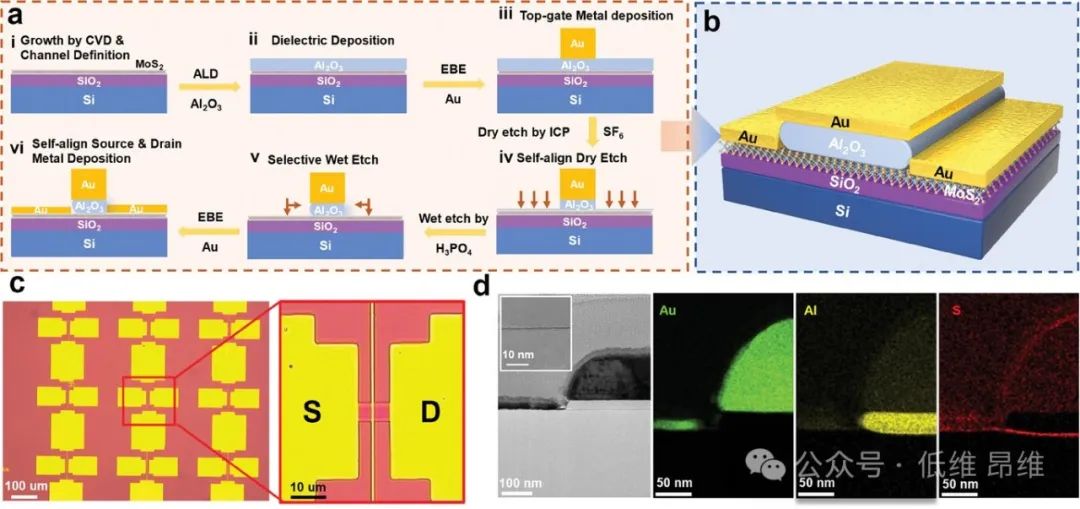

图 2. 制备与优化后的自对准MoS

2

TG-FET的示意图及电学性能。a) 自对准MoS

2

TG-FET制备工艺的示意图。制备后、退火后以及封装后MoS

2

TG-FET的b) 转移特性曲线。c) 栅极漏电流。d) 接触电阻。e) 优化后器件的肖特基势垒高度(SBH)提取结果。

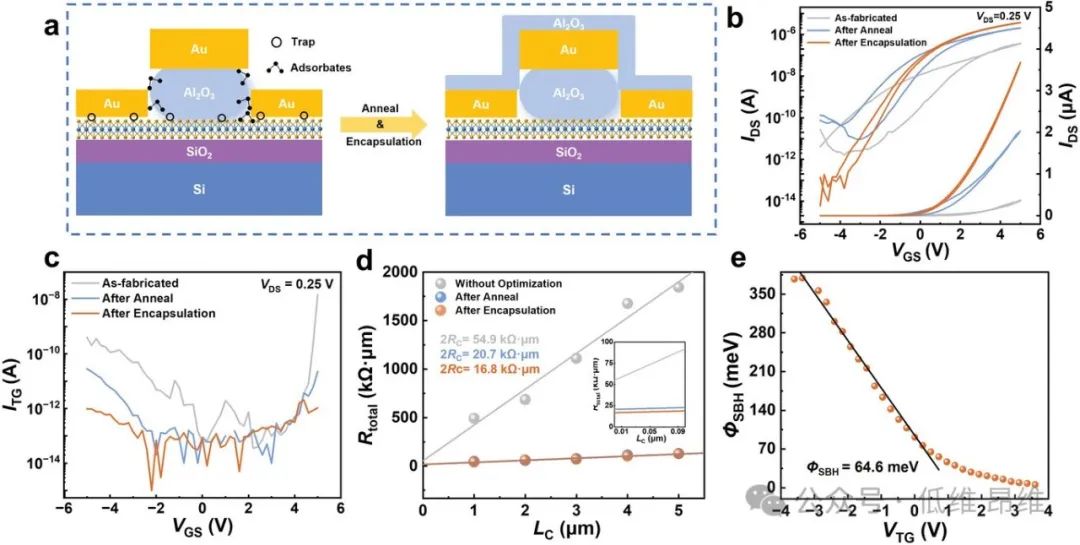

图 3. 制备与优化后的自对准MoS

2

TG-FET电学性能对比。a) 40个制备后和优化后的自对准MoS

2

TG-FET的转移曲线。b) 优化后的自对准MoS

2

TG-FET的输出曲线。c) 开态电流(I

on

)、d) 开关比(I

on

/I

off

)、e) 滞后窗口、f) 亚阈值摆幅(SS)和g) 阈值电压(V

th

)的统计分布。

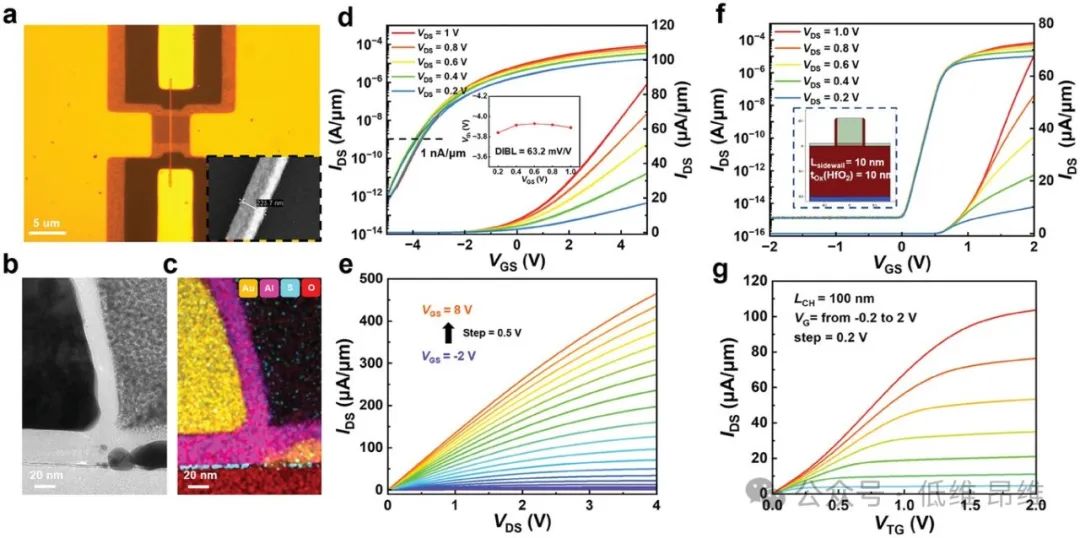

图 4. 具有亚微米沟道长度的优化自对准MoS

2

TG-FET的结构与电学性能。a) 沟道长度约为200 nm的自对准MoS

2

TG-FET的光学图像及SEM插图。b) 优化后沟道长度约为200 nm的自对准MoS

2